IEEE1149.1 学习笔记

[^1]本文仅用于自己学习笔记记录

TAP 是一组通用端口,能够对基于此协议定义的测试逻辑提供对元器件的测试功能支持。

最小组成:三输入(TCK,TMS,TDI)一输出(TDO)

可选输入端口:TRST,提供测试逻辑的异步复位

当测试逻辑能够在上电后建立Test-Logic_Reset状态或片上POR电路存在时,TRST并不是必需;否则,当上电后没有外部控制操作的情况下,TAP controller 状态无法确定,需要TRST 输入来完成初始状态的确定

所有TAP端口应为dedicated,不可与其他端口复用

TCK:提供测试逻辑时钟信号

当TCK为0时,测试逻辑中包含的stored-state devices(还不会翻译)应永久保持当时状态,即高有效(也可设计成低有效的时钟TAP结构);因为TCK对于大多数设计来说,是单driver控制,因此其load应尽可能小

特定TCK端口作用:

(1)通常情况下,component 特定的系统时钟之间频率不同,而特定TCK端口能独立于系统时钟,完成components 之间串行测试数据的传送

(2)实现同一component上与普通系统操作同时完成测试数据传送(需支持TAP的使用以及设计中TDR的存在)

(3)在不改变芯片系统逻辑的同时完成测试数据的传输

(4)支持boundary scan register 用于板级互连测试

大多数情况下,TCK是占空比50% free-running的时钟信号。某些情况下,需要TCK 停下来。例如,当ATE需要从backup memory中拿出测试数据时,某些测试系统不能同时保持时钟running,所以需要TCK置于0 态以免影响测试逻辑状态。当TCK=0,store-state devices 保留状态,当时钟信号继续工作,测试逻辑能在当前状态基础上继续工作。

测试逻辑的大部分是依赖于TCK的上升沿或下降沿工作的,应在TCK沿发生相应改变后的固定延时时间内完成,且这种延时是被component supplier 定义的。

TMS:Test mode select ,input (TCK 上升沿采样,TMS的值决定TAP controller的下一状态)

The design of the circuitry fed from TMS shall be such that an undriven input produces a logical response identical to the application of a logic 1

(怎么理解呢?)

满足这一点(英文说的),能够保证当TMS不受外源控制时,TAP controller 以最快速度进入Test-Logic-Reset 状态。例如,当未与板相连的test controller 或新组装印刷电路板上存在开路时,满足这一点能够帮助整个设计继续正常工作,不受测试逻辑的干扰。对于TTL或CMOS设计电路,可以通过在TMS输入电路处添加上拉电阻来满足此规则。

TCK上升沿,TMS 值被采样。一般,总线主控器(bus master),如ATE/bus controller等在TCK下降沿采TMS值。

因为大多数component TMS 端口是单driver 控制,所以load 应尽可能小

TDI: test data input ,接受串行测试指令及数据,TCK上升沿采样(在串行板级通路间第一个component的 bus master 如ATE,bus controller 在TCK下降沿采样TDI)

The design of the circuitry fed from TDI shall be such that an undriven input produces a logical response identical to the application of a logic 1

板级串行测试数据同路的开路故障会向测试逻辑中输入固定的逻辑值。当这个常值输入到指令寄存器后,会选择bypass register。对于TTL和CMOS设计电路来说,可以在TDI输入电路处添加上拉电阻满足此规则。

当测试数据从TDI向TDO传送,TDI接收的测试数据经过一系列TCK上升/下降沿后(由指令长度或所选TDR决定),在TDO不出现反转,以来简化印刷电路板上与此协议兼容的components操作

TDI和TDO作为数据端口,为电路提供测试数据的传输。

TDO:Test data output,从测试逻辑中输出串行测试指令和数据,TCK下降沿或TRST下降沿采样

若不处于传输数据状态,TDO driver 应处于inactive drive 状态。(有效态是high 1 , low 0, undrivern Z)

为了保证没有竞争,测试逻辑的TMS 值在TCK上升沿采样,而TDO在下降沿采样。同理,对于从系统端口drive或接收信号的测试逻辑,测试逻辑状态改变从component 输出的在TCK下降沿采样,进入测试逻辑的TCK上升沿采样

TDO必须能在active 与 inactive drive 间的切换,保证板级测试数据的并行连接而不是串行。对于TTL或CMOS设计电路,可食用三态输出buffer 来满足此规则

TRST:Test reset input (optional)

在上电时提供TAP controller,TMP controller及其他测试逻辑的异步复位。它比简单的使TAP controller状态机移到Test-Logic-Reset状态影响更大。当上电后无法处于一种已知可控的状态,或没有片上上电复位逻辑(POR)时,需要TRST端口。

若TAP中包含TRST,TRST=0时,TAP controller 和TMP controller 应被异步复位到Test-Logic_reset 态和Presistence-Off 态

对于undriven 的TRST 输入端口,应等同于向测试逻辑中灌入逻辑1 激励。此规则能够保证当TRST无法确定输入值时,测试逻辑可通过操作TMS,TCK继续工作。对于TTL或CMOS电路,可在TRST输入电路处加上拉电阻实现

TRST 不能用于复位component 中任何系统逻辑,以便测试逻辑能独立于片上系统逻辑完成复位及解复位

为了保证测试系统的操作确定性,当TRST从0变为1时,TMS应为1。若TCK和TRST同时出现上升沿,而TMS处于逻辑0时,会出现竞争,TAP controller 可能会处于Test-Logic-State态,也可能处于Run-Test/Idle态

TAP controller的复位反过来会使其他测试逻辑产生复位动作

板级间components的互连

在封装产品上可能存在板级的TAP 输入输出端口互连关系

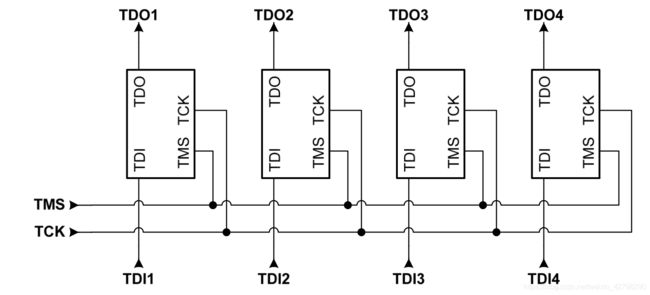

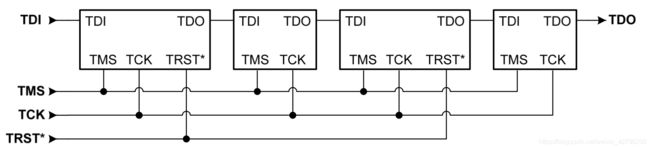

如图1-4 展示了四种可选的板级components互连关系。每个例子中,测试总线可以由ATE控制,也可以在下一个产品组装级别提供测试总线的端口(如板/背板接口)。在该标准中,控制板级测试总线的设备称为总线主控器。

图1的TMS/TCK信号是有可测试的bus master 并行提供到所有slave master;TDI与TDO的串行数据连接关系是daisy-chain connection

图2使用两个TMS信号完成串行/并行连接的混合,来实现指定时间内只在一个串行通路中传输数据。这个配置利用了TDO输出端口的三态特性,即只有当TDO端口处于active drive 状态,components才会传输数据

图3展示了四个components在整板上存在四个单独的串行数据通路,有单独的TDI/TDO端口信号,但是可被同一TCK/TMS控制

当在板级选择components的互连关系时,有必要考虑测试设备的兼容性和测试向量的产生。更期望任何的测试设备或测试向量能够通过图1的板级配置,实现支持基于此协议定义的boundary scan 架构的测试方法,因为图1配置的简并模式是一个单一component。另一方面,一些测试设备或测试向量可能无法

通过图2或图3的结构完成板级配置的测试

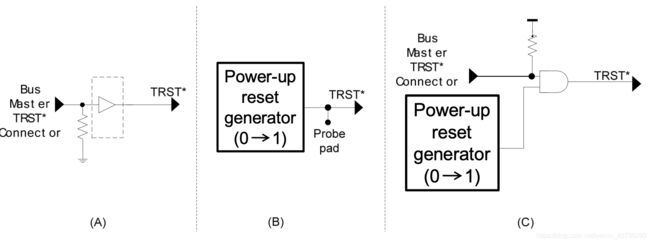

图4展示了TRST 端口存在时的板级互连结构。TRST进一步连到三个可替代之一如图5

图5(A)电阻接地实现。虚框里为可选buffer,可用来时TRST可靠置0 以及消除通过IC接收器中的上拉电阻和板上的下拉电阻器的任何电流路径。

图5(B)不支持TRST *上的外部总线主控器连接,但应为ATE提供板上的访问点(shown by the stub on the TRST net)。 显示了一个接触pad。

图5(c)展示了板上上电复位发生器和测试bus master 的组合。

图5(b)和(c) 展示了在低功耗环境中支持TRST的方法。上电复位发生器是没有TAP的电路,能够保持其输出为低电平,直到电源稳定为止,然后将其输出驱动为逻辑高电平。

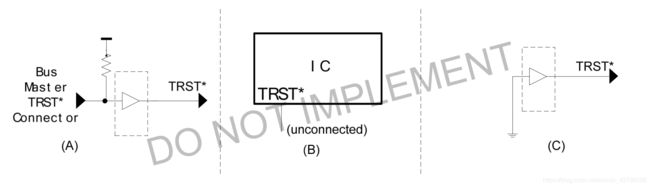

不要把TRST tie 到 上拉电阻或把上拉电阻镰刀TRST 的input driver buffer 上,如图6(A)所示。不要使TRST 未连接,如图6(B)。这两种情况没有办法使TRST 为0,因此存在测试逻辑干扰一般系统操作的可能。

不要把TRST 或TRST 的 driver buffer 接地,如图6(C)所示。这种情况下,测试逻辑一直处于reset 状态。

基于此协议的更高级别测试方法的拓展 (NA)