HDMI 1.4 协议详解

HDMI系统架构定义为由源和接收器组成。给定的设备可能具有一个或多个HDMI输入和一个或多个HDMI输出。这些设备上的每个HDMI输入都应遵循HDMI接收器的所有规则,每个HDMI输出应遵循HDMI源的所有规则。

如图3-1所示,HDMI电缆和连接器带有四个差分对,它们构成了TMDS数据和时钟通道。这些通道用于传输视频,音频和辅助数据。另外,HDMI带有VESA DDC通道。DDC用于单个源和单个接收器之间的配置和状态交换。可选的CEC协议可在用户环境中的所有各种视听产品之间提供高级控制功能。

可选的HDMI以太网和音频回传通道(HEAC)在连接的设备和音频回传通道之间以与TMDS相反的方向提供以太网兼容的数据网络。

音频,视频和辅助数据通过三个TMDS数据通道传输。通常以视频像素速率运行的TMDS时钟在TMDS时钟通道上传输,并且被接收机用作三个TMDS数据通道上数据恢复的频率参考。

在源头,TMDS编码将每个TMDS数据通道的8位转换为10位DC平衡的,最小化转换的序列,然后以每TMDS时钟周期10位的速率跨线对串行传输。

视频数据的像素大小可以为24、30、36或48位。默认的24位色深的视频以等于像素时钟速率的TMDS时钟速率传输。使用相应较高的TMDS时钟速率传输较高的色深。TMDS速率低于25MHz的视频格式(例如 可以使用像素重复方案传输480i / NTSC的13.5MHz。视频像素可以RGB,YCBCR 4:4:4或YCBCR 4:2:2格式编码。

为了跨TMDS通道传输音频和辅助数据,HDMI使用数据包结构。为了获得音频和控制数据的更高可靠性,此数据使用BCH纠错码进行保护,并使用特殊的纠错编码进行编码,以生成要发送的10位字。

基本音频功能包括单个IEC 60958 L-PCM音频流,采样率为32kHz,44.1kHz或48kHz。这可以容纳任何正常的立体声流。HDMI可以选择以高达192KHz的采样率和3至8个音频通道传输此类音频。HDMI还可以以高达24.576Mbps的比特率传输IEC 61937压缩(例如环绕声)音频流。

HDMI还可以传输2到8通道的一位音频和压缩格式的一位音频,称为DST。

源使用DDC读取接收器的增强型扩展显示标识数据(E-EDID),以发现接收器的配置和/或功能。

Utility Line用于扩展的可选功能,例如补编2中指定的HEAC。

物理

设备的外部HDMI连接应通过五个指定的HDMI连接器之一(类型A,类型B,类型C,类型D或类型E)进行显示。此连接器可以直接连接到设备,也可以通过电缆适配器连接。

随设备一起提供。

所有五个连接器都承载所有必需的HDMI信号,包括TMDS链接。

B型连接器稍大一些,并带有第二条TMDS链接,这对于使用双链接支持非常高分辨率的显示器是必需的。

C型连接器承载与A型相同的信号,但结构更紧凑,适用于移动应用。

D型连接器承载与A型相同的信号,但比C型更为紧凑。E型连接器承载与A型相同的信号,适用于汽车应用。

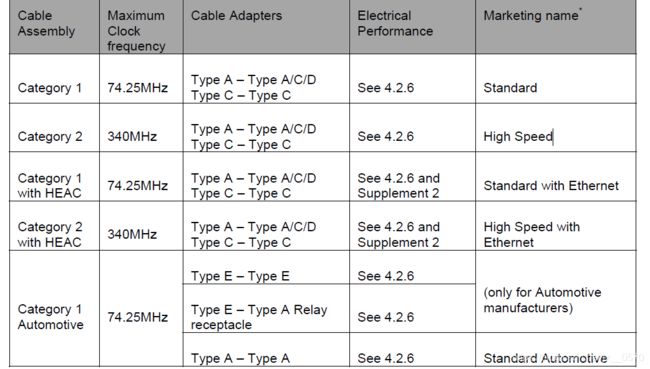

根据支持的时钟频率,电缆分为两类。

除汽车应用外,在满足附录2中的其他电缆规范后,此处指定的两种电缆都可以支持HEAC应用。

为了支持大于165Mpixels / sec的DVI信号,必须使用B型连接器的双链路功能。为了支持小于或等于165Mpixels / sec的DVI信号,应使用单链路操作。

为了支持高速HDMI信号,可以使用B型连接器的双链路功能。HDMI的单链路到双链路交叉频率将在将来的规范中定义,并且将大于340Mpixels / sec。双链路不能用于低于该交叉频率的格式。

A型为19Pin,HDMI B型为29Pin,HDMI C型为19Pin(俗称MINI HDMI),HDMI D型为19Pin(Micro HDMI)。HDMI接口分公头(plug)和母头(socket)。

HDMI 物理接口序号

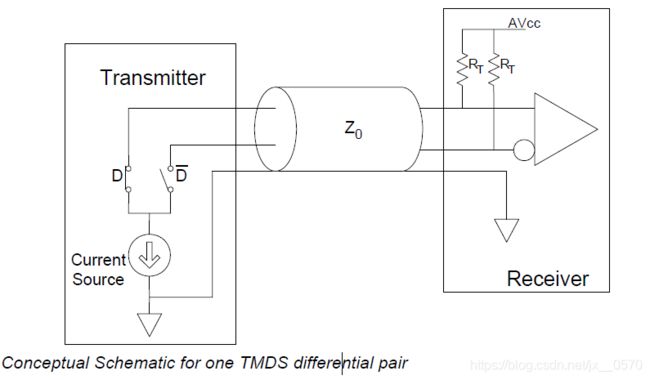

一个TMDS差分对的概念图如图4-22所示。TMDS技术使用电流驱动在直流耦合传输线的Sink端产生低压差分信号。链路参考电压AVcc设置差分信号的高电压电平,而低电压电平则由HDMI源的电流源和接收器处的终端电阻确定。终端电阻(RT)和电缆的特性阻抗(Z0)必须匹配。

单端差分信号表示差分对的正端或负端,如图4-23所示。信号的标称高电平电压为AVcc,信号的标称低电平电压为(AVcc-Vswing)。由于摆幅在线对上是差分的,所以线对上的净信号的摆幅是单端信号的两倍,即2Vswing。

如图4-24所示,差分信号在正Vswing和负Vswing之间摆动。

所有TMDS时钟和数据信号抖动规范都是相对于以下定义的理想恢复时钟指定的。数据抖动不是用数字指定的,而是当使用理想恢复时钟作为触发源测量TMDS数据信号时,HDMI设备或电缆应遵守适当的眼图。

TMDS时钟信号可能包含低频抖动分量(通常由Sink的时钟恢复电路跟踪)和高频分量(通常不会跟踪)。

理想恢复时钟的目的是当用作眼图和时钟抖动规范的触发器时,能够准确表示链路性能。时钟抖动与数据抖动的关系仅由眼罩间接指定。

出于抖动和眼图规范的目的,相对于TMDS时钟信号定义了理想恢复时钟。当将TMDS时钟信号输入到PLL时,理想恢复时钟应等效于具有抖动传递函数的理想PLL(理想时钟恢复单元)所产生的信号,如公式4-1所示。该抖动传递函数具有低通滤波器的特性,具有20dB /十倍频滚和–3dB点为4MHz。

为了进行合规性测试,时钟恢复单元用于生成恢复时钟,该时钟近似于理想恢复时钟。该恢复时钟用于测量抖动和眼图。

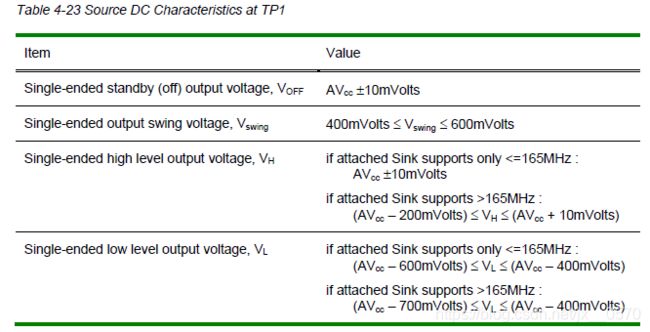

4.2.4 HDMI源TMDS特性HDMI需要直流耦合的TMDS链路。电源测试应使用图4-29所示的测试负载进行,AVcc设置为3.3V。TP1代表插座的连接点。

将表4-23中指定的单端摆幅电压(Vswing)与15%的过冲(传统)和表4-24的下冲限制相结合,可以计算最小和最大高电平电压(Vhigh)以及接口上允许的低电平电压(Vlow)。

在驱动时钟和数据信号时,对于表4-22中指定的所有工作条件,该源应满足表4-23中的DC规范。Vswing参数是在振铃消退后,单端最常见的高电平电压(将通过直方图测量显示)与最常见的低电平电压之间的差。

建议具有更高速度的信号源结合有效量的信号源端接,尤其是在使用C型连接器的情况下。此端接通常会降低每个单端信号的平均DC电平。放宽的VH和VL参数允许这种实现。

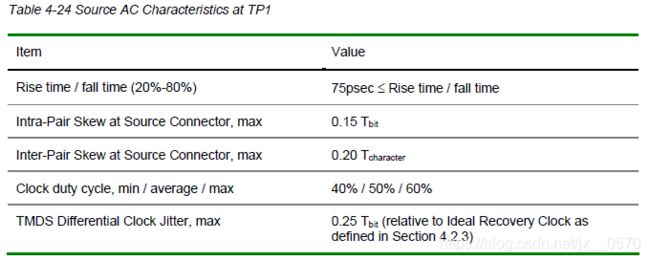

在表4-22中指定的所有工作条件下,电源应符合表4-24中的AC规范。上升和下降时间定义为被测器件标称摆幅电压(Vswing)的20%至80%之间的信号转换时间。

源对对内时滞是在给定差分对的真实信号和互补信号之间在TP1处测得的最大允许时间差(从低到高和从高到低的转换)。在真实信号和互补信号的单端信号摆幅的中点测量该时间差。源对之间的时滞是在TP1上测得的任何两个不构成差分对的单端数据信号之间的最大允许时间差(在从低到高和从高到低的转换上)。

电源的设计应考虑到电缆组件和接收器的100欧姆差分阻抗(请参阅表4-29)。

对于在表4-22中规定的所有工作条件下且如图4-29所示终止时的所有通道,信号源的TP1输出电平应满足图4-30的眼图要求。该要求指定了最小的眼图张开以及绝对的最大和最小电压。时间轴被归一化为工作频率下的位时间。

当差分信号具有最小摆幅(800mV)时,绝对幅度限制在图4-30中允许最大下冲25%(平均差分摆幅电压),而对于更高的摆幅则具有更大的下冲。过冲限制仅由归一化眼图上方和下方所示的±780mV的绝对最大/最小电压施加。

将表4-23中指定的单端摆幅电压(Vswing)与15%的过冲(传统)和表4-24的下冲限制相结合,可以计算最小和最大高电平电压(Vhigh)以及接口上允许的低电平电压(Vlow)。

请注意,这些极端情况的组合并不构成唯一有效的眼睛。

源眼图测试程序在HDMI一致性测试规范中定义。

4.2.5 HDMI接收器TMDS特性HDMI接收器电气测试应使用测试信号发生器执行,如图4-31所示。

如果在上电或其他电源转换期间,接收器在任何TMDS线上断言过高或过低的电压(例如,超出DVI 1.0规范中的最大额定值),则可能存在电源损坏的风险。

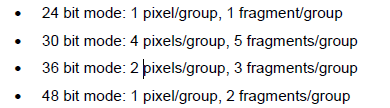

接收器应满足表4-25,表4-26和表4-27中列出的信号要求。 在TMDS时钟频率高于165MHz的情况下,应用参考电缆均衡器后,如果接收到符合图4-32眼图的任何信号,则接收器应以10-9或更高的TMDS字符错误率恢复每个通道上的数据。。

在TMDS时钟频率高于165MHz的情况下,应用参考电缆均衡器后,如果接收到符合图4-32眼图的任何信号,则接收器应以10-9或更高的TMDS字符错误率恢复每个通道上的数据。。

4.2.7 + 5V电源信号HDMI连接器提供了一个引脚,可让信号源为电缆和接收器提供+5.0 V的电压。

每当HDMI源使用DDC或TMDS信号时,所有HDMI源均应断言+ 5V电源信号。源驱动的电压应在表4-34中为TP1电压指定的限制内。HDMI源应具有不超过0.5A的+ 5V电源信号过流保护。

所有HDMI源均应能够向+ 5V电源引脚提供至少55 mA的电流。

接收器从+ 5V电源引脚汲取的电流不得超过50 mA。接收器通电后,从+ 5V电源信号中汲取的电流不得超过10mA。接收器应假定在表4-34中为TP2电压指定的范围内的任何电压都表明已连接一个源并将电源施加到+ 5V电源信号。

即使将电缆组件连接到提供不超过55mA的电源,电缆组件也应能够至少向+ 5V电源引脚提供50mA的电流。

+ 5V电源信号的返回是DDC / CEC接地信号。

4.2.8 DDC显示数据通道(DDC)I / O和电线(SDA,SCL,DDC / CEC地线)应满足I2C总线规范版本2.1第15节“标准模式”中指定的要求。

设备。

请注意,I2C总线规范第17.2节“快速模式I2C总线的开关上拉电路”中有关高电容环境的讨论也可以应用于HDMI环境。

HDMI设备应具有符合表4-35,表4-36和表4-37中所示值的DDC电气特性。

确切的方法和测量步骤写在HDMI一致性测试规范中。

在某些情况下,只要满足所有I2C时序要求,就可以在电缆中插入缓冲器或I2C“加速器”。

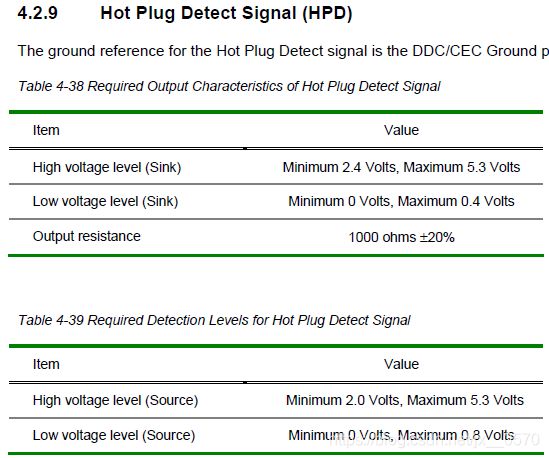

请注意,许多接收器设备只是通过1000欧姆电阻将HPD信号连接到+ 5V电源信号。

请注意,许多接收器设备只是通过1000欧姆电阻将HPD信号连接到+ 5V电源信号。

因此,对于信源,可能有必要下拉HPD信号,以便可靠地区分浮动(断开)的HPD和高电压电平的HPD信号。

4.2.10 CEC线路所有产品(包括未实施CEC协议的产品)均需要以下线路特性。

附录1中提供了对那些实现CEC协议的设备的进一步要求。CEC信号的接地参考是DDC / CEC接地信号。

信号和编码

图5-1所示,一条HDMI链路包括三个TMDS数据通道和一个TMDS时钟通道。TMDS时钟通道始终以与传输视频的像素速率成比例的速率运行。在TMDS时钟通道的每个周期内,三个TMDS数据通道中的每一个都发送一个10位字符。使用几种不同的编码技术之一对该10位字进行编码。

源编码逻辑的输入流将包含视频像素,数据包和控制数据。

分组数据包括音频和辅助数据以及相关的纠错码。

这些数据项以多种方式处理,并以每个TMDS通道2位控制数据,4位分组数据或8位视频数据的形式呈现给TMDS编码器。源在任何给定的时钟周期内对这些数据类型之一进行编码或对保护带字符进行编码

5.1.2操作模式概述HDMI链接以以下三种模式之一进行操作:视频数据周期,数据岛周期和控制周期。在视频数据周期期间,传输活动视频线的活动像素。

在“数据岛”期间,使用一系列数据包传输音频和辅助数据。

当不需要传输视频,音频或辅助数据时,将使用控制周期。非控制期间的任何两个期间之间都需要一个控制期间。

下图显示了每个期间的放置示例。

视频数据周期使用最小化过渡的编码来编码每个通道8位,或每个像素总共24位。数据岛周期使用类似的最小化转换编码TMDS减少错误编码(TERC4)进行编码,该编码每通道传输4位,或每个TMDS时钟周期总共传输12位。

在控制周期内,每个TMDS时钟使用过渡最大化编码对每个通道2位或总共6位进行编码。这6位是HSYNC,VSYNC,CTL0,CTL1,CTL2和CTL3。

在每个控制周期即将结束时,使用CTLx位的前同步码指示下一个数据周期是视频数据周期还是数据岛周期。

每个视频数据周期和数据岛周期都从前导保护带开始,该保护带设计用于确定从控制周期到数据周期的过渡。该领导警戒带由两个特殊字符组成。

数据岛时间段也受尾随保护带的保护,该保护带旨在为过渡到控制时间段提供可靠的确定。

下表显示了每种操作模式下使用的编码类型和传输的数据。

5.2工作模式5.2.1控制周期控制周期用于传输前同步码。接收器还将控制周期用于字符同步。

HDCP指定的增强加密状态信令ENC_EN代码(CTL0:3 = 1001)不得用作HDCP指定的机会窗口期间的正确ENC_EN。5.2.1.1前导码每个视频数据周期或数据岛周期之前紧接的是前导码。这是八个相同的控制字符的序列,用于指示即将到来的数据周期是视频数据周期还是数据岛。CTL0,CTL1,CTL2和CTL3的值指示随后的数据周期的类型。其余控制信号HSYNC和VSYNC在此序列中可能会有所不同。

“视频数据周期”类型指示以下数据周期包含从视频保护带开始的视频数据。

数据岛类型表示从数据岛保护带开始,以下数据周期是符合HDMI的数据岛。

按照此顺序从TMDS控制字符到保护带字符的过渡标识了数据周期的开始。

除非在前同步码期间正确使用,否则不得传输数据岛前同步码控制代码(CTL0:3 = 1010)。

5.2.1.2字符同步TMDS接收器需要确定串行数据流中字符边界的位置。

一旦在所有数据通道上建立了字符边界,就将接收器定义为与串行流同步,并且可以从数据通道中恢复TMDS字符以进行解码。TMDS数据流为解码器同步提供周期性提示。

在视频数据周期和数据岛周期中使用的TMDS字符包含五个或更少的过渡,而在控制周期中使用的TMDS字符包含七个或更多的过渡。在控制周期内传输的字符的高转换内容构成了解码器处字符边界同步的基础。尽管这些字符在串行数据流中不是唯一的,但是它们足够相似,以至于解码器可以在传输的同步间隔内唯一地检测到它们的连续性。此检测的确切算法是实现细节,超出了本文档的范围,但是定义了接收器同步的最低条件。

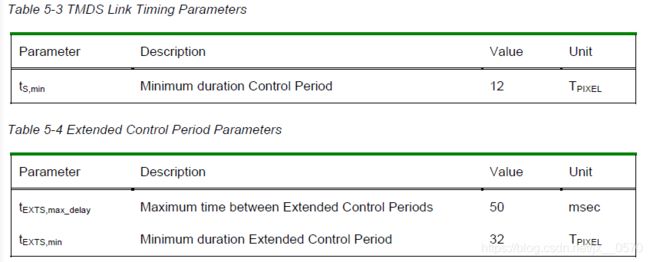

要求接收器在任何长度大于或等于tS,min(12)个字符的控制周期内与数据流建立同步。

还要求源偶尔根据表5-4发送扩展的控制周期。

5.2.2视频数据周期视频数据周期用于承载活动视频线的像素。

每个视频数据周期之前都有上述的前同步码。

在序言之后,视频数据周期以两个字符的视频领先保护带开始。

视频数据期间没有尾随保护带。

在有效视频周期内,在每个TMDS时钟周期内使用TMDS转换最小化编码对24位像素数据进行编码。

5.2.2.1视频保护带表

5-5视频主要保护带值情况(TMDS通道号):

0:q_out [9:0] = 0b1011001100;

1:q_out [9:0] = 0b0100110011;

2:q_out [9:0] = 0b1011001100; endcase

5.2.3数据岛时段

5.2.3.1数据岛概述数据岛用于承载音频样本数据和辅助数据的数据包。

此辅助数据包括InfoFrame和描述活动音频或视频流或描述Source的其他数据。

每个数据岛前面都有一个前导,如上所述。

在序言之后,每个岛屿都以领队为首。

然后是数据岛的第一个数据包。

在数据岛的每个TMDS时钟周期(包括保护带)中,TMDS通道0的位0和1传输HSYNC和VSYNC的编码形式。

TMDS通道0的位2用于发送数据包头。

TMDS通道1和2的所有四个位都用于数据包数据,如图5-3所示。

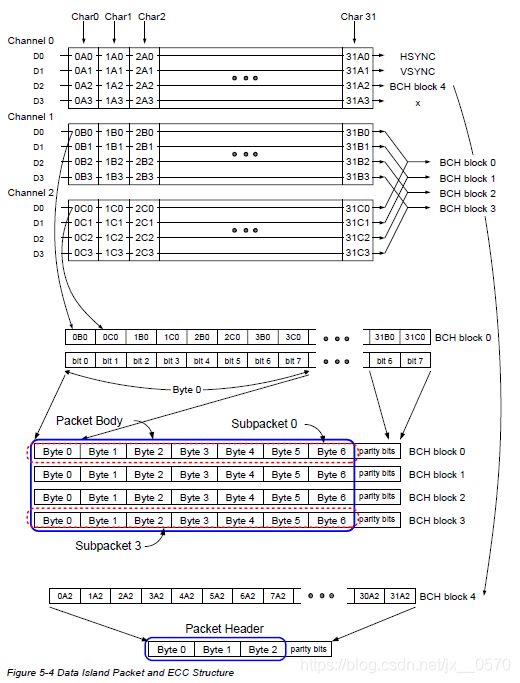

每个数据包的长度为32个像素,并受BCH ECC保护,以进行纠错和检测。

在数据岛期间,三个TMDS通道中的每个通道都使用TMDS减少错误编码(TERC4)传输从4位输入字编码的一系列10位字符。

TERC4通过仅选择具有高固有错误避免能力的10位代码来显着降低链路的错误率。

在最后一个数据包之后,数据岛的最后两个字符是尾随保护带。

数据岛保护带5.2.3.2岛的放置和持续时间要求信号源确定相对于视频信号的水平和垂直消隐周期以及同步信号的数据岛的时间放置和持续时间。

它应遵守以下规定。

所有TMDS控制周期应至少长tS,min(12)个字符(像素)。

数据岛应至少包含一个数据包,并将其最小大小限制为36个像素。

离岛应包含整数个数据包。

为了确保数据岛内数据的可靠性,应将其限制为18个数据包或更少。

在随后的视频数据周期之间可能会出现零个,一个或多个数据岛。

在传输视频时,应在每两个视频场之间传输至少一个数据岛。

5.2.3.3数据岛保护带数据岛内的前两个数据字符是前导保护带。

数据岛中的最后两个数据字符是后卫保护带。

在数据岛保护带期间,通道0被编码为四个TERC4值之一。

根据HSYNC和VSYNC的值,这些TERC4值(D [3:0])为0xC,0xD,0xE和0xF。

表5-6数据岛前导和尾随保护带值的情况(TMDS通道号):

0:q_out [9:0] = n.a .;

1:q_out [9:0] = 0b0100110011;

2:q_out [9:0] = 0b0100110011; endcase

5.2.3.4数据岛包构造数据岛内的所有数据都包含在32个时钟包中。

数据包包括一个数据包头,一个数据包主体(由四个子数据包组成)和相关的纠错位。

每个子分组包括56位数据,并由另外8位BCH ECC奇偶校验位保护。

子数据包0及其对应的奇偶校验位构成BCH块0。此块被映射到通道1和通道2的位0。这样,BCH块0的64位在32个像素的过程中传输。

同样,BCH块1(子数据包1和奇偶校验)被映射到通道1和2的位1。

在下表中,标头字节表示为HB0,HB1和HB2,子数据包字节表示为SB0至SB6。

子数据包0字节0到6(SB0-SB6)也被指定为数据包字节0到6(PB0-PB6)。

子数据包1字节0到6(SB0-SB6)也被指定为数据包字节7到13(PB7-PB13)。

子数据包2字节0到6(SB0-SB6)也被指定为数据包字节14到20(PB14-PB20)。

子数据包3字节0到6(SB0-SB6)也被指定为数据包字节21到27(PB21-PB27)。

如图5-4所示。

视频编码

5.4.4视频数据编码

5.4.4.1视频数据编码以下是在视频数据传输期间使用的编码算法的说明。

给出了编码器的详细描述。

其他实现也是可能的,并且被允许,但是给定相同的输入字符序列,要求它们产生与所描述的编码器生成的相同的输出(10位)字符序列。

在视频数据中,每个10位字符代表8位像素数据,编码后的字符可提供近似的DC平衡以及数据流中过渡次数的减少。

活动数据周期的编码过程可以分为两个阶段。

第一级从输入的8位中产生最小转换的9位代码字。

第二阶段产生一个10位代码字,即完成的TMDS字符,它将管理所传输字符流的总体DC平衡。

编码器第一级产生的9位代码字由输入8位中出现的转换的8位表示以及一个位标志(表示使用两种方法中的哪一种来描述)构成。

过渡。

在这两种情况下,输出的LSb与输入的LSb匹配。

建立起始值后,输出字的其余7位从输入的每个位与先前导出的位的顺序异或(XOR)或异或(XNOR)函数得出。

在XOR和XNOR逻辑之间进行选择,以使编码的值包含最少的可能转换,并且码字的第9位用于指示是使用XOR还是XNOR函数导出输出码字。

对该9位代码字的解码仅是对代码的相邻位应用XOR或XNOR门的问题,而从解码器输入到解码器输出的LSb不变。

编码器的第二级通过选择性地反转由第一级产生的9位代码字的8个数据位,对传输的流执行近似的DC平衡。

将第十位添加到代码字,以指示何时进行了反转。

编码器根据在传输流中跟踪的一和零之间的运行差异以及在当前代码字中找到的一和零的数量,确定何时反转下一个字符。

如果传输的比特过多,并且输入中的比特大于零,那么代码字将被反转。

通过基于TMDS字符的第十位对输入代码字进行条件反转,可以简单地在信宿处对源处的这种动态编码决策进行解码。

图5-7用表5-35的定义指定了TMDS代码映射。

编码器产生460个唯一的10位字符之一。

在视频数据周期内,编码器不得生成任何其他10位字符。

进入视频数据周期后,编码器应将数据流视差(cnt)视为零。

视频部分

6视频

6.1概述

HDMI允许传输和显示任何视频格式时序。

为了使产品之间的互操作性最大化,已经定义了常见的DTV格式。

这些视频格式时序定义像素和行数,时序,同步脉冲位置和持续时间,以及格式是隔行格式还是逐行格式。

HDMI还允许使用供应商特定的格式。

链路上承载的视频像素应采用以下三种不同的像素编码之一:RGB 4:4:4,YCBCR 4:4:4或YCBCR 4:2:2。

HDMI源基于源视频的特性,源上可能的格式和像素编码转换以及接收器的格式和像素编码功能以及偏好来确定所传输信号的像素编码和视频格式。

6.2视频格式支持为了在视频源和接收器之间提供最大的兼容性,已为源和接收器指定了特定的最低要求。

6.2.1格式支持要求除CEA-861-D中指定的要求以外,以下某些支持要求。

•HDMI源应至少支持以下视频格式时序之一:•640x480p @ 59.94 / 60Hz•720x480p @ 59.94 / 60Hz•720x576p @ 50Hz•HDMI Source能够使用以下任意格式传输以下任何视频格式时序 其他分量模拟或未压缩的数字视频输出,应能够通过HDMI接口传输该视频格式时序。

••1280x720p @ 59.94 / 60Hz•1920x1080i @ 59.94 / 60Hz•720x480p @ 59.94 / 60Hz•1280x720p @ 50Hz•1920x1080i @ 50Hz•720x576p @ 50Hz•接受60Hz视频格式的HDMI接收器应支持640x480p @ 59.94 / 60Hz和720x480 59.94 / 60Hz视频格式时序。

•接受50Hz视频格式的HDMI接收器应支持640x480p @ 59.94 / 60Hz和720x576p @ 50Hz视频格式时序。

•接受60Hz视频格式并支持HDTV功能的HDMI接收器应支持1280x720p @ 59.94 / 60Hz或1920x1080i @ 59.94 / 60Hz视频格式时序。

•接受50Hz视频格式并支持HDTV功能的HDMI接收器应支持1280x720p @ 50Hz或1920x1080i @ 50Hz视频格式时序。

•能够使用任何其他分量模拟或未压缩的数字视频输入接收以下任何视频格式定时的HDMI接收器,应能够通过HDMI接口接收该格式。

•1280x720p @ 59.94 / 60Hz•1920x1080i @ 59.94 / 60Hz•1280x720p @ 50Hz•1920x1080i @ 50Hz附录F中提供了有关源和接收器处理视频格式的其他建议。

6.2.2视频控制信号:HSYNC,VSYNC在数据岛期间,HDMI使用通道0上的编码位承载HSYNC和VSYNC信号。在视频数据周期内,HDMI不承载HSYNC和VSYNC,接收器应假定这些信号仍然存在 不变。

在控制期间,HDMI通过在TMDS通道0上使用四个不同的控制字符来传输HSYNC和VSYNC信号。

6.2.3像素编码要求

HDMI上只能使用RGB 4:4:4,YCBCR 4:2:2和YCBCR 4:4:4(如6.5节中指定)的像素编码。

所有HDMI源和接收器均应能够支持RGB 4:4:4像素编码。

只要该设备能够跨任何其他分量模拟或数字视频接口传输色差色彩空间,则所有HDMI源均应支持YCBCR 4:2:2或YCBCR 4:4:4像素编码,除非需要该设备 将RGB视频转换为YCBCR,以满足此要求。

当该设备能够支持与任何其他分量模拟或数字视频输入的色差色彩空间时,所有HDMI接收器均应能够支持YCBCR 4:4:4和YCBCR 4:2:2像素编码。

如果HDMI接收器支持YCBCR 4:2:2或YCBCR 4:4:4,则两者均应受支持。

HDMI源可以通过使用E-EDID确定接收器支持的像素编码。

如果接收器指示它支持YCBCR格式的视频数据,并且源可以传递YCBCR数据,则它可以启用此数据在链路上的传输。

6.2.4颜色深度要求

HDMI源和接收器可能支持每像素24、30、36和/或48位的颜色深度。

所有HDMI源和接收器均应支持每像素24位。

每像素大于24位的色深被定义为“深色”,并且在本规范中定义了几种深色功能模式。

尽管如果HDMI源或接收器支持任何深色模式,则所有深色模式都是可选的,但它应支持36位模式。

对于每种受支持的深色模式,应支持RGB 4:4:4,还可以选择支持YCBCR 4:4:4。

YCBCR 4:2:2也是36位模式,但不需要进一步使用6.5.2和6.5.3节中所述的深色模式。

HDMI接收器应在所有EDID指示的视频格式上支持所有EDID指示的深色模式,除非该组合超过Max_TMDS_Clock指示。

HDMI源不得将任何深色模式发送到不表明对该模式支持的接收器。

6.3视频格式时序规范

在传输指定的视频格式时序时,必须遵守所有指定的视频线像素计数和视频场线计数(有效和总计)以及HSYNC和VSYNC位置,极性和持续时间。

例如,如果某个Source正在处理每行有效像素少于所需像素的材料(即 704像素与720像素(标准清晰度MPEG2材料为720像素)相比,它可以在通过HDMI传输之前在所提供材料的左右添加像素。可能需要调整AVI条信息以解决这些增加的像素。

在CEA-861-D或CEA-861的更高版本中,可以找到以下视频格式时序的详细时序。

6.4像素重复

原始像素速率低于25 Mpixels / sec的视频格式需要像素重复,才能通过TMDS链路传输。720x480i和720x576i视频格式时序应始终重复像素。

HDMI Source通过AVI InfoFrame中的Pixel Repetition(PR0:PR3)字段指示像素重复的使用。该字段向HDMI接收器指示每个唯一像素重复发送多少次。在非重复格式中,此值为零。对于重复像素格式,此值指示接收器可以丢弃而不会丢失实际图像内容的像素数。

源应始终准确指示所使用的像素重复计数。对于HDMI接收器,像素重复字段的使用是可选的。

在CEA-861-D中更充分地描述了此像素重复计数字段的使用。

6.5像素编码和颜色深度

可以通过HDMI电缆发送三种不同的像素编码:YCBCR 4:4:4,YCBCR 4:2:2和RGB 4:4:4。无论使用哪种编码,都应符合本节中描述的方法之一。

6.5.1像素编码

图6-1显示了默认编码,即24位色深的RGB 4:4:4。给定视频行的第一像素的R,G和B分量在保护带字符之后的视频数据周期的第一像素上传输。

图6-2显示了通过HDMI传输YCBCR 4:2:2数据的信号映射和时序。

由于4:2:2数据每个像素只需要两个分量,因此每个分量分配更多的位。可用的24位分为Y分量的12位和C分量的12位。HDMI上的YCBCR 4:2:2像素编码与标准ITU-R BT.601非常相似。Y采样的高8位映射到通道1的8位,低4位映射到通道0的低4位。如果使用的位数少于12位,则有效位应左对齐(即MSb = MSb),并用零填充LSb以下的位。

在视频数据周期内发送的第一个像素包含三个分量Y0,Cb0和Cr0。

Y0和Cb0分量在第一像素周期期间被发送,而Cr0在第二像素周期期间被发送。第二个像素周期也包含第二个像素的唯一分量– Y1。这样,链路每两个像素承载一个CB样本,每两个像素承载一个Cr样本。这两个组件(CB和CR)被多路复用到链路上的相同信号路径上。

在第三像素处,重复该过程,发送第三像素的Y和CB分量,然后在下一个像素周期中,第三像素的CR分量和第四像素的Y分量被重复。

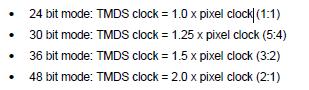

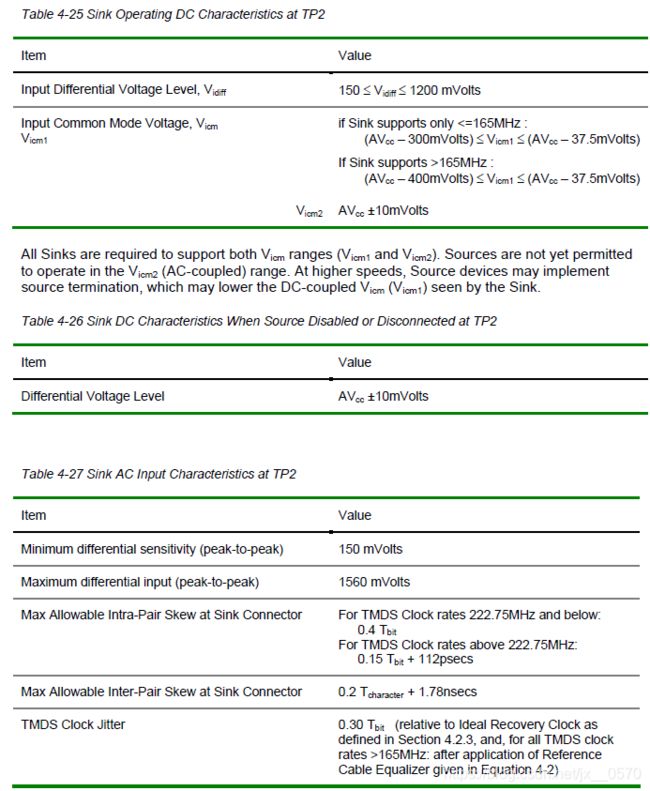

支持四种颜色像素打包模式:每个像素24位,30位,36位和48位,分别为RGB 4:4:4和YCBCR 4:4:4定义。对于24位/像素的色深,每个TMDS时钟以一个像素的速率传输像素。在较深的色彩深度下,TMDS时钟的运行速度比源像素时钟快,从而为附加位提供了额外的带宽。TMDS时钟速率按像素大小与24位的比率增加:

在深色模式下运行时,所有视频数据(像素)和信令(HSYNC,VSYNC,DE转换)都分为一系列打包的像素组,每个像素组携带相同数量的像素,并且每个都需要相同数量的TMDS时钟用于传输。在每个TMDS时钟上,传输一个像素组的一个片段。每组的像素数和每组的片段数取决于像素大小:

在活动视频期间,输入像素数据被打包到这些组中。在消隐期间,HSYNC和VSYNC被打包到这些相同的组中。这样,所有与视频相关的协议元素均以与像素时钟成正比的方式传输,从而确保像素时钟与像素数据之间的关系,DE转换以及HSYNC或VSYNC转换都不会发生变化。这还允许以24位/像素支持的任何HSYNC,VSYNC,DE转换序列等都可以在任何其他像素大小中均等地支持。

所有其他HDMI协议元素均不受深色像素包装的影响。数据岛,视频保护带和前同步码会像在正常(24位)模式下一样发生-每个前同步码是8个TMDS时钟,每个数据岛数据包是32个TMDS时钟,每个保护带是2个TMDS时钟。

如上所示,一个像素组由1个,2个或4个像素组成。每个TMDS时钟将每个像素组分为1个,2个,3个或5个像素片段。

传输流中的每个TMDS字符周期(一个TMDS时钟)都携带一个像素组的单个片段,因此代表该组的特定打包阶段。接收器有必要确定字符流中的哪个字符代表新组的开始或阶段0,以便使其像素拆包状态与源像素的拆包状态同步。为此,源发送一个指示特定像素打包阶段的数据包(有关数据包的详细信息,请参见6.5.3)。每个视频字段至少发送一次此数据包,指示当时的打包阶段。接收器使用此数据来最初确定每个新组从何处开始,还应该使用此定期更新来验证它是否仍同步或从链路上的严重错误中恢复。

下表指定了所有颜色深度的所有像素编码。对于每种模式,将描述每个阶段的包装。活动视频的打包阶段被标识为“ mPn”(10P0、10P1等),而消隐的打包阶段被标识为“ mCn”(10C0、10C1等)。

HDMI 供应商信息帧

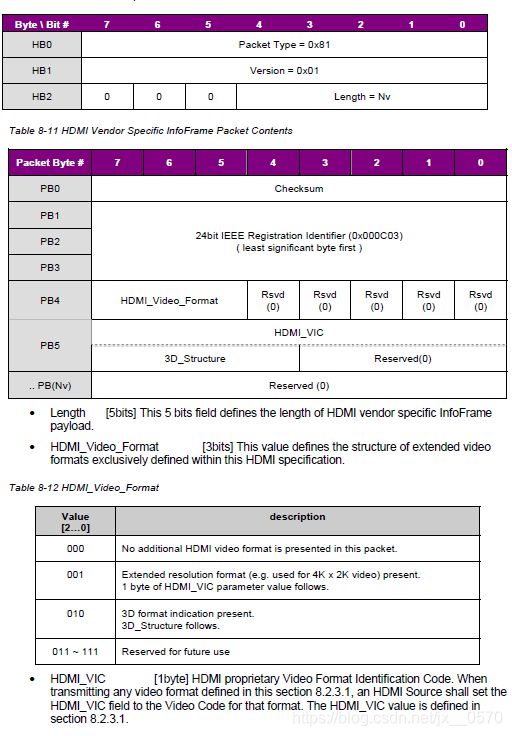

这是CEA-861供应商特定的信息帧,其中包含24位IEEE注册标识符0x000C03,该值属于HDMI Licensing,LLC。此InfoFrame的内容由此规范定义。

对于源设备,此InfoFrame的传输是可选的。但是,如果信源设备输出第8.2.3节中定义的视频信号,则信源应发送此数据包。

每当发送此数据包时,每两个视频字段至少应发送一次准确的HDMI供应商特定信息帧。

接收器解释此数据包是可选的。如果接收器支持HDMI_VIC,则应使用HDMI_VIC值。即使发送了HDMI供应商特定的InfoFrame,AVI InfoFrame数据包中的其他数据仍然有效。

此HDMI供应商特定的InfoFrame的分组化定义如下。

8.2.3.1 HDMI视频格式标识代码在本节中,定义了由HDMI_VIC号标识的HDMI视频时序格式。

表8-13中显示的以下视频格式用于4K x 2K视频信号传输。

表8-13和图8-2定义了表8-13中每个参数的含义。

8.2.3.2 3D视频格式结构使用AVI InfoFrame中的VIC(视频标识代码)指示3D视频格式(指示2D图片之一的视频格式,如CEA-861-D或表8-4所定义))以及HDMI Vendor Specific InfoFrame中的3D_Structure字段(指示3D结构)。