CaptureCIS 和Allegro快速成长手册

CaptureCIS 和Allegro快速成长手册

从captureCIS到Allegro,从原理图到PCB全过程详细指导

CaptureCIS 绘制

绘制器件

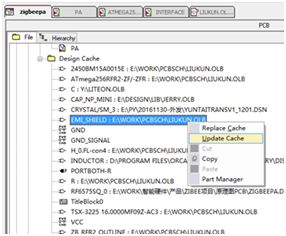

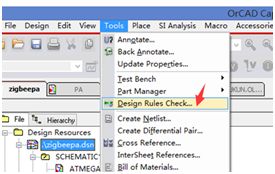

原理图更新原器件

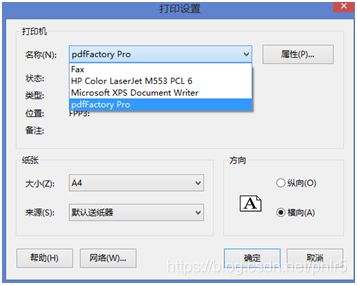

CaptureCIS生成pdf文件

生成bom

Allegro绘制器件

比较好的一片基础文档:

e:\tools\candence\cadence–allegro-16.6入门学习参考步骤.pdf

下面这个文档更好一些:

“e:\tools\candence\CADENCE ALLEGRO 16.6实战必备教程.pdf”

Allegro一些基本的意思:

Symbol所需层面:

Package Geometry ? Silkscreen_top(零件外框层,此层面不可压PAD)

Package Geometry ?Slodermask_top(防焊层)

Package Geometry ? Dimension(标注尺寸)

Package Geometry ? Footprint(封装名称)

Package Geometry ? Pad(PAD名称)

Package Geometry ? Hight(高度)

Package Geometry ? Place_bound_top(禁止放零件区域,需设置零件高度)

Maufacturing ? No_probe_top(禁止探针探入区域)

Maufacturing ? No_probe_bot(禁止加测点区域,一般用于chip的零件,如:BGA, PGA)

Maufacturing ? No_place_bot(禁止背面放零件区域,用于DIP零件,SMD零件不需高此层面,在PAD的外缘基础上加3MM)

Maufacturing ? Shape problems(在椭圆PAD上用箭头标注出椭圆孔的尺寸且需备注PAD是PTH or NPTH,如:0.75X3.2MM(PTH),一般将数字小的放在前面)

Ref Des ? Assembly_top(组装层文字面层)

Ref Des ? Silkscreen_top(丝印层文字面层)

Comonent Value ? silkscreen_top(Value)

Component Value ? Assembly_top(零件组装层)

Via Keepout ? top(禁止打VIA区域,用于SMD PAD,在PAD的基础上单边加3MIL,对SMD零件VIA Keepout应加在TOP(BGA里要孙PAD稍大),DIP则加在VIA Keepout all)

Device Type ? Silkscreen_top(封装名称)

Route ?Keepout_top(禁止走线区域)

Symbol分类:

1.Pack symbol:组件的封装符号 *.psm

2.Mechanical symbol:由板外框及螺丝孔所组成的机构符号 *.bsm

3.Format symbol:由图框和说明所组成的组件符号 *.osm

4.Shape symbol:供建立特殊形状的焊盘用 *.ssm

5.Flash symbol:焊盘连接铜皮导通符号 *.fsm

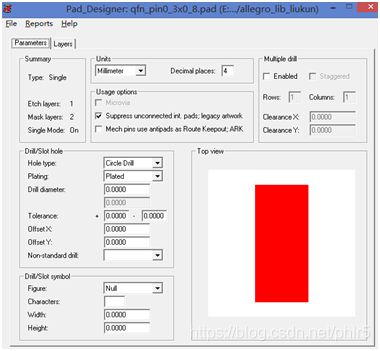

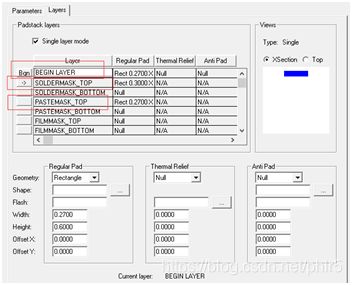

Allegro绘制焊盘:

https://www.cnblogs.com/chensmith/p/8151425.html

a、 用Pad Designer,设计表贴焊盘。在库里面调出一个焊盘,

保存为pad文件

Allegro绘制器件

https://www.cnblogs.com/dongfengweixiao/p/5819625.html

Allegro更新器件封装的焊盘

Allegro绘制不规则焊盘

https://www.cnblogs.com/ohio/p/3912495.html

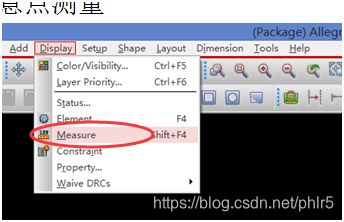

Allegro使用任意点测量

Allegro移动焊盘到准确位置

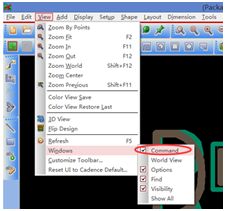

首先打开Command窗口:

之后点击

之后

点击需要移动的焊盘,输入键盘 x 1.25 2.48,就可以了。

Allegro邮票孔焊盘

https://blog.csdn.net/u010444107/article/details/79274898

采用郭江峰的例子:

e:\work\智能硬件\产品\zibee项目\硬件参考\3422-130-09271-H\3422-130-09271-H.brd

Allegro绘制板框

在命令窗口 x a b,确定第一个点,之后x c d确定对角线的点。Rectangle就划好了。

常用的命令如下:

Allegro设置层结构

Layer Type

层的类型。

Conductor 信号层的类型

Dielectric 电介质

Plane 地层和电源层的类型

DRC as Photo File Type

? Positive 正片

? Negative 负片

(Positive )正片:简单地说就是,在底片上看到什么就有什么。

(Negative)负片:正好相反,看到的就是没有的,看不到的就是有的

Conductivity:导电度

Dielectric Constant:介电常数

Loss Tangent:介质损耗正切

介绍相关参数关系的一篇文章:

http://www.51hei.com/bbs/dpj-78081-1.html

设置完层后,就可以导入netlist了。

先设置封装路径

Allegro设置封装路径

Allegro导入netlist

allegro快速放置器件

allegro快速放置器件出现outside of drawing extents,扩大图纸面积,或可以手动放置。

Allegro 设置undo redo的级数

Allegro锁定器件

选定器件点击Fix按钮

Allegro隐藏device type

最后在封装库里面把device type去掉了。

导入器件后器件device type显示一长串

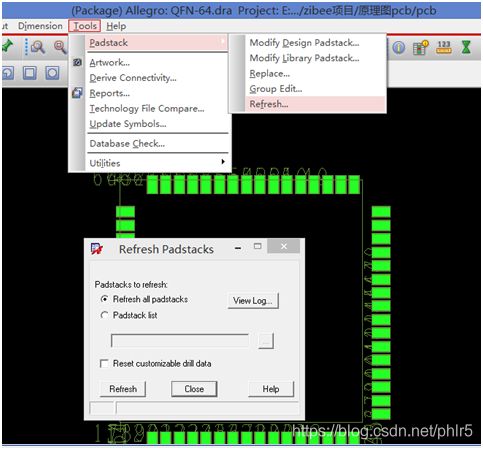

Pcb上如何更新封装

Allegro如何设置默认走线宽度

Allegro如何设置默认过孔

allegro如何修改过孔大小

allegro如何设置间距

Allegro如何换层

Allegro画线的时候如果不让线自动跑偏拐弯

下图这两个都不选则。

Allegro 如何隐藏pin number

Allegro如何隐藏和显示网络连接线、鼠线

logic=>Identify DC Nets,在里面把地或者电源设置成0或者3.3之类的就能隐藏鼠线了,并且这些被隐藏的网络会用方框包起来,这样也不会忘了布线

显示的话,就Delete可以了。

Allegro如何走差分线

设置完之后在PCB上选择这两个网络点击Route-》Connect

之后两条线会都一起引出,可以点击鼠标右键,选择single trace mode,进行单条线走线。

Allegro如何在任意位置放置过孔

在焊盘或者覆铜处双击,就可以放置过孔了,过孔的连接网络应该是焊盘或者覆铜的网络。

Allegro 如何设置器件标号的尺寸大小

统一设定元件编号大小

Edit-Change

之后在设置find选项:

之后在Options设置:

和

之后就可以点击要修改的器件标号,或者框选全部修改。

Allegro如何覆铜

CM设置:

之后选择:

之后选择option

之后画长方形。

Allegro如何去掉覆铜的孤岛 死铜

Shape->Delete Islands在options里面会出现如下属性,死铜的个数。点下边的按钮可全部删除死铜。

Allegro显示覆铜

这两项不勾。

Allegro如何显示Place bound top

Allegro如何做问题检查DRC检查

Allegro如何导出gerber光绘文件

选择需要的层,进行生成gerber文件。

Allegro生成钻孔文件

设置参数:

生成drv文件

生成NC Drill和Route文件。

Allegro最终绘制板子