verilog基础知识点

目录

1、模块的基本架构

2、数据类型

2.1、数值

2.2、线网类型

2.3、变量声明/寄存器类型

3、连接方式

3.1、端口位置连接

3.2、端口命名连接

4、 操作符

5、 数据流建模

连续赋值语句assign

6、行为级建模

6.1、行为级建模常包含语句

6.2、过程块

6.3、语句块

6.4、多路分支语句case

6.5、循环语句for

6.6、function and task

7、测试平台

7.1、顶层测试模块

7.2、结构化测试模块

以下为灵活运用知识

1、模块的基本架构

module 模块名(端口列表);

//端口声明可以再端口列表,也可以在模块内,input,output,inout

//参数定义(常量)

//内部信号声明,wire或reg

//模块内部可以包涵function、task,

//低层次的引用,

//连续赋值语句assign、过程块initial,always

endmodule

2、数据类型

2.1、数值

0:逻辑低电平

1:逻辑高电平

z:高组态,三态

x:未知逻辑电平

2.2、线网类型

wire [7:0] x; //x是8bit的wire型连线;

wire #(2,1) carry; //带上升、下降延迟的线网;

注意:verilog HDL程序模块中输入输出信号类型默认为wire类型。

2.3、变量声明/寄存器类型

reg [7:0] a [0:4]; //5个8bit符号变量,或称为5个8bit寄存器,或位宽为8深度为5的寄存器;注意:变量是数据存储单元的抽象,常包含reg、time、integer类型,其初值是不定态“x”值,可以储存数据赋值给其它变量、线网。

3、连接方式

3.1、端口位置连接

//调用模块

modulenamel(...);

//端口定义

//端口描述

//mux u1(in1,in2,sel,out);

endmodule

//被调用模块

modulenamel(in1,in2,sel,out);

//端口定义

//端口描述

//具体代码

endmodule3.2、端口命名连接

module same_port(.a(i),.b(j));

//.a,.b被调用模块端口

//i,j调用模块的端口名举例:

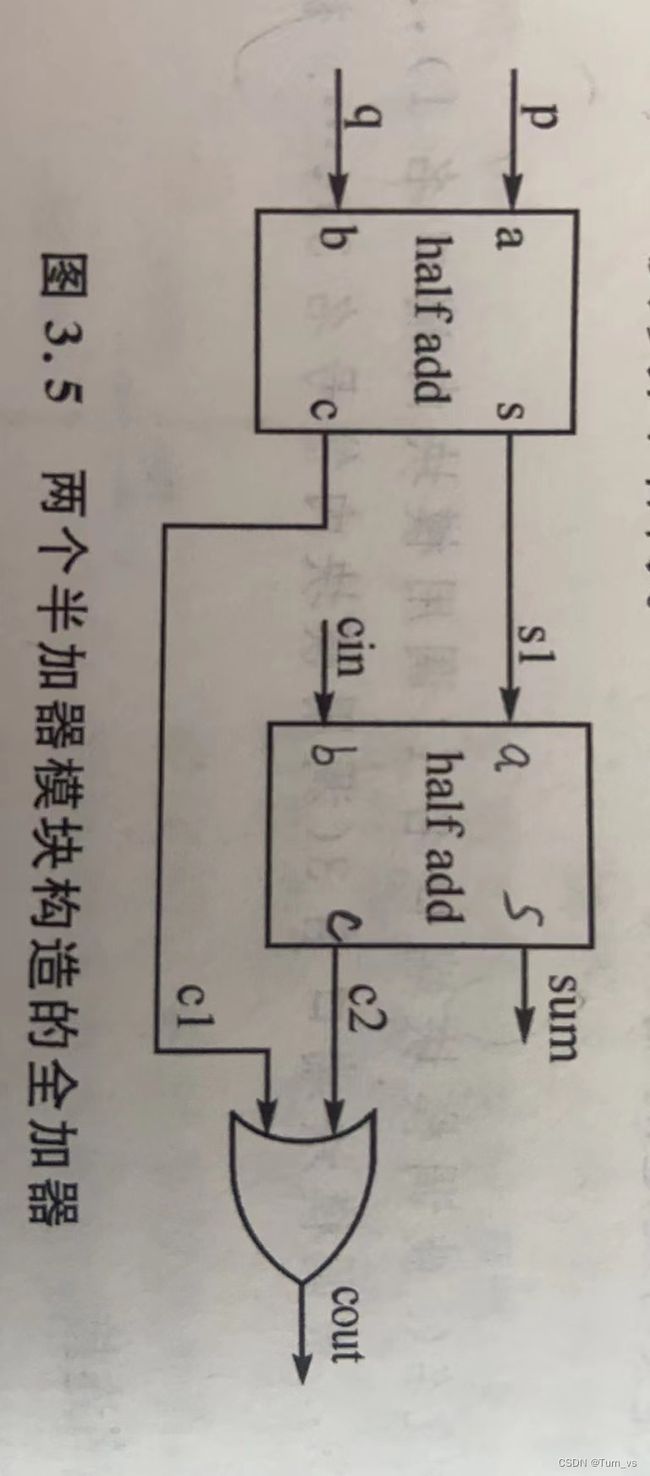

module full(p,q,cin,sum,cout);

input p,q,cin;

output sum,cout;

wire s1,c1,c2;

//两个实例调用语句

half h1(p,q,s1,c1); //端口位置连接,第一个半加器四个端口的连接

half h2(.b(cin),.s(sum),.a(s1),.c(c2)); //端口命名连接,第二个半加器四个端口的连接

or h3(cout,c1,c2);

endmodule

module half(a,b,s,c) //被调用的半加器模块;

input a,b;

output s,c;

求和描述;

进位描述;

endmodule

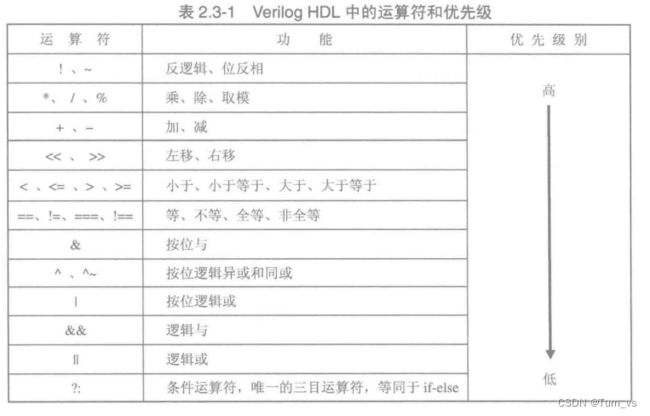

4、 操作符

5、 数据流建模

连续赋值语句assign:连续赋值是用某个逻辑值驱动线网,一般用关键字assign声明,赋值用操作符“=”执行

assign {out_y,s}=a+b+c;注意:

- 赋值式的左边必须是线网类型

- 连续赋值总是处于赋值操作的状态,只要赋值表达式右端数据变化,就会赋值给左端。

- 赋值语句的右端可以是线网或寄存器类型,也可以是函数调用。

- 连续赋值语句可以不用关键字assign,既隐式连续赋值结构。

6、行为级建模

采用逻辑门级建模或连续赋值建模方法能实现简单功能的电路描述,其特点是易于理解电路的门级关系,更准确的描述电路的物理结构;但是实际工程设计中,像微处理单元等复杂抽象逻辑需要提供描述复杂系统的更高层抽象功能。

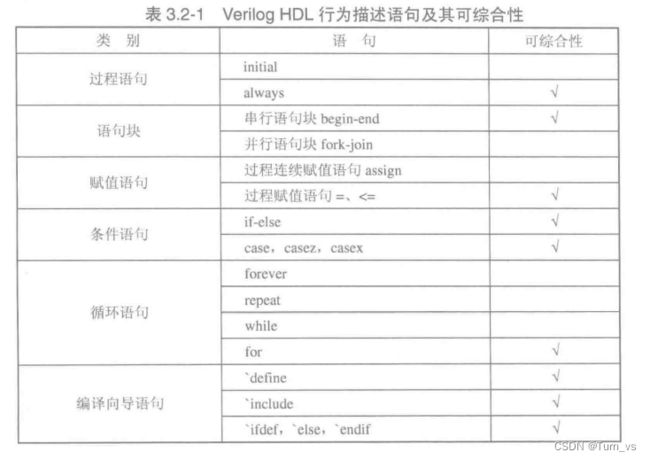

6.1、行为级建模常包含语句

6.2、过程块

1、initial语句

initial过程块(initial语句中的所有行为)只执行一次,在仿真初始时刻(0时刻开始)并发执行直到当前状态结束

initial begin

语句1;

语句2;

...

end

2、always语句

always过程块(always语句中的所有行为),在仿真初始时刻(0时刻开始)当过程块中最后一条语句执行结束后,在时序控制条件下再次执行过程块的第一条语句,直到仿真结束。

always@(posedge clk) begin

q1<=in; //always中触发条件带时序,内部用非阻塞赋值;

q2<=q1;

end6.3、语句块

- 顺序块(关键字:begin...end):语句块中语句按照给定顺序执行

- 并行块(关键字:fork...join) :语句块中语句按照给定并发执行,不可综合,一般在测试平台使用

6.4、多路分支语句case

根据条件表达式的值进行分支执行的行为类似多路复用选择器,多路分支语句的关键字为case、endcase、default。

always@(*) begin

case(sel)

0:out=in[0];

1:out=in[1];

2:out=in[2];

default:out=in[0]; //默认的过程声明语句,默认的分支项。

endcase

end6.5、循环语句for

integer i;

for(i=0,i<1,i++) begin

...

end- 1、初始条件,对控制变量赋初值;

- 2、循环条件,也被称为“终止条件”

- 3、改变控制变量的过程赋值语句

6.6、function and task

task

对于行为级建模,代码结构会出现不同位置代码,执行相同功能的情况,为了方便理解与复用。输入输出和总线信号可以传入、传出任务,函数只能传入并由函数名返回结果。

task 任务标识符;

输入输出变量声明;

语句声明;

endtasl

//例:

task mult_use; //任务块定义

input [3:0] xme,tome;

output[7:0] result;

wait(delay)

result=xme*tome;

endtask

//调用

<任务名>(端口1,端口2,...,端口n)

multi_use(a,b,out); //任务调用语句function

函数至少需要一个输入变量,一个返回值,在函数中不能调用任务,通常用于计算某一个函数值或描述组合逻辑。

function 返回值类型或返回值宽度 函数名;

输入端口声明;

局部变量声明;

begin

行为语句1;

行为语句2;

end

endfunction

///

function [7:0]fun_log;

input[7:0]a,b,c;

input en;

...

endfunction

//函数调用

{out1,out2}=fun_log(a,b,c,en);- 1、n个端口与函数定义结构中说明的各个输入输出端口一一对应;

- 2、在verilog语言中函数不能自动递归调用,当被不同地方同时调用时可能会出现错误,使用关键字automatic,自动递归调用时仿真器为每次函数调用动态的分配新的地址空间,例如:

function automatic int facto_func;- 3、函数不能作为一条单独的语句出现,只能作为语句的一部分。

7、测试平台

7.1、顶层测试模块

对于简单的待测模块,在测试平台中编写测试代码完成简单模块的仿真测试工作

7.2、结构化测试模块

对于复杂的待测模块,按照模块化的思想分层进行测试模块的设计和开发,针对不同测试案例以完成复杂待测模块的功能和性能验证。

`timescale 10ns/1ns //定义仿真时间尺度

`include "dut.v" //包含所设计的待测模块源文件

`include "sigdata.v" //包含激励信号生成模块文件

`include "verifdata.v" //包含监视验证模块源文件

module test; //仿真测试模块名

//各种输入输出变量定义

wire clk; //激励信号:时钟

wire reset; //激励信号:重置

wire[7:0] data; //激励信号:测试向量

wire[7:0] result; //待测模块输出信号

//调用激励信号生成模块

sigdata sig(.rst(reset),.clk(clk),.data(data));

//调用待测试模块

dut m(.rst(reset),.clk(clk),.data(data),.result(result));

//调用监视验证模块

verifdata verif(.rst(reset),.clk(clk),.data(data),.result(result))

endmodule

=========================================================================

以下为灵活运用知识

循环序列,时钟建立,数据显示,译码器,检测器,分频器,组合逻辑电路,时序逻辑电路,连续赋值语句assign,过程块语句always,if,case,选择器,奇偶校验,串并转换,有限状态机,时序与延迟,锁存器,寄存器(时序要求),逻辑综合,定向测试,受约束随机测试,代码覆盖率,功能覆盖率,断言覆盖率,分频器,积分,微分,阻塞,非阻塞。重点:FIFO、全双工UART接口设计。