2023/9/26 -- ARM

【计算机相关理论】

1.计算机的组成

输入设备、输出设备、存储器、运算器、控制器

1.输入设备:将编写好的软件代码以及相关的数据输送到计算机中。转换成计算机可以识别、存储

和处理的数据。

例如:鼠标、键盘、复印机、传感器

2.输出设备:将计算机处理的数据的结果通过输出设备进行输出,输出到计算机的外部。

例如:显示屏 音响 打印机 投影仪

3.存储器:存储器是计算机用来存放程序指令和数据的部件,也是计算机能够实现“程序存储控制”

的基础。

- MMU 内存(主存储器):一般程序的指令的执行时会预先加载到内存上,CPU从内存里拿数据和指令。

- 外存(辅助存储器):存储一些不直接加载到程序里的数据。

- 缓存(cache):暂时存储数据的部件,CPU快速读取数据。

- volatile 寄存器:在cpu内部,没有地址概念。

4.控制器(CU):计算机的控制中枢,对机器指令进行译码,并且对译码后的结果做相关控制。

5.运算器:算数逻辑运算单元(ALU)将译码后的指令进行逻辑算数运算,并且把运算结果输出。

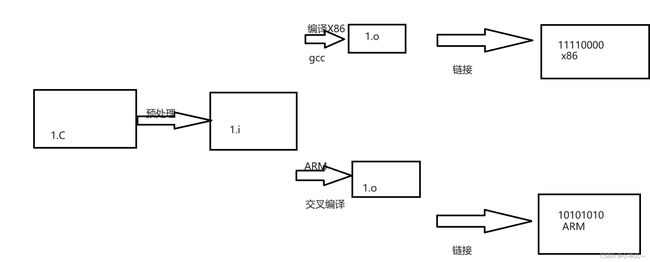

2.程序编译的原理

编译步骤:预处理 编译 汇编 链接

CPU能够识别的唯一的语言是机器语言,一个CPU能够识别哪一些机器指令是由处理器的硬件(运算器的类型)决定的。不同的机器指令代表不同的运算。不同的CPU的机器码是不通用的,不可以移植。汇编就是一个机器码的标识。不同的CPU机器指令不通用所以汇编也不通用。我们可以采用不同的编译工具将C程序编译生成在不同架构机器上可以执行的机器指令文件

3.指令和指令集

机器指令(指令的机器码):由二进制的0和1组成的一条机器码。计算机解析这条机器指令可以做相应的运算处理。

汇编指令:每一条汇编指令就是一条机器指令的标志。执行汇编指令可以让计算机做出相应的运算处理。

汇编的指令集:汇编指令的集合。

4.RISC和CISC

4.1 RISC精简指令集

精简指令集的架构主要应用在嵌入式的设备上

精简指令集是在复杂指令集的基础上选取一些比较简单,使用频率比较高的指令,组成了一个指令集

精简指令集的特点:

1.指令的长度和执行周期固定

指令的长度:一条机器指令在计算机占用的存储空间

指令的周期:CPU执行一条机器指令所花费的时间(时钟周期)

时钟周期:CPU的工作频率决定

2.基于精简指令集生产的CPU功耗低,成本低,但是实现的功能也相对简单

对于ARM指令,但多数都是单周期指令,指令长度为32bit

查看一个ARM机器的程序中的指令长度:

使用交叉编译工具链生产程序的反汇编文件 arm-linux-gnueabihf-objdump -D a.out

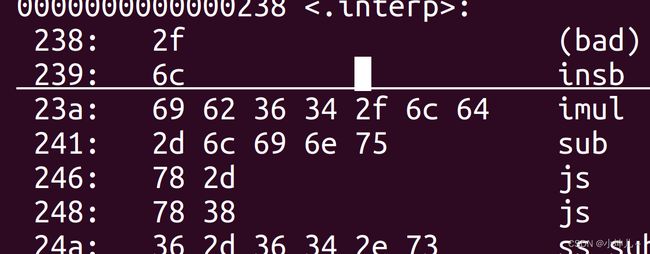

4.2 CISC:复杂指令集

复杂指令集的架构一般用于PC端 X86和X64都是复杂指令集CPU

复杂指令集更加注重指令的功能性,复杂指令集的指令周期和指令的长度都不固定

复杂指令集生产的芯片成本、功耗都会更大,但是性能也会更强

查看复杂指令集的程序机器码: gcc 1.c objdump -D a.out > a.dis

5.国际上比较主流的几类RISC内核

ARM内核--》主流的嵌入式内核,不开源,需要授权 RISC-V->正在发展,开源 MIPS:完全闭源,中国龙芯科技将MIPS直接买断,不受版权控制,还在它的基础上做了拓展

【ARM相关内容】

1.ARM的发展

ARM发展史 (huawei.com)

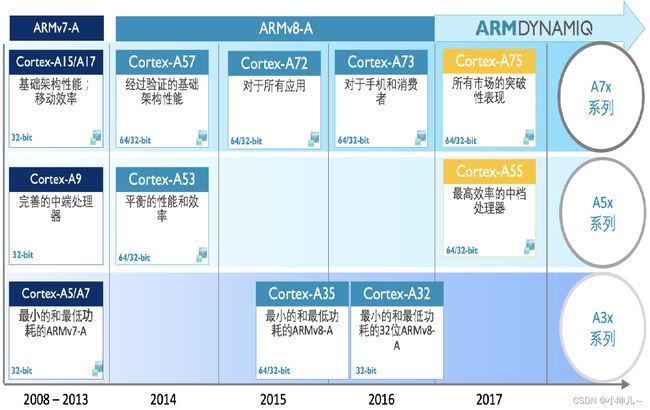

2.ARM架构

arm针对不同版本的指令集起的名字叫做ARM不同的架构

- ARMV1-ARMV6架构:已经被淘汰

- ARMV7架构:32位的架构,支持32位指令集的架构

- ARMV8架构:64位架构,支持64位指令集的架构,向下兼容32位指令

- ARMV9架构:64位架构,支持64位指令集的架构

3.ARM内核

基于不同的架构生产出来的不同的处理器核心叫做内核

- arm7/arm9/arm11

- cortex-A7 ARMV7

- cortex-A53 ARMV8

- cortex-A55 ARMV8

- cortex-A77 ARMV8

- cortex-A78 ARMV8

- cortex-X1 ARMV8

- cortex-a710 ARMV9

- cortex-a510 ARMV9

4.SOC(system on chip)

ARM公司只做技术授权,将自己的IP授权给芯片厂商,芯片厂商基于ARM提供的arm技术,在ARM处理器的基础上添加了一些外围设备和电路,集成了一个芯片,这个芯片被称为SOC(片上系统)

5.ARM产品分布

5.1 cortex-A系列

cortex-A系列的核心是ARM处理器中性能最完善的 处理器。属于高端处理器 在

基于cortex-A的核心的开发板上可以搭载linux\鸿蒙等标准化操作系统

5.2 cortex-R系列

cortex-R系列的处理器追求系统的实时性能,对于数据的实时性要求高的场景下使用cortex-R系列的处理

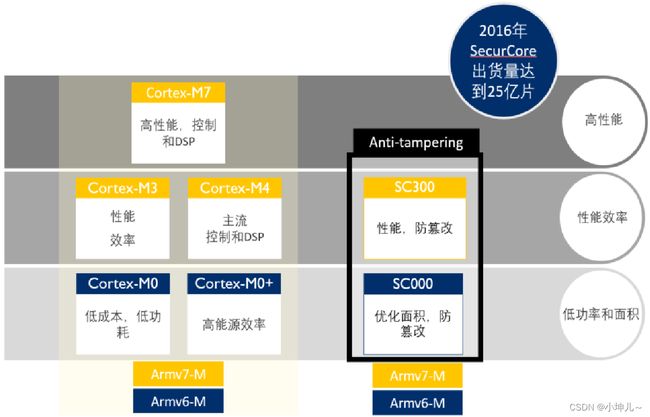

5.3 cortex-M系列

ARM处理器中比较低端的芯片处理器,处理器的工作主频一般在24MHZ-256MHZ之间

cortexM处理器一般不跑操作系统,主要执行一些裸机程序

cortex-M可以搭载一些实时操作系统 freeRTOS

5.4 SecurCore系列

用于对于安全性能要求比较高的场景下

6.ARM的数据约定

A7采用的是32位架构.

ARM32位处理器 约定:

- Byte 8 bits.

- Halfword 16 bits.

- Word 32 bits.

- Doubleword 64 bits.(64位处理器中才有)

- quardworld 128bit (64位处理器中才有)

7.ARMv7架构和ARMV8架构的区别

ARMV7架构支持32位汇编指令集

32位指令集表示一条指令的大小是32位

ARMV8架构支持64位汇编指令集,同时向下兼容32位指令集

32位的处理:表示一条指令最高可以完成32位数据的运算

ARM指令集:一条指令32位

THUMB指令集:一条指令16位

8.ARM的工作模式

ARM 有7种基本工作模式:

- User : 非特权模式,大部分任务执行在这种模式

- FIQ : 当一个快速(fast) 中断产生时将会进入这种模式

- IRQ : 当一个通用(normal) 中断产生时将会进入这种模式

- Supervisor(svc) :当复位或软中断指令执行时将会进入这种模式

- Abort : 当存取异常时将会进入这种模式 Undef : 当执行未定义指令时会进入这种模式

- System : 使用和User模式相同寄存器集的特权模式 Cortex-A特有模式:

- Monitor : 是为了安全而扩展出的用于执行安全监控代码的模式; 也是一种特权模式 HYP:虚拟化模式,当一个硬件上运行两个OS内核时进入这个模式

9.ARM寄存器组织

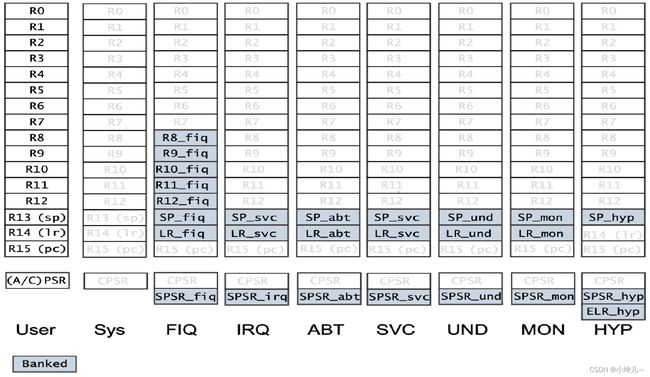

9.1 ARM V7架构各个模式下的寄存器组织

1.每一种工作模式下只能使用自己这个模式下的寄存器

2.user模式和system可以使用的寄存器是17个,这17个寄存器被称为通用寄存器

3.处理ssytem模式,其他的特权模式下都会有自己特有的寄存器可用

4.寄存器没有地址,想要访问这个寄存器直接通过寄存器名字或者编号就可以访问

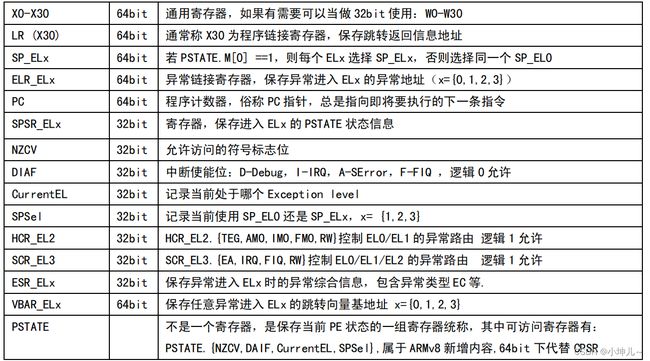

9.2 ARM V8架构下的寄存器组织

9.3 ARM V7架构下的一些特殊功能寄存器

R13寄存器(SP)

SP(stack pointer):R13又被称为栈指针寄存器

一般在内存中分出一部分内存当作栈使用,SP寄存器始终保存栈顶空间的地址

栈中一般存放一些临时数据,也可以用于进行保护现场

r15寄存器(PC)

PC(program counter):程序计数器

PC寄存器中始终保存马上就要执行的指令的地址,每次指令执行完毕后PC寄存器的值会自动向下+4,特殊情况下可以手动修改PC寄存器的数值

R14寄存器(LR)

LR(link register):链接寄存器,在程序跳转时保存跳转指令下一条指令的地址,方便程序返回

当程序跳转后PC保存跳转后的指令的地址

程序返回时,将LR寄存器的值赋值给PC寄存器,CPU就可以执行跳转指令下一条指令了

CPSR寄存器和SPSR寄存器

1. cpsr : current program stated register

当前程序状态寄存器:保存的是当前程序的运行状态(比如工作模式)

2. spsr : saved program stated register

保存程序状态寄存器:主要用户保存当前程序状态寄存器的。

1. N[31] : 指令的运行结果为负数时,N位被自动置1,否则为0.

eg : 100 - 200

2. Z[30] : 指令的运行结果为零时,Z位被自动置1,否则为0.

100-100

3. C[29] :

加法:加法运算如果产生进位,C位被自动置1,否则为0.

32位指令:低32位向高32位进位

0XFFFFFFFF+1

减法:减法运算如果产生借位,C位被自动清0,否则位1.

32位指令:低32位向高32位借位

1-0XFFFFFFFE

4. V[28] : 符号位发送变化,V位被自动置1,否则清0.

5. I[7] : IRQ中断屏蔽位

I = 0 : 不屏蔽IRQ中断

I = 1 : 屏蔽IRQ中断

6. F[6] : FIQ中断屏蔽位

F = 0 : 不屏蔽FIQ中断

F = 1 : 屏蔽FIQ中断

7. T[5] : 状态位

T = 0 : 表示ARM状态,执行的是ARM指令集

T = 1 : 表示Thumb状态,执行的是Thumb指令集

ARM指令集 : 一条汇编指令编译生成32位的机器码

thumb指令集:一条汇编指令编译生成16位的机器码

ARM指令集的代码的密度低,而thumb指令记得代码密度高。

ARM指令集的功能性要高于Thumb指令集。

8. M[4:0] : 模式位

10000 User mode;

10001 FIQ mode;

10010 IRQ

10011 SVC mode;

10111 Abort mode;

11011 Undfined mode;

11111 System mode;

10110 Monitor mode;

其他没有使用到的值,保留。10 ARM的流水线工作

10.1 一条指令的执行过程

1.取址:cpu将PC寄存器的数值通过地址总线传输给存储器,存储器将PC存储的地址位置的指令传输到CPU内存,存放在IR寄存器中

2.译码:IR寄存器的指令交给译码器,对指令进行译码

3.执行:控制器把译码之后的指令交给运算器,运算器再进行对于的运算操作

10.2 ARM三级流水线

当一条指令正在被取址时,译码模块和执行模块处于空闲状态,这样两个模块没有被充分利用。为了充分利用指令处理模块,增加指令处理速度,我们引入了三级流水线: