数字IC设计笔试常见大题整理(简答+手撕)

IC修真院为大家整理了一些数字IC设计的笔试常见题目,大家快来领取吧~

面试题目(文末可全领)

![]()

1. 简述latch与FF的区别,并用verilog分别实现1bit latch与DFF。

Latch对电平信号敏感,在输入脉冲的电平作用下改变状态。

DFF对时钟边沿敏感,检测到上升沿或下降沿触发瞬间时改变状态。

2. IC设计中reset的设计通常有同步reset和异步reset两种方式。

1) 简述两种reset方式的区别?

2) 异步reset的主要缺点是什么?

3) 设计中如何规避异步reset的缺点?

1)同步reset是指复位信号只在时钟上升沿到来时才有效,异步reset是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

2)异步reset的主要缺点是复位信号的随机性会导致亚稳态,而且对电路内的毛刺敏感,容易造成复位错误。

3)可以采用异步复位同步释放的方法来解决这个问题,即复位与clk无关,复位信号在第二级触发器的clk边沿到来后释放,第二级输出是稳定且被同步的。多打一拍,消除亚稳态,从而触发器会在一个或两个时钟周期内返回稳态。

3. 阐述“时钟抖动”的基本概念,可能产生的原因?在数字逻辑设计中对setup time和hold time的影响是什么?

时钟抖动指的是信号周期的长度会有一定变化,从而导致下一个时钟沿到来的时间不确定,主要是时钟周期T变化。抖动是在时钟发生器内部产生的,产生的原因和晶格振动以及内部电路有关。时钟抖动的存在会影响电路中的时序收敛,导致setup time和hold time出现violation。

4. 阐述一下meta-stability的概念及在设计中如何防止?

亚稳态指的是触发器无法在某个规定的时间内达到一个可以确认的状态。触发器进入亚稳态后,无法预测其输出电平,也无法预测输出何时能稳定。

在设计中,为了抑制亚稳态现象,在跨时钟域传输时,对于单bit信号,可以使用双锁存器法同步、边沿检测同步器、脉冲检测同步器的方法来进行同步。对于多bit信号,可以采用握手协议以及异步FIFO来解决。

5. 给定一个时钟信号clk,设计一个占空比为50%的三分频时钟clk_div3,用Verilog写出这个设计。

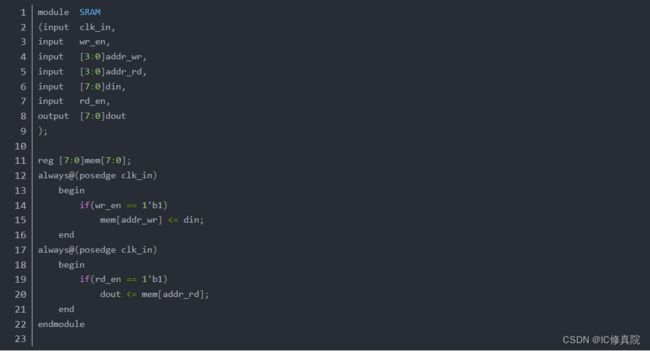

6. 设计一个顶层模块,顶层模块实现一个双口SRAM,一个口只读,一个口只写。试用Verilog写出这个顶层模块的实现。

7. 根据自己的理解列出经典处理器CPU执行大致阶段,以及各阶段的大致行为。

取指(fetch):从主存中取指令到指令寄存器。

译码(decode):将指令按照指令结构,进行拆分解释,识别区分不同指令类别和各种获取操作数的方法。

执行(execute):实现指令的功能。

访存(memory):根据指令访问主存,读取操作数。

写回(write back):将运算结果写回到某存储器。

8. 芯片设计三个核心指标为PPA,请解释这三个字母分别代表什么,并阐述你对PPA的理解。

performance性能、power功耗、area面积 。

在流水线设计中,流水线越深:追求性能,更高的主频。流水线越浅:追求功耗,小面积低功耗。

面积换功耗:门控时钟(动态功耗),电源门控、多阈值电压、动态电压(静态功耗)。

面积换性能:大容量cache提高cpu的hit几率。

功耗换性能:关键路径采用低阈值电压cmos,但静态功耗很大。

9. What is The Difference Between Mailbox And Queue?

队列存放有序的同类元素,同时结合了链表的优点可以任意位置操作或访问。

mailbox是跨线程的通信,一个线程中写入数据,可以在另一个线程中将数据读出。

10. What Is The Use Of $cast?

$cast为了强制类型转换,可以把基类句柄赋值给扩展类句柄,前提是基类句柄指向了这个扩展类对象或者这个扩展类的扩展类对象,强制类型转换后,这个扩展类句柄就会指向这个扩展类的对象或者这个扩展类的扩展类的对象。

11. UVM中,如果想要某个成员使用UVM compare和print函数,需要如何操作该变量?

通过域的自动化,在注册UVM类的同时可以声明今后会参与到对象拷贝、克隆、打印等操作的成员变量。

12. 如何启动sequence?

13. 请根据下面的设计描述,尽可能多的列出你所能想到的用于功能验证的测试点。

一个异步FIFO, rdata和wdata均为8位数据,FIFO深度为16,当rst_n输入为低时,FIFO被复位,当wclk的上升沿采样到wr为高时,数据被写入FIFO,当rclk的上升沿采样到rd为高时,FIFO输出数据。此外,当FIFO为空时,empty信号输出为高,当FIFO满时,full信号输出为高。

测试点:

(1) 同时读写,读写数据正确检查。

(2) FIFO满标志位检查。

(3) FIFO空标志位检查。

(4) 写过程中发生写复位,写数据和FIFO满标志被清空。

(5) 读过程中发生读复位,读数据和FIFO读空标志位被清空。

(6) 读写时钟相位相同,异步FIFO能正常工作。

(7) 读写时钟相位不同,异步FIFO能正常工作。

(8) 写时钟等于读时钟,异步FIFO能正常工作。

(9) 写时钟快于读时钟,异步FIFO能正常工作。

(10) 写时钟慢于读时钟,异步FIFO能正常工作。

(11) 写过程中发生写复位后,异步FIFO能继续正常工作。

(12) 读过程中发生读复位后,异步FIFO能继续正常工作。

(13) FIFO满以后,继续往FIFO写数据,异步FIFO不会被卡死,数据被读走以后,FIFO能继续正常工作。

14. 简述流水线设计的方法和作用。

典型的流水线设计是将原本一个时钟周期完成的较大的组合逻辑,通过合理的切割后分由多个时钟周期来完成,这样一来该部分逻辑运行的时钟频率就会有明显的提升,尤其当它是一条关键路径时,采用流水线设计后整个系统的性能都会得到提升。

流水线设计从某种程度上可以提高系统频率,因此常用于高速信号处理领域,如果某个信号可以分为若干步骤处理,而且整个数据处理过程是单项的,即没有反馈运算和迭代运算,前一个步骤的输出就是下一个步骤的输入,可以考虑流水线设计来提高系统的频率。

15. 请简述数字后端P&R流程。

后端设计流程:

1、可测性设计——DFT

Design ForTest,可测性设计。芯片内部往往都自带测试电路,DFT的目的就是在设计的时候就考虑将来的测试。DFT的常见方法就是,在设计中插入扫描链,将非扫描单元(如寄存器)变为扫描单元。关于DFT,有些书上有详细介绍,对照图片就好理解一点。DFT工具:Synopsys的DFT Compiler。

2、布局规划(FloorPlan)

布局规划就是放置芯片的宏单元模块,在总体上确定各种功能电路的摆放位置,如IP模块,RAM,I/O引脚等等。布局规划能直接影响芯片最终的面积。工具为Synopsys的Astro。

3、时钟树综合——CTS

Clock Tree Synthesis,时钟树综合,简单点说就是时钟的布线。

由于时钟信号在数字芯片的全局指挥作用,它的分布应该是对称式的连到各个寄存器单元,从而使时钟从同一个时钟源到达各个寄存器时,时钟延迟差异最小。这也是为什么时钟信号需要单独布线的原因。CTS工具,Synopsys Physical Compiler。

4、布线(Place & Route)

这里的布线就是普通信号布线了,包括各种标准单元(基本逻辑门电路)之间的走线。比如我们平常听到的0.13um工艺,或者说90nm工艺,实际上就是这里金属布线可以达到的最小宽度,从微观上看就是MOS管的沟道长度。工具Synopsys的Astro

5、寄生参数提取

由于导线本身存在的电阻,相邻导线之间的互感,耦合电容在芯片内部会产生信号噪声,串扰和反射。这些效应会产生信号完整性问题,导致信号电压波动和变化,如果严重就会导致信号失真错误。提取寄生参数进行再次的分析验证,分析信号完整性问题是非常重要的。工具Synopsys的Star-RCXT

6、版图物理验证

对完成布线的物理版图进行功能和时序上的验证,验证项目很多,如LVS(Layout Vs Schematic)验证,简单说,就是版图与逻辑综合后的门级电路图的对比验证;DRC(Design Rule Checking):设计规则检查,检查连线间距,连线宽度等是否满足工艺要求;ERC(Electrical Rule Checking):电气规则检查,检查短路和开路等电气规则违例;等等。工具为Synopsys的Hercules。

需要上述面试题目的同学可按需领取,点击下方链接可以直接分享给大家~

这里放个口:IC笔面试题目

![[图片]](http://img.e-com-net.com/image/info8/0421c460688e4b238fe430555efbf1c6.jpg)

![[图片]](http://img.e-com-net.com/image/info8/7dbfa69d5399423e954a923ef75a8138.jpg)