FPGA project : TFT_LCD

实验目标:

驱动TFT_LCD显示十色彩条。

重点掌握的知识:

1,液晶显示器,简称LCD(Liquid Crystal Display),相对于上一代CRT显示器(阴极射线管显示器),LCD显示器具有功耗低、体积小、承载的信息量大及不伤眼的优点,因而它成为了现在的主流电子显示设备,其中包括电视、电脑显示器、手机屏幕及各种嵌入式设备的显示器。薄膜晶体管型。

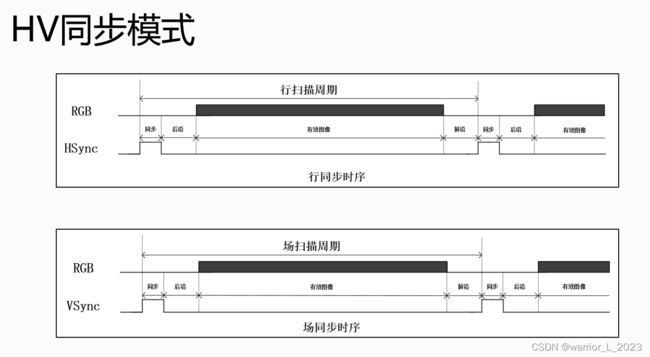

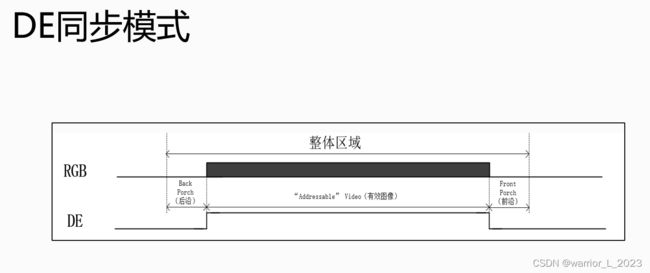

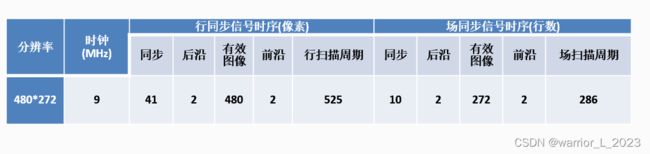

2,两种工作时序:

值得注意的事:

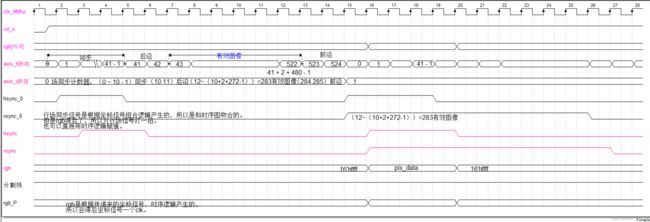

有效图像,与行场同步信号时序上要对齐。需要对行场同步信号打一拍,或者直接使用时序逻辑赋值。在时序图上有更直观的说明。

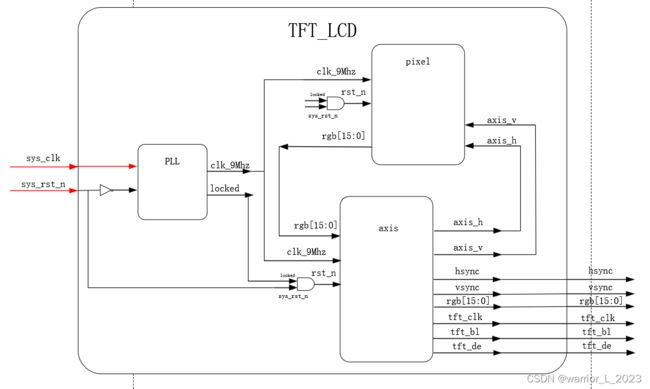

模块框图:

时序图:

代码:

module axis(

input wire clk_9Mhz ,

input wire rst_n ,

input wire [15:0] rgb ,

output reg hsync ,

output reg vsync ,

output reg [9:0] axis_h ,

output reg [8:0] axis_v ,

output wire [15:0] rgb_tft ,

output wire tft_clk ,

output wire tft_bl

);

// wire signal define

wire hsync_0 ;

wire vsync_0 ;

// parameter

parameter TOTAL_H = 10'd525 ,

TOTAL_V = 9'd286 ,

SYNC_H = 10'd41 , // 同步synchronization

SYNC_V = 9'd10 ;

/*****************************************************************************************/

assign hsync_0 = (axis_h >= 0 && axis_h <= (SYNC_H - 1'b1)) ? 1'b1 : 1'b0 ;

assign vsync_0 = (axis_v >= 0 && axis_v <= (SYNC_V - 1'b1)) ? 1'b1 : 1'b0 ;

// output signal

assign tft_clk = clk_9Mhz ;

assign tft_bl = rst_n ;

always @(posedge clk_9Mhz or negedge rst_n) begin

if(~rst_n)

axis_h <= 10'd0 ;

else if(axis_h == TOTAL_H - 1'b1)

axis_h <= 10'd0 ;

else

axis_h <= axis_h + 1'b1 ;

end

always @(posedge clk_9Mhz or negedge rst_n) begin

if(~rst_n)

axis_v <= 9'd0 ;

else if((axis_h == TOTAL_H - 1'b1) && (axis_v == TOTAL_V - 1'b1))

axis_v <= 9'd0 ;

else if(axis_h == TOTAL_H - 1'b1)

axis_v <= axis_v + 1'b1 ;

else

axis_v <= axis_v ;

end

always @(posedge clk_9Mhz or negedge rst_n) begin

if(~rst_n) begin

hsync <= 1'b0 ;

vsync <= 1'b0 ;

end else begin

hsync <= hsync_0 ;

vsync <= vsync_0 ;

end

end

assign rgb_tft = rgb ;

endmodulemodule pixel(

input wire clk_9Mhz ,

input wire rst_n ,

input wire [9:0] axis_h ,

input wire [8:0] axis_v ,

output wire tft_de ,

output reg [15:0] rgb

);

// parameter

parameter TOTAL_H = 10'd525 ,

TOTAL_V = 9'd286 ,

SYNC_H = 10'd41 , // 同步synchronization

SYNC_V = 9'd10 ,

BACK_H = 10'd2 ,

BACK_V = 9'd2 ,

VALI_H = 10'd480 ,

VALI_V = 9'd272 ,

FRON_H = 10'd2 , // 前沿front

FRON_V = 9'd2 ;

parameter RED = 16'hF800 ,

ORANGE = 16'hFC00 ,

YELLOW = 16'hFFe0 ,

GREEN = 16'h07e0 ,

QING = 16'h07FF ,

BLUE = 16'h001F ,

PURPLE = 16'hF81F ,

BLACK = 16'h0000 ,

WHITE = 16'hFFFF ,

GRAY = 16'hD69A ;

// wire signal define

wire valid_rgb ;

reg valid_rgb_reg1 ;

always @(posedge clk_9Mhz or negedge rst_n)

if(~rst_n)

valid_rgb_reg1 <= 1'b0 ;

else

valid_rgb_reg1 <= valid_rgb ;

assign valid_rgb = (axis_h >= (SYNC_H+BACK_H) && (axis_h <= (SYNC_H+BACK_H+VALI_H-1'b1))

&& (axis_v >= (SYNC_V+BACK_V) && (axis_v <= (SYNC_V+BACK_V+VALI_V-1'b1)))) ? 1'b1 : 1'b0 ;

// output signal

always @(posedge clk_9Mhz or negedge rst_n) begin

if(~rst_n)

rgb <= WHITE ;

else if(valid_rgb)begin

if((axis_h >= (SYNC_H+BACK_H)) && (axis_h <= (SYNC_H+BACK_H+VALI_H/10-1'b1)))

rgb <= RED ;

else if((axis_h >= (SYNC_H+BACK_H+VALI_H/10)) && (axis_h <= (SYNC_H+BACK_H+VALI_H/10*2-1'b1)))

rgb <= ORANGE ;

else if((axis_h >= (SYNC_H+BACK_H+VALI_H/10*2)) && (axis_h <= (SYNC_H+BACK_H+VALI_H/10*3-1'b1)))

rgb <= YELLOW ;

else if((axis_h >= (SYNC_H+BACK_H+VALI_H/10*3)) && (axis_h <= (SYNC_H+BACK_H+VALI_H/10*4-1'b1)))

rgb <= GREEN ;

else if((axis_h >= (SYNC_H+BACK_H+VALI_H/10*4)) && (axis_h <= (SYNC_H+BACK_H+VALI_H/10*5-1'b1)))

rgb <= QING ;

else if((axis_h >= (SYNC_H+BACK_H+VALI_H/10*5)) && (axis_h <= (SYNC_H+BACK_H+VALI_H/10*6-1'b1)))

rgb <= BLUE ;

else if((axis_h >= (SYNC_H+BACK_H+VALI_H/10*6)) && (axis_h <= (SYNC_H+BACK_H+VALI_H/10*7-1'b1)))

rgb <= PURPLE ;

else if((axis_h >= (SYNC_H+BACK_H+VALI_H/10*7)) && (axis_h <= (SYNC_H+BACK_H+VALI_H/10*8-1'b1)))

rgb <= BLACK ;

else if((axis_h >= (SYNC_H+BACK_H+VALI_H/10*8)) && (axis_h <= (SYNC_H+BACK_H+VALI_H/10*9-1'b1)))

rgb <= WHITE ;

else if((axis_h >= (SYNC_H+BACK_H+VALI_H/10*9)) && (axis_h <= (SYNC_H+BACK_H+VALI_H-1'b1)))

rgb <= GRAY ;

else

rgb <= WHITE ;

end else

rgb <= WHITE ;

end

assign tft_de = valid_rgb_reg1 ;

endmodule

module top(

input wire sys_clk ,

input wire sys_rst_n ,

output wire tft_de ,

output wire tft_clk ,

output wire tft_bl ,

output wire hsync ,

output wire vsync ,

output wire [15:0] rgb_tft

);

// 例化间连线

wire clk_9Mhz ;

wire rst_n ;

wire [15:0] rgb ;

wire [ 9:0] axis_h ;

wire [ 8:0] axis_v ;

pll_9Mhz pll_9Mhz_insert(

.sys_rst_n ( sys_rst_n ) ,

.areset ( ~sys_rst_n ) ,

.inclk0 ( sys_clk ) ,

.c0 ( clk_9Mhz ) ,

.locked ( rst_n )

);

axis axis_insert(

.clk_9Mhz ( clk_9Mhz ) ,

.rst_n ( rst_n ) ,

.rgb ( rgb ) ,

.hsync ( hsync ) ,

.vsync ( vsync ) ,

.axis_h ( axis_h ) ,

.axis_v ( axis_v ) ,

.tft_clk ( tft_clk ) ,

.tft_bl ( tft_bl ) ,

.rgb_tft ( rgb_tft )

);

pixel pixel_insert(

.clk_9Mhz ( clk_9Mhz ) ,

.rst_n ( rst_n ) ,

.axis_h ( axis_h ) ,

.axis_v ( axis_v ) ,

.tft_de ( tft_de ) ,

.rgb ( rgb )

);

endmodule`timescale 1ns/1ns

module test_top();

reg sys_clk ;

reg sys_rst_n ;

wire hsync ;

wire vsync ;

wire [15:0] rgb_tft ;

wire tft_de ;

wire tft_clk ;

wire tft_bl ;

top top_inst(

.sys_clk ( sys_clk ) ,

.sys_rst_n ( sys_rst_n ) ,

.tft_de ( tft_de ) ,

.tft_clk ( tft_clk ) ,

.tft_bl ( tft_bl ) ,

.hsync ( hsync ) ,

.vsync ( vsync ) ,

.rgb_tft ( rgb_tft )

);

parameter CYCLE = 20 ;

initial begin

sys_clk = 1'b1 ;

sys_rst_n = 1'b0 ;

#(CYCLE) ;

sys_rst_n = 1'b1 ;

end

always #(CYCLE / 2) sys_clk = ~sys_clk ;

endmodule仿真波形: