foc配置篇——ADC注入组使用定时器触发采样的配置

foc配置篇——ADC注入组使用定时器触发采样的配置

foc驱动板都会用到电流采样,本篇就针对三电阻低测采样来讲一讲如何配置ADC。

一、基本原理

在此之前,或许大家使用ADC都是建立一个大数组,然后DMA无脑开着将数据搬到数组里,等到要用到时候就取出来做一个均值滤波。

这种方法用在foc电流采样上行不行呢?答案是看情况,如果你的硬件用的是低采,这种方法是行不通的。因为低采的采样电阻在下桥臂到地之间,当下桥臂关闭时,电流是不能通过下桥臂流向地的,此时采样电阻自然也不会有电流经过(除了漏电流之类的)。因此,低采就是要当下桥臂开启的时候采样。

如果我们还用无脑采,采样点在任意一个地方都是有可能的,可能采在下桥臂关闭的时候,也可能采在mos开启关闭的瞬间,具体在哪我们是不知道。因此我们就需要触发采样,必须非常明确地在下桥臂开启的时候采样。

二、CubeMX配置

下面就以最常见的STM32F405RG为例:

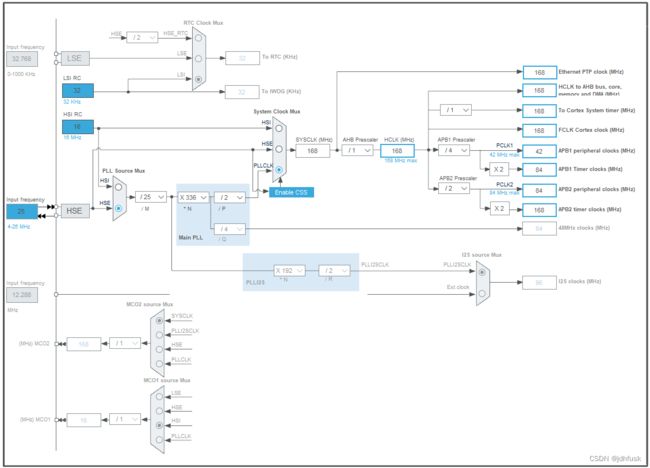

1、首先是正常配置时钟树,将主频配置为168M。

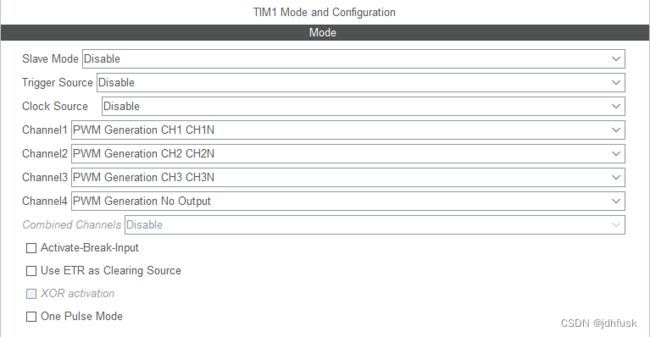

2、配置TIM1输出六路24KHz的PWM信号

(1)

解释:

- 这里的通道四用作ADC的触发源,一般情况不需要它输出,不过初学时为了方便调试及理解,也可以配置成 PWM Generation CH4。但一定要看清楚是 PWM Generation 开头的,切记切记不要选成 Output Compare 开头的!!!

(2)

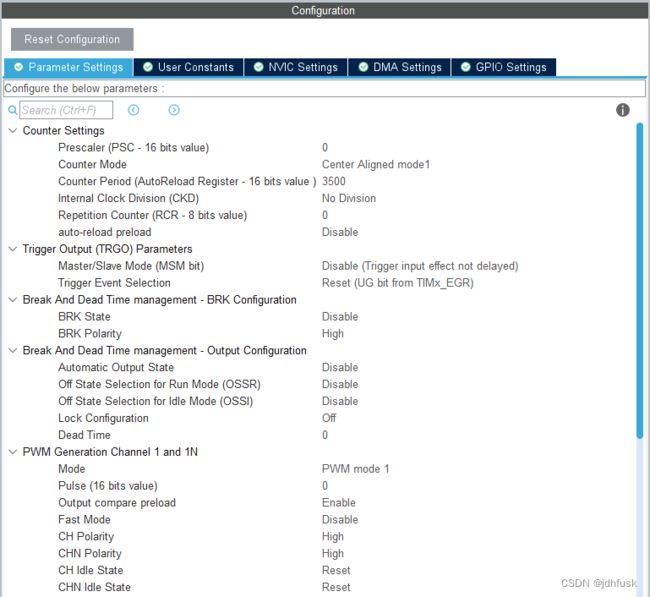

说明:

- Counter Settings

- Presclar :预分配系数,为了不损失定时器的分辨率,一般都设为0

- Counter Mode :这里一定要选择中心对齐模式,至于是123无所谓,因为这个只会影响到捕获比较中断,而这个中断我们用不到。

- Counter Period :装载值,计算公式为 定时器频率/PWM频率/2 = 168000000/24000/2 = 3500 。中心对齐模式的装载值需要除以2,但不需要减1。

其余全部默认即可。

(3)这里可以使能溢出中断,然后在中断里翻转io便于调试。

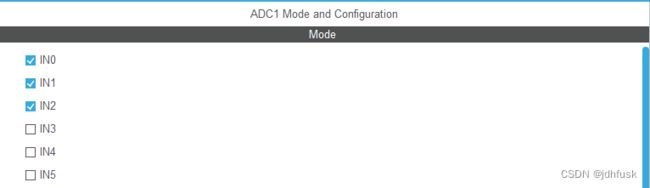

3、配置ADC

(1)根据自己板子的硬件连接去选择ADC通道,这里假设连接通道0、1、2

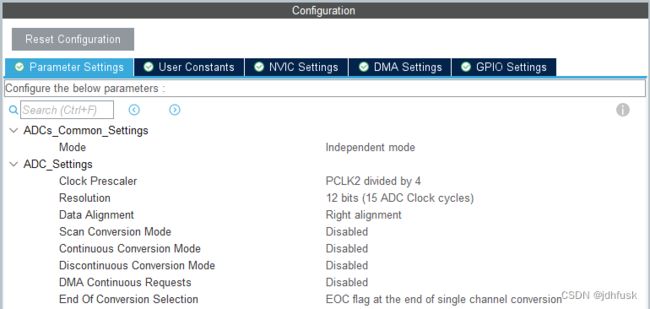

(2)ADC基本配置

全部默认即可

(3)ADC规则组的配置

全部默认即可。不过这里特别说明一下,使用CubeMX配置ADC,即使用不到规则组,它也会强制你用一个规则通道。这里可以随便选择一个,只要后续我们不开启规则转换,这个通道也不会被规则组影响。或者实在是不放心的,可以选个内部温度通道。

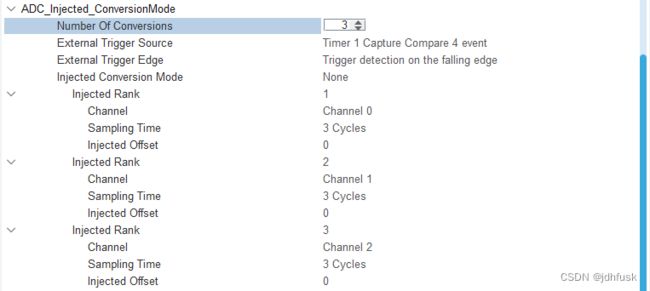

(4)ADC注入组的配置

说明:

- Number Of Conversions :使用到注入组的通道个数。默认是0的,需要我们加到3,然后点击旁边空白地方一下,就会自动多出下面三个 Injected Rank 。

- External Trigger Source :外部触发源,这里我们便使用前边说的定时器1的通道四作为触发源。

- External Trigger Edge :外部触发极性。这个极性怎么去理解呢?我们可以想象一下定时器1的通道四输出pwm,而pwm是有上升沿和下降沿的。我们这里选择下降沿,意思就是在通道4输出pwm的下降沿的瞬间,触发ADC进行AD转换。(这个后边会细讲)

- Injected Conversion Mode :这个默认即可。

- Injected Rank :这个就是注入序列,一旦ADC开始注入转换,就会按照Rank1-2-3-4的顺序依次进行采样,每个rank只能选择一个对应的通道,一个通道可以被多个rank选择。而在本例中,一旦定时器1通道4的pwm产生下降沿,ADC1就会对通道0进行一次采样,然后对通道1采样,最后对通道2采样。三个序列采样完成后,注入组会停下来等待下一个下降沿来临。

- Sampling Time :采样时间,因为foc电流采样是一个分秒必争的过程,所以采样时间尽可能的要短,这里选择3周期,最大也不要大于15周期。

- Injected Offset :默认即可。

4、生成工程

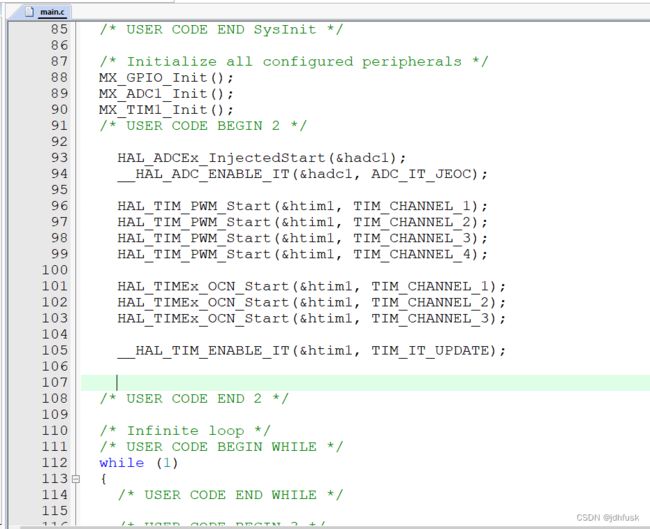

生成工程后,在main函数的这个地方添加如下代码:

HAL_ADCEx_InjectedStart(&hadc1);

__HAL_ADC_ENABLE_IT(&hadc1, ADC_IT_JEOC);

HAL_TIM_PWM_Start(&htim1, TIM_CHANNEL_1);

HAL_TIM_PWM_Start(&htim1, TIM_CHANNEL_2);

HAL_TIM_PWM_Start(&htim1, TIM_CHANNEL_3);

HAL_TIM_PWM_Start(&htim1, TIM_CHANNEL_4);

HAL_TIMEx_OCN_Start(&htim1, TIM_CHANNEL_1);

HAL_TIMEx_OCN_Start(&htim1, TIM_CHANNEL_2);

HAL_TIMEx_OCN_Start(&htim1, TIM_CHANNEL_3);

__HAL_TIM_ENABLE_IT(&htim1, TIM_IT_UPDATE);

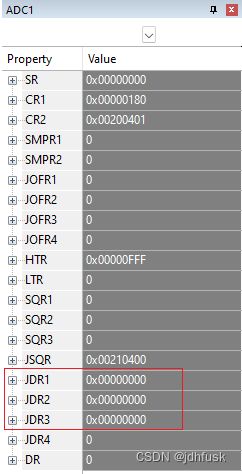

然后编译,点击仿真按钮,下载并仿真。再打开ADC1的相关寄存器:

我们发现注入组相关的几个数据寄存器都为0,是不是没有开启转换?

没错是的。大家还记得之前提到的通道四pwm的下降沿吗?我们现在定时器1的CCR4的值为0,也就是它一直都在输出低电平,自然就没有下降沿,没有下降沿ADC也不会被触发。于是我们现在给定时器1的CCR4寄存器随便赋个值(1-3499的任意值),然后再看ADC1的这几个寄存器:

可以看到,它们已经有数值了,而且不断地在跳动、更新。如果我们将这个通道连接到3.3V,数据会变成4095左右;连接到地,数值会变成0左右。到了这里,我们的ADC可以说已经配置成功了。

三、调试

前文虽然调通了ADC注入组触发采样,但还不能直接应用于低侧采样,因为还有一个重要的东西没讲,那就是触发位置。触发位置的设置是触发采样的灵魂所在,触发位置设置的不对,触发采跟无脑采也就没什么两样了。

1、什么是触发位置

前文铺垫的已经够多了,现在便让各位直观地感受一下什么叫触发位置。

我们使用逻辑分析仪连接单片机的三个IO口,连接关系如下:

通道0 -> 定时器1中断函数中翻转IO

通道1 -> 定时器1的pwm通道1(非互补通道)

通道2 -> 定时器1的pwm通道4

通道3 -> ADC1中断函数中翻转IO

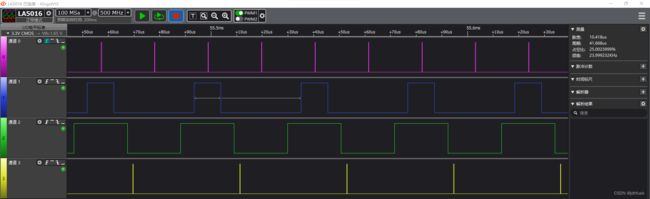

然后我们将pwm通道1的占空比设为25%,pwm通道4的占空比设为50%,测一组波形:

通过通道1(蓝色)的波形,我们可以看到此时定时器1的通道1输出的pwm的频率为24KHz左右,占空比为百分之25左右,与我们的设置相符。

通道2(绿色)的波形则是定时器1的通道4输出的pwm,我们可以发现在它的下降沿后的一段时间,通道3(黄色)产生了一个脉冲,也就是进入了ADC注入中断,这代表着ADC已经完成了一组采样。而这段延时,由ADC采集三个通道的采样时间和响应中断的延时组成,而ADC单次采样时间我们可以从手册中找到。

通道0(紫色)的波形反映了定时器1进入中断的频率,我们可以发现这个频率是48KHz,比pwm频率快一倍,这是为什么?因为我们用到了中心对齐模式,这个模式下定时器上溢和下溢都会进入一次中断(和中心对齐模式123没有关系)。如果我们希望进入中断的频率和pwm同频,我们就需要给重复计数寄存器RCR赋值,值为1即同频。(但要注意,定时器是上溢进入中断还是下溢进入中断可能会不确定,与我们写入RCR寄存器的时机有关系)

2、低采的触发位置

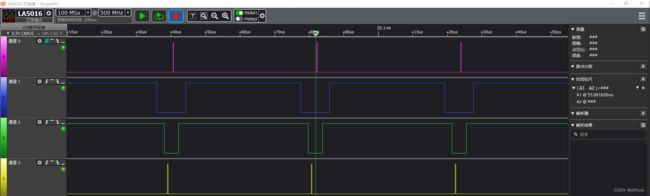

低采是触发位置是在ABC三相pwm同时处于低电平的时刻,也就是定时器三个通道(正常通道不是互补通道)输出的pwm同时处于低电平的时刻。

那么什么时候会出现三个pwm同时为低电平?

如图所示,中间蓝色竖线的地方就是三相都为低电平的地方(前提是三相占空比都小于100%)。三相中占空比最大的相的低电平时间,就是留给我们ADC采样的时间。如果某一相的占空比过大,留给我们的时间已经小于采样时间了,那ADC可能会无法采样到电流,或者在mos开启关闭的附近时间采样,这个时候会采到非常严重的尖峰,此时电流采样已经无法正常进行。因此,低采需要限制最大占空比。

那么低采的触发位置设置在什么地方比较合理?我们再看上图,假如定时器通道1(蓝色波形)是三相中占空比最大的那个,那么我们的采样位置可以放在它下降沿处靠右一点的位置,就比如图中的绿色波形。

那么,在我们前面配置都一样的前提下,CCR4寄存器的值设为多少合适?因为我们的装载值是3500,如果我们设为3500,通道四就会一直处于高电平,没有下降沿也就无法触发ADC。因此我们可以设置成比3500小一点的数,比如3450,但前提是三相最大的装载值不会超过3400左右。不过这里只是打个比方,具体还是要根据自己手上的硬件去细调。

问题解答:

1、为什么一定要用注入组,用规则组加触发行不行?

这样也是可以的,关键在于触发而非规则还是注入。不过规则组仅有一个数据寄存器,因此多通道采集还需要DMA的配合。而注入组的四个通道都有独立的数据寄存器,要用的时候直接从寄存器里面取即可。同时,注入组可以打断规则组,因此可以配置规则组进行一些温度采样,注入组进行电流采样,合理分配。所以,在ADC支持注入组的情况下,强烈建议使用注入组进行电流采样。

2、可不可以多个ADC使用同一个触发源?

可以,而且更加合理。虽然我们的ADC采样时间很短(3个通道加起来可能不过5us,不过前提是采样周期为3周期),但是占空比高的时候留给我们采样的时间也很短。如果使用3个ADC同时触发,可以一次采样时间采完三相电流。而且,虽然连续采样的间隔很短,但仍然是有时间差的,这样我们采集到的三相电流就不是同一时刻的,这一点在追求细节的时候是不可忽视的。