DLL和PLL

在芯片设计中时钟网络的生成常用两个器件分别是DLL(Delay-locked loop)和PLL(Phase-locked loop)。

这两个期间都能完成 分频,倍频和相位调整的功能。但PLL的分频和倍频范围大,成本高。DLL有一定的分频,倍频能力,主要是用来做时钟相位调整。

1.DLL

结构一

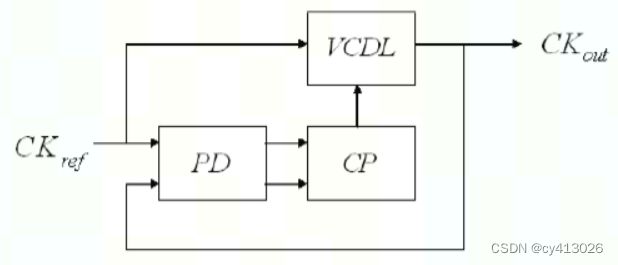

DLL 的环路结构分两种,一种是输入参考时钟与 DLL 的输出时钟进行比较, 这种结构的 DLL 通常使用于频率综合,时钟产生与信号同步应用中。如下图所示:

结构二

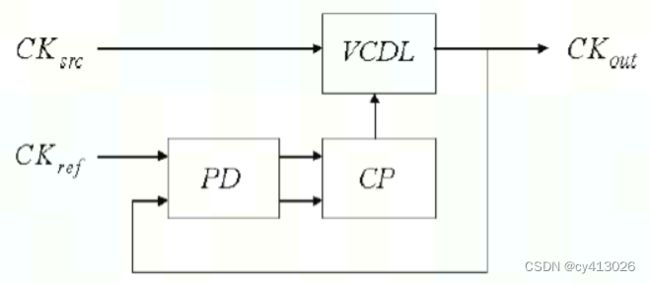

一种是输入参考时钟与不相关的时钟进行比较,这种 DLL 需要 2 个输入时钟,该结构主要应用于时钟恢复电路中。如下图所示:

从上图中可以看出DLL的主要组成单元有:

PD:phase detector 鉴相器

CP:charge pump 电荷泵

VCDL:Voltage-Controlled Delay Line 压控延迟线

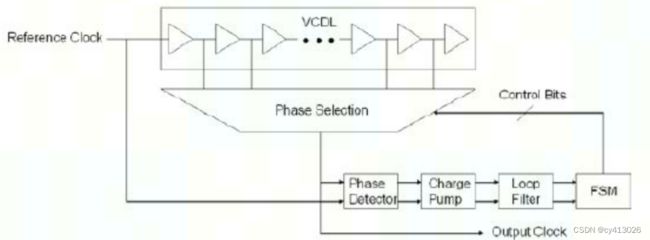

DLL可以分为数字DLL和模拟DLL,下图给出了简单数字DLL的结构框图。

其中VCDL是用的clk buff或者反相器【如果使用反相器抽头应该在每两个反相器的输出端】设一个clk buff或者两个反相器的延迟为![]() 。这里的clk buff或反相器的延迟

。这里的clk buff或反相器的延迟![]() 基本是不可调的,那么只能选择串联的clkbuff级数的办法调节延迟。假设clk周期为4

基本是不可调的,那么只能选择串联的clkbuff级数的办法调节延迟。假设clk周期为4![]() ,那么refclk经过4级clkBuff延迟得到和refclk同向的时钟被phase selection选出来,经过PD检测到相位相同,到达锁定状态。此时4级clkBuff的输出分别是refclk的90°,180°,270°,360°移相时钟。

,那么refclk经过4级clkBuff延迟得到和refclk同向的时钟被phase selection选出来,经过PD检测到相位相同,到达锁定状态。此时4级clkBuff的输出分别是refclk的90°,180°,270°,360°移相时钟。

如果refclk是4.8![]() ,那么选择与refclk最近的相位送近PD,就是5级clkbuff的输出。此时每一级输出相位偏差是360°/4.8=75°。这种DLL对不同频率的refclk移相精度差别太大。除非refclk的周期远大于

,那么选择与refclk最近的相位送近PD,就是5级clkbuff的输出。此时每一级输出相位偏差是360°/4.8=75°。这种DLL对不同频率的refclk移相精度差别太大。除非refclk的周期远大于![]() 。所以这种结构限制性较大。一般情况clkbuff的delay在30个ps一下,如果refclk在100MHz左右,

。所以这种结构限制性较大。一般情况clkbuff的delay在30个ps一下,如果refclk在100MHz左右,![]() =20ps。那么移相精度就在20ps*360°/10ns=0.72°

=20ps。那么移相精度就在20ps*360°/10ns=0.72°

soc设计中基本没见过上面的DLL使用,这里仅作为一个示例。用clkBuff倒是常常出现在后端做clkTree的过程中。在时钟恢复电路和高速DDR接口做时钟对齐的电路常用更复杂设计的DLL或PLL。

下面分节介绍一下DLL三个主要组成部分。

1.1 PD

鉴相器的作用就是检测从 VCDL 输出的信号与时钟参考信号的相位差,把相位差的信息传递给下级电路。

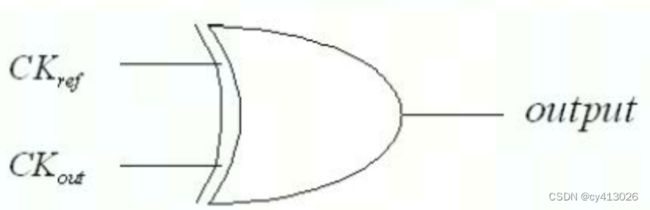

PD有数字的也有模拟的,一个简单的异或门就可以是一个鉴相器,对output的输出积分在相位差0-180°时积分逐渐增大,180°到360°又逐渐减少,当clk(out)和clk(ref)相位相同,并差一个周期时,异或输出为0。

复杂的PD不在这里详细介绍。可参考:

TODO

1.1.1 PD/PF/PFD

有一个说法来区别鉴频器和鉴相器。说鉴频器只能保证频率锁定,但是可能锁定在随机的相位差上面。鉴相器是可以固定锁定相位差的。

还有鉴频鉴相器,先进行频率锁定在进行相位锁定。鉴相器同时锁定频率和相位;鉴频器只锁定频率。

对于DLL来说,如果用在时钟恢复电路是需要一定的频率跟踪能力的。最开始给出的普通数字DLL结构是不具有频率跟踪能力的,或者说DLL的第一种结构是不需要频率跟踪能力