Solid State Disk(SSD)结构细分+高级指令+并行优化

1、结构

如图2所示,SSD主要由主机接口、SSD控制器和闪存芯片阵列三部分组成。主机接口支持主机系统和SSD控制器之间的通信,并维护设备级I/O队列,HIL以循环方式从主机队列中获取I/O请求,插入设备队列中。SSD控制器,通常包含一个嵌入式处理器和DRAM,负责处理I/O请求和管理SSD资源,通过执行一组flash翻译层(FTL)功能。、地址转换、垃圾收集和损耗均衡。SSD控制器还通过闪存芯片控制器与闪存芯片阵列通信。由多个闪存芯片组成的闪存芯片阵列通过通道连接到闪存控制器,提供物理存储容量。闪存芯片(存在一个命令队列,并行派发给每个plane)由die组成,每个die都有自己的地址寄存器和命令寄存器。die被进一步划分为plane(可以多个plane串行进行缓存寄存器的数据传输,并行刷入介质中)。在一个plane内,页(用于读操作和编程(写)操作的原子单元)被分组成块,组成用于擦除操作的原子单元。重要的是,页面读取和编程操作可以跨通道、chip、die和plane进行条带处理,以便并行处理。

SSD内部存储空间是闪存阵列,一般多个通道,每个通道上有多个闪存芯片,每个闪存芯片有多个DIE(并行单元,LUN,每个die中一次执行一个命令),每个DIE有多个Plane,每个Plane有多个block,每个block有多个page,每个page对应一个wordline。

2、Block Management and Page Management

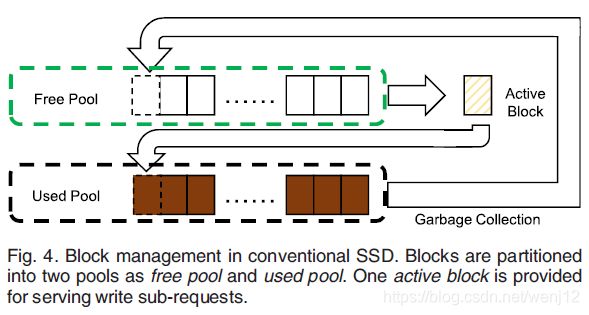

在一个plane内,块被划分为两个池,即空闲池和使用池,和一个活动块,如图4所示。具体来说,擦除的块(其中的所有页面都是空闲的)属于空闲池,而完全编程的块(其中的所有页面都是编程的)属于使用的池。此外,每个平面维护一个活动块,它通常包含已编程页面和空闲页面,用于服务后续页面大小的写子请求。当活动块中的所有页面都被编程后,该块将被停用并插入到使用的池中,同时从空闲池中获得另一个块并作为新的活动块被激活。另一方面,一旦空闲池大小低于GC(垃圾收集)阈值,就会触发GC操作,并将块从使用池回收到空闲池。根据这一plane内块管理和块内页面内管理,在页面分配时,目标plane由PLAlloc原语决定后,实际上只有一个候选页面从活动块中的空白页中被BLAlloc原语选择。在每个平面上设计一个单独的候选页面可以显著地简化块和页面的管理,但是,这样做的代价是降低了分配所需页面类型的灵活性。

3、芯片(chip)—晶圆(die)—分组(plane)—块(block)—页(page)

芯片(chip)

是最外层结构,通常,芯片层拥有一套完整的外围电路,外部信号线。在很多时候,闪存厂商为了节约成本和空间,将多个芯片在物理上叠加起来,叠加在一起的每个芯片有一个独立的片选信号和一个独立的工作状态信号线,外部看来这些芯片就是一个整体,被称之为颗粒(package)。在一个封装中的所有芯片chip共享相同的8/16位I/O总线的封装,但有单独的芯片启用和就绪/忙碌控制信号。因为颗粒是多个芯片在物理上的几何堆砌,并无逻辑上的意义,所以不存在颗粒这个层次。

晶圆(die)

是闪存的第二层结构,晶圆层次的出现也是因为闪存厂商出于节约成本和空间的目的,将多个晶圆组合在一起,共用一套外围电路和外部信号线,但是为了执行高级命令(将在后面详细介绍,闪存厂商提供的高效的读、写、擦除方法,是对普通读、写、擦除命令的升级),每个晶圆有一个内部的工作状态信号线(Ready/Busy),与芯片层的工作状态信号线不同的是,用户无法看到内部的工作状态信号线,它存在于芯片内部,用于查询每个晶圆的当前状态。

分组(plane)

是闪存中关键层次,为了提高闪存的读写速度,在每个分组中设置了一个或者多个寄存器(目前,三星的闪存产品提供一个寄存器,称之为数据寄存器—data register;美光的闪存产品提供两个寄存器,称之为数据寄存器—data register 和缓存寄存器—cache register)。数据被暂存在这个寄存器中,通过I/O 信号线逐步传入或传出。

块(block)

是闪存中擦除操作的基本单元,通常,一个分组中有固定数量的物理块,在三星的一款产品中,一个分组中有2048 个物理块。

页(page)

是闪存中读写操作的基本单元,通常,一个物理块内有固定数量的物理页,在同样一款三星的产品中,一个物理块中有64 个物理页。值得注意的是,分组中的寄存器大小就是一个物理页的大小,这是因为分组中的寄存器被用作读写操作时的缓存,所以寄存器的大小应该被设置成与闪存的读写操作单元大小一样。图1.2 是一个页的结构示意图,在这个图中,假设页大小为2KB,其中包括正常存储空间和一个额外存储空间。额外存储空间是一个特殊的空间,它用来保存正常存储空间中数据的ECC 纠错码,逻辑页号等元数据。通常每512 字节的正常存储空间配备16 字节的额外存储空间。除此之外,部分闪存芯片存在子页的层次,这个层次是依据传统的块设备特点设计的。如图1.2 一个页中包括4 个子页。在传统块设备中,一个扇区大小为512 字节,所以子页的大小也为512 字节。

闪存芯片除了具有以上层次结构,它在使用过程中还存在两个主要特点:

(1)先擦后写;(2)擦写次数有限。先擦后写是因为闪存中的写操作(program),也称作编程操作,能将每个存储位上的1 变成0,但是不能将0 变成1。闪存的存储介质是浮栅场效应管,写、擦除操作需要通过半导体层向浮栅注入或者排出电子进行信息的保存,电子多次通过半导体之后将击穿半导体,这导致闪存的写、擦除次数有限。

4、基本指令与高级指令

基本命令就是通常所说的读、写、擦除。主要的高级命令包括三种:内部数据迁移(copyback)、多分组操作(multi-plane)、交错操作(interleave)

读操作:读取闪存中的数据。完整的读操作分成三个部分:发送命令,访问介质,传输数据。写操作:将数据存储到闪存中

。完整的写操作分成三个部分,发送命令,传输数据,访问介质。在块内,页面必须按照页面地址的递增顺序连续编程,随机页地址编程是被禁止的。我们称这个限制为(a)。

擦除操作:擦除闪存中的某个物理块。

数据内部迁移(copyback):在一个分组内部,将一个物理页的数据移动到同一个分组内其他物理页。它的操作过程是:首先从源物理页中将数据读出到这个分组的寄存器,然后从这个寄存器写回到位于同一个分组的目标物理页。这个高级命令使得一次数据迁移在分组内部完成,没有占用外部数据总线。源页和目标页必须具有相同的芯片chip、芯片die和plane地址。源页和目标页的地址必须都是奇数或偶数。如图4所示,一个copy-back操作只能将数据从页面0移动到页面2,或者从页面1移动到页面3,等等。禁止将数据从第0页移动到第1页或第3页。我们称这个限制为(b)。(同一plane中,可以是不同块,之间的页面移动)盲目地使用copy-back命令会导致几乎一半的copy-back操作在所有工作负载下都使一个额外的页面失效,导致更多的GC操作,影响请求响应。为了明智地使用copy-back命令来最小化无效页面的数量,我们建议只在源页面和目标页面的地址具有相同奇偶的情况下使用该命令。

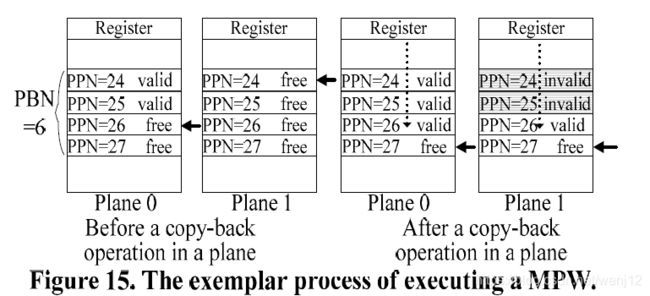

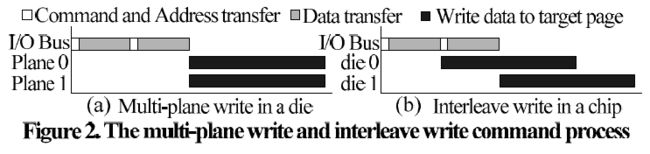

多分组操作(multi-plane):一个晶圆上的多个分组同时进行多个读、写、擦除操作,它包括三个命令:多分组读(multi-plane read)、多分组写(multi-plane write)、多分组擦除(multi-plane erase)。多分组读的操作过程是:同一个晶圆上的多个分组同时将数据从介质中读出到该分组的寄存器中,再通过外部数据总线,依次将每个分组的寄存器中的数据传输出去。多分组写的操作过程是:依次将数据发送到同一个晶圆的多个分组的寄存器上,然后将这些寄存器中的数据同时写到介质中。多分组擦除的操作过程是:依次发送擦除命令给同一个晶圆的多个分组,然后这些分组同时执行擦除操作。多分组操作只消耗了一次读介质、写介质、擦除介质的时间,而完成了多次读、写、擦除操作。多平面命令可在同一die的所有plane中激活多个读取、编程或擦除操作。它只花费一次读、写或擦除操作的时间,同时执行多个这样的操作,如图2 (a)所示。执行多平面读/写操作的页必须具有相同的芯片chip、芯片die、块和页地址(plane不同)。执行多平面擦除操作的块必须具有相同的芯片chip、芯片die和块地址(plane不同)。如图4所示,使用多平面读写操作,只能同时读写同一die平面0的第1页和平面1的第1页。禁止使用多平面读写操作从平面0读取/写入页1和平面1读取/写入页3。我们称这个限制为©。(等不同命令和不同数据都传到die完成后,所有plane一起工作)(plane级并发)(要么都进行读,要么都写,要么都擦)图15演示了MPW操作。图中显示了同一die的两个不同平面,平面0和面1。平面0中的下一个可用页面的页地址是26,而平面1中的页地址是24。当在这两个平面上使用MPW命令时,平面1中的PPN =24和PPN =25将失效。因此,在本例中,执行MPW命令会使两个空闲页面失效(并浪费)。

交错操作(interleave):根据一个芯片由多个晶圆组成的结构特点,利用流水的方式,依次操作每个晶圆的读、写、擦除。在交错操作中,当一个晶圆处于介质访问阶段时,数据总线向同一个芯片上的另一个晶圆发送数据,当数据传输完成后,该晶圆进入介质访问阶段,然后数据总线再向同一个芯片上的第三个晶圆传输数据,如此循环往复,不同晶圆通过轮流使用外部总线,而隐藏对介质的操作过程,最终在较短时间内完成多次读写操作。Interleave指令同时在同一芯片chip的不同die上执行多个页读、页写、块擦除和multi-plane读/写/擦除操作。交错命令与J. Seol等提到的交错操作不同。前者是在同一chip的不同die之间执行的flash命令,而后者是在同一通道的不同chip之间执行的flash命令。交错写命interleave write如图2 (b)所示。除了同时操作的页面必须属于同一chip上的不同die的限制外,使用交错写命令没有其他限制。(die为命令执行单元,每个die自己的命令和数据传完后可以立马开始工作,不同die可以同时工作。)(die级并发)

所有高级命令可以组合使用,例如多分组操作和交错操作组合在一起形成:交错多分组操作,它是利用交错操作流水式地将数据传输到多个晶圆,使多个晶圆同时执行多分组操作。

从图中可以看到,在固态盘中,存在三种主要部件:固态盘控制器芯片、闪存芯片、内存芯片。在少数低端固态盘中,为了节约成本通常利用控制器内部的存储空间而将内存芯片省去。固态盘控制器是整个固态盘的核心,所有的软件算法全部由控制器执行。固态盘控制器中有很多逻辑单元模块,包括微处理器、主机接口控制器、内存控制器、DMA、多个相互独立的通道控制器等。微控制器是固态盘的计算处理单元;主机接口控制器负责从外部接口获取读写请求,然后传递给固态盘控制器内的其它模块;内存控制器是用来控制固态盘内的所有内存芯片;DMA 是在固态盘内部用来控制内存芯片数据与通道控制器FIFO 数据直接存取操作的控制单元;通道控制器用来控制一系列的闪存芯片。通常在固态盘中,为了提高性能和存储容量,存在多个通道,每个通道均有一个独立的通道控制器。在每个通道控制器中有一个数据缓存区(FIFO),这个部分在DMA 的控制下,与内存之间进行快速的数据交换。

6、完全覆盖更新与非完全覆盖更新

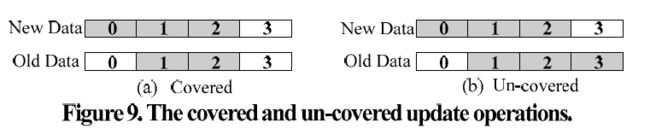

逻辑页被写入闪存内存有两种情况,逻辑页被第一次写入,逻辑页被重写或更新在闪存内存中。更新操作可能导致两种类型的SSD内部数据移动,这取决于页的新数据是完全重叠(称为覆盖),还是部分重叠(称为未覆盖)页的旧数据。

图9显示了被覆盖(图9(a))和未被覆盖(图9(b))的页面更新情况,假设页面大小为2KB(即相当于4个扇区),其中页面的阴影扇区表示有效数据,而非阴影扇区表示无效数据。在覆盖更新的情况下,如图9(a)所示,新数据(扇区0-2)被写入到新的物理页,使包含逻辑页的旧数据(扇区1-2)的旧物理页失效,并修改逻辑页的映射信息。un-covered的更新,如图9所示(b),旧的数据被读出(部门3)后结合新数据(0 - 2)的逻辑页,然后合并后的数据(部门0 - 3)写入一个新的物理页面,使包含旧数据的旧的物理页面无效并且修改这个逻辑的映射信息页面。(对于旧数据页,只需读出未更新的页即可)未覆盖的操作比覆盖的更新操作需要多一个flash读操作,这可能对请求的响应时间有负面影响。

7、四个并行级别

优先级NOTE:

1.严格地说,每个读/写操作包括两个步骤,(1)数据传输和(2)从目标页page到平面plane数据寄存器的数据读写。并行性的目的是重叠或管道这两个步骤。芯片级chip并行、die级并行和plane级并行在共享同一channel总线的同一channel上执行。因此,这三个并行级别只能重叠或流水线操作的步骤(2)。另一方面,channel级并行不仅与步骤(2)重叠,还与操作的步骤(1)重叠。因此,在并行度的四个级别中,通道级并行度应该被给予最高的优先级。(命令和地址寄存器在die,数据寄存器在plane)

2.芯片chip级并行使得多个芯片chip繁忙。当通道上的芯片chip正在服务请求时,在这些忙碌的芯片chip返回空闲状态之前无法服务后续请求。另一方面,die级并行和plane级并行只涉及到一个芯片chip,这使得它们的优先级高于芯片chip级并行。(同一芯片chip在同一时刻只能服务一个请求,读/写/擦/高级指令)

3.如图19所示,为了服务一个四页写请求,在利用平面级并行性时执行两个MPW操作。但是,要利用die级并行性,需要执行两个交错写命令。从图中可以看出,后者要优于前者。而且,利用平面级并行性需要执行MPW/MPR命令,这通常会使空闲页面失效。相反,利用die级并行性所需的交错命令没有这样的缺点。因此,die级并行应该比平面级并行具有更高的优先级。

见解9:SSD中并行度的最佳优先级顺序应该是(1)通道级并行度,(2)die级并行度,(3)平面级并行度,和(4)芯片级并行度。

-

通道之间的并行:每个通道拥有独立的通道控制器,当两个逻辑页(a,b)需要写到固态盘时,利用多通道的结构,将逻辑页a 发送到通道0,将逻辑页b 发送到通道1,这样通道0 和通道1 同时服务两个逻辑页

-

芯片之间的并行:一个通道上存在多个芯片,每个芯片存在独立的片选信号,芯片之间读写介质的过程也是可以相互独立的,但是这些芯片属于同一个通道,共用同一个数据通道。例如,将逻辑页a 发送到芯片0 上之后,再将逻辑页b 发送到芯片1 上,当两个逻辑页的数据依次传输到两个芯片后,两个逻辑页的数据写到各自闪存介质的过程是相互独立的,这就是芯片之间的并行。

-

晶圆之间的并行:交错操作命令(interleave)可以将逻辑页a 的数据写到晶圆0,逻辑页b 的数据写到同一个芯片的晶圆1,两个写入介质的过程交错进行,这是晶圆之间的并行

-

分组之间的并行:多分组操作命令(multi-plane)将逻辑页a的数据写到分组0,逻辑页b 的数据写到同一个晶圆的分组1,写入介质的过程同时进行,这就是分组之间的并行。

参考文献:

2020-TPDS-Improving Overall Performance of TLC SSD by Exploiting Dissimilarity of Flash Pages

2012-胡洋-高性能固态盘的多级并行性及算法研究