【FPGA】Vivado软件使用教程

目录

一、创建Vivado工程

二、创建Verilog HDL文件

三、添加管脚约束

四、时序约束

五、生成BIT文件

六、Vivido仿真

七、上板再补充

一、创建Vivado工程

1、启动Vivado,在Vivado开发环境里点击“Create Project”,创建新工程。

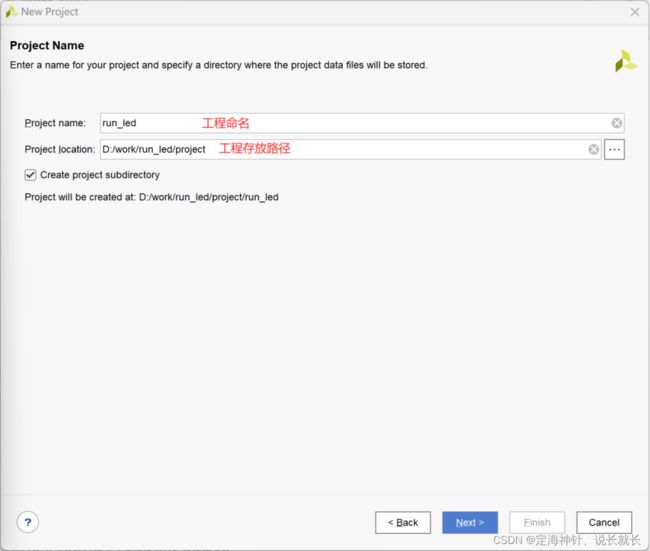

2、弹出窗口点击“Next”,在弹出的窗口中输入工程名和存放的工程路径,工程名在这里我取的run_led;工程路径不能含有中文字符,路径名也不宜太长。

3、点击“Next”后,在后面弹出的窗口,在工程类型中选择“RTL Project”;目标语言Target language中选择“Verilog”。在添加文件窗口中直接点击“Next”,不添加任何文件。

在器件选择页面中根据自己使用的FPGA开发板进行选择。

点击“Finish”完成工程创建。

二、创建Verilog HDL文件

1、工程创建完成后随之进入到Vivido软件界面。点击PROJECT MANAGER 下的Add Sources(或者快捷键Alt+A)。

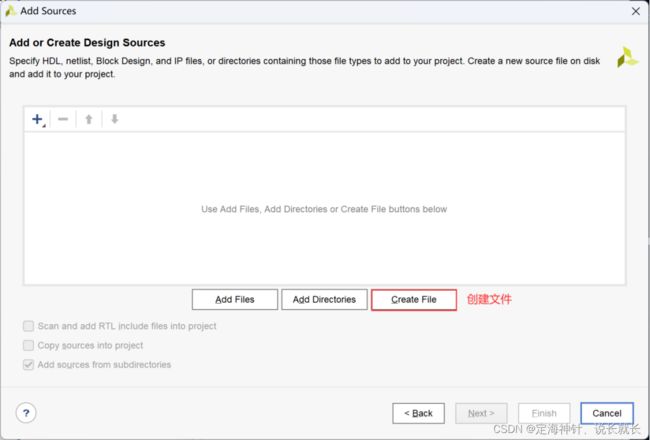

2、 选择“Add or create design sources”添加或创建设计源文件,点击“Next”。

3、选择创建文件“Create File”。

4、文件命名为run_led,点击“OK”。再点击“Finish”完成“run_led.v”文件的添加。

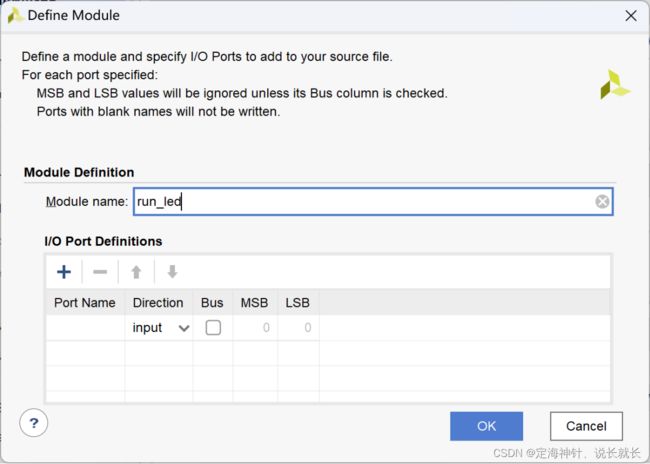

5、在弹出的Define Module模块定义中,可以指定“run_led.v”文件的模块名称,默认不变为“run_led”。

6、双击“run_led.v”打开文件,可以编辑代码。

编写好代码保存。

代码是简单的点灯。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/03/28 17:54:01

// Design Name:

// Module Name: run_led

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module run_led(

input clk ,

input rst_n,

output reg led

);

//参数定义

reg [11:0] cnt ;

wire add_cnt;

wire end_cnt;

//参数设置

parameter TIME_1S = 20 ;//1S亮灭

//计数器

always@(posedge clk or negedge rst_n)begin

if(~rst_n)begin

cnt <= 0;

end

else if(add_cnt)begin

if(end_cnt)begin

cnt <= 0;

end

else begin

cnt <= cnt + 1 ;

end

end

end

assign add_cnt = 1;

assign end_cnt = add_cnt & (cnt == TIME_1S - 1);

//流水灯

always @(posedge clk or negedge rst_n) begin

if(~rst_n)begin

led <= 0;

end

else if(end_cnt)begin

led <= ~led;

end

else begin

led <= led ;

end

end

endmodule三、添加管脚约束

Vivado使用的约束文件格式是xdc文件。管脚约束是对“run_led.v”程序中的输入输出端口分配到FPGA的真实管脚上。

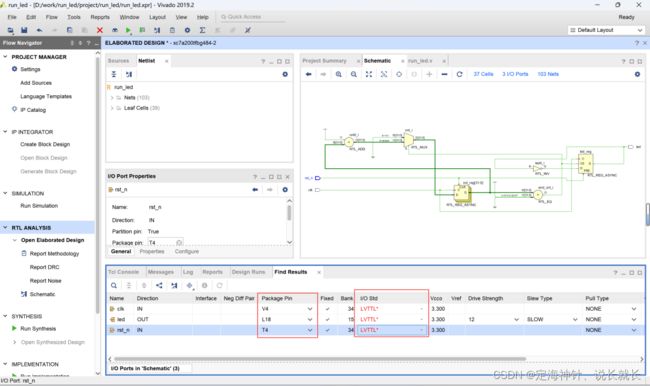

1、点击“Open Elaborated Design”打开详细设计。在弹出的窗口点击“OK”。

2、在菜单中选择“Window”中的“I/O Ports”。

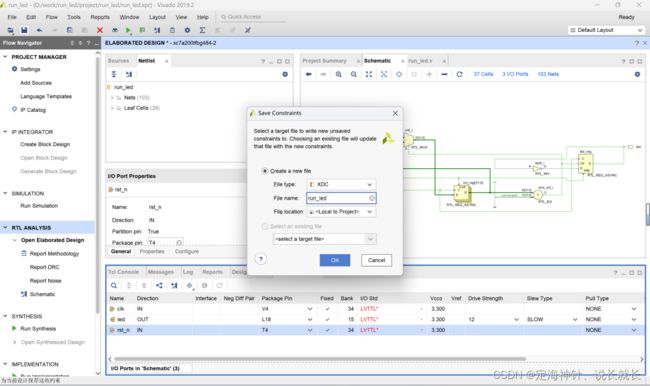

3、在弹出的I/O Ports中可以看到管脚分配情况。根据FPGA芯片的原理图将复位信号、时钟信号和LED分配管脚和电平标准,完成后点击保存。

4、弹出保存界面,文件类型默认“XDC”,文件名填写“run_led”,点击“OK”。

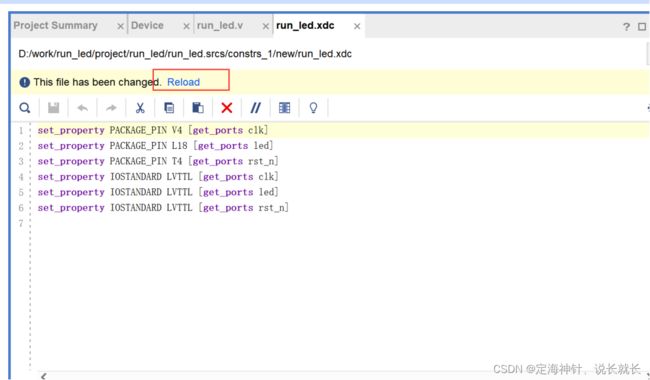

5、 打开刚才生成的“run_led.xdc”文件,是一个TCL脚本,如果我们了解语法,也可以自己编写xdc文件来约束管脚。

四、时序约束

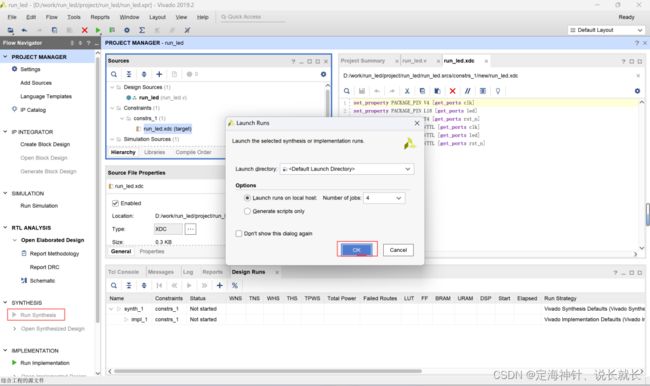

1、点击“Run Synthesis”开始综合,弹出窗口点击“OK”。

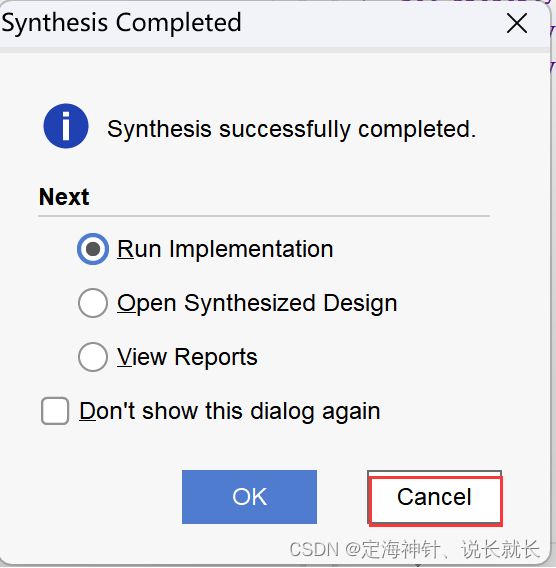

2、综合完成点击“Cancel”。

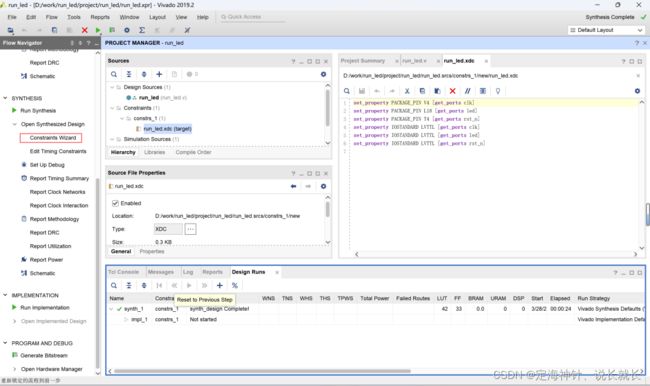

3、点击“Constraints Wizard”,在弹出的窗口点击“Next”。

4、 时序约束向导分析出设计中的时钟,这里把“clk”频率设置成20MHz,点击“Skip to Finish”,结束时序约束向导。

5、在弹出的窗口点击“OK”,点击“Finish”。Run_led.xdc文件已经更新,点击“Reload”重新加载文件,并保存文件。

五、生成BIT文件

编译的过程可以细分为综合、布局布线、生成bit文件等。

1、点击“Cenerate Bitsteam”,直接生成bit文件,在弹出的对话框可以选择任务数量,数量越大编译越快。

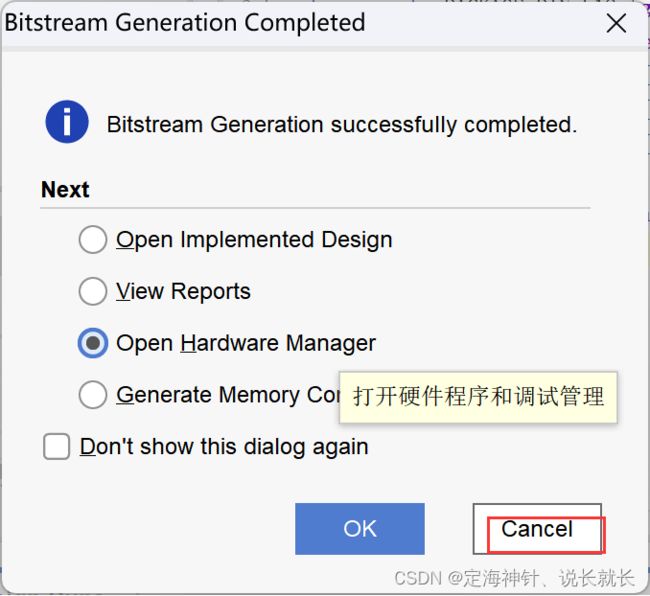

2、编译完成后,弹出对话框进行后续操作,可以选择“Open Hardware Manger”,也可以选择“Cancel”,先不下载。

六、Vivido仿真

利用Vivido自带的仿真工具来输出波形验证程序是否正确(在生成bit文件之前也可以仿真)。

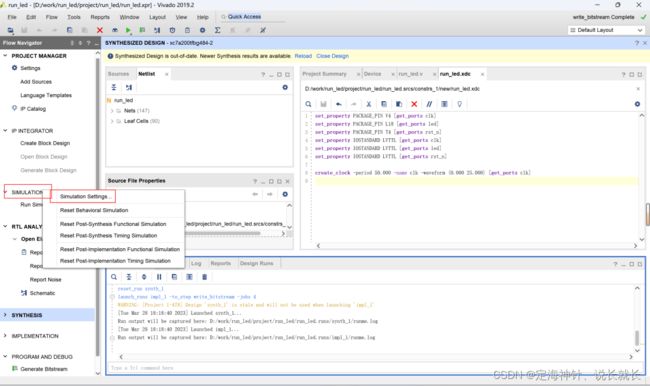

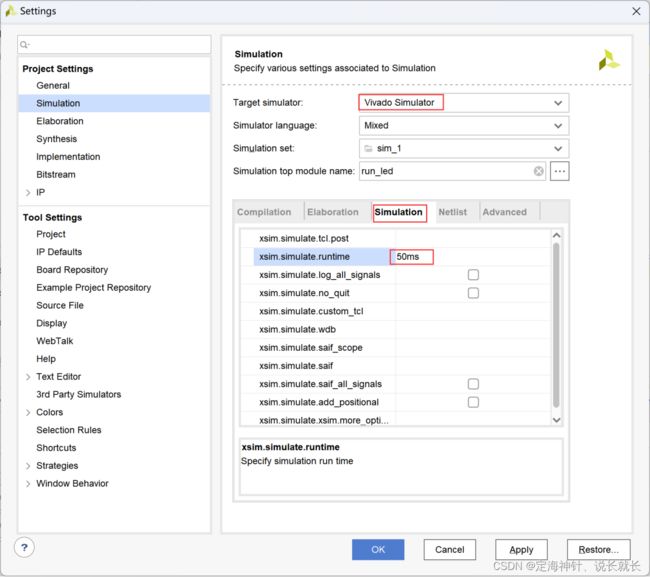

1、打开 SIMULATIONZ 中的 Simulation Settings,设置仿真配置。

2、在设置窗口进行配置,根据需要自行设置,我这里设置50ms。

3、添加激励测试文件,点击Project Manager下的Add Sources,选择仿真。

4、点击“Create File”生成仿真激励文件。

5、激励文件命名,我命名为“vtf_run_led_test”

6、 这里先不添加I/O Ports,点击OK.

7、在Simulation Sources中看到添加进的vtf_run_led_test文件。双击激励文件进行编写,编写后保存,vtf_run_led_teat.v自动成为仿真Hierarchy的顶层,文件下面是run_led.v。

仿真激励文件代码:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/03/28 18:28:36

// Design Name:

// Module Name: vtf_run_led_test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module vtf_run_led_test();

reg tb_clk ;

reg tb_rst_n;

wire tb_led;

parameter CYCLE=20;

//模块例化

run_led u_run_led(

.clk (tb_clk ),

.rst_n (tb_rst_n),

.led (tb_led )

);

//初始化

initial begin

tb_clk=1'b1;

tb_rst_n=1'b1;

#40;

tb_rst_n=1'b0;//复位

#40;

tb_rst_n=1'b1;

#(CYCLE*25*6);

$stop;

end

always #10 tb_clk=~tb_clk;

endmodule

8、点击Run Simulation ,在选择Run Behavioral Simulation。开始行为级仿真。

9、在弹出的仿真界面是仿真软件自动运行到仿真设置的50ms的波形。

10、可以点击Scope界面下的u_run_led,再右键选择Objects界面下的timer,在弹出的下拉菜单里选择Add to Wave Window。观测计数器的变化。

11、添加计数器cnt后,需要点击restart复位,再点击Run ALL。

12、就可以看到更新后的仿真图了。