FPGA时序约束

FPGA时序设计

- 概述

- 时序约束相关概念

-

-

- 发起沿和捕获沿

- 时序路径

- 常规时钟路径

- 数据到达时间

- 时钟到达时间

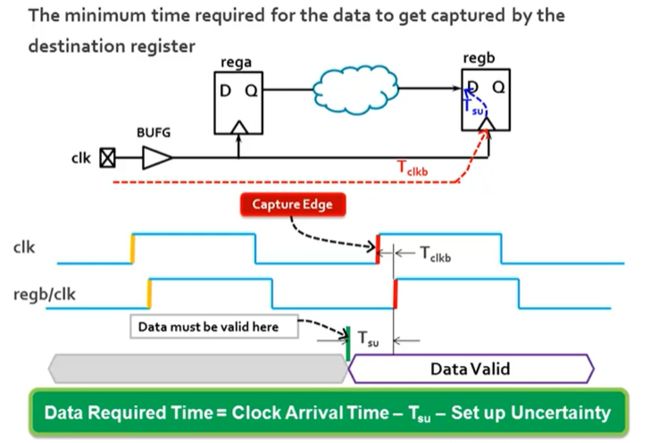

- 数据需求时间(建立情况下)

- 数据需求时间(保持情况下)

- 建立时间的裕量

- 保持时间的裕量

-

- 时序分类

- 时序约束语法

-

- 创建时钟周期约束

- 设置输入延时约束

- 设置输出延时约束

-

- FPGA内部组合逻辑从输入端口到输出端口

- 虚拟时钟

- 设置多周期约束

-

- 两倍时钟周期使能信号

- 相同的时钟周期,目的时钟正向偏移

- 相同的时钟周期,目的时钟负向偏移

- 发端慢速,收端快速

- 发端快速,收端慢速

- 设置伪路径约束

-

- 1. 组合逻辑中的伪路径

- 2. 时序路径中的伪路径

- 3. 跨时钟域中的伪路径

概述

要简单介绍为什么么进行时序约束,以及文章编写的思路

时序约束相关概念

-

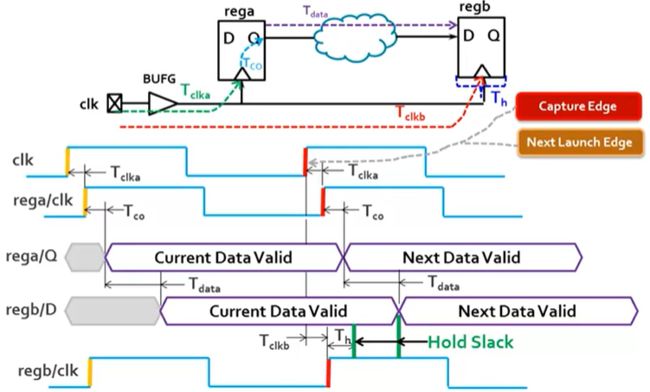

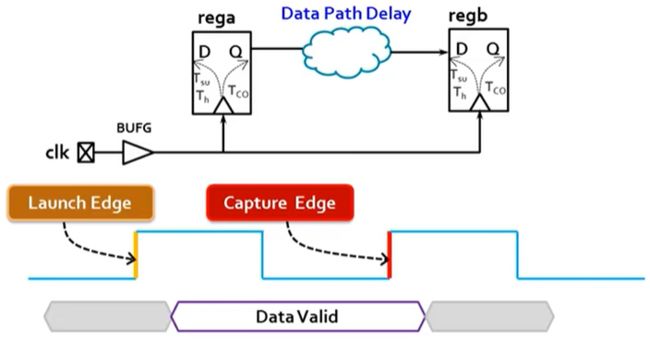

发起沿和捕获沿

-

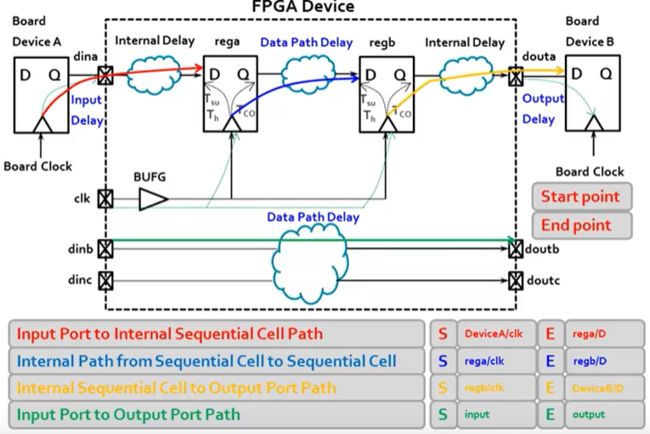

时序路径

-

常规时钟路径

-

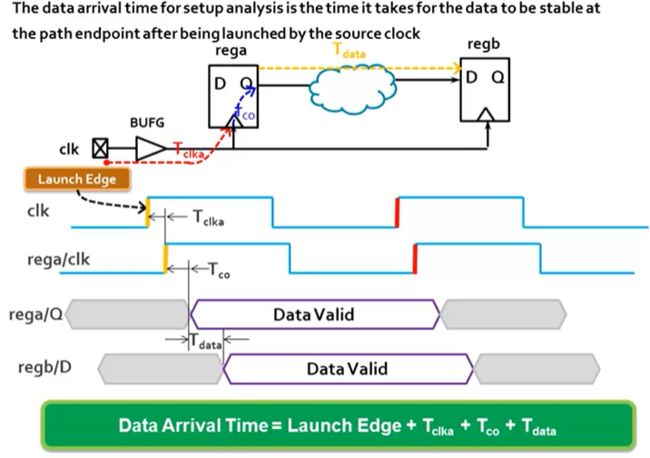

数据到达时间

-

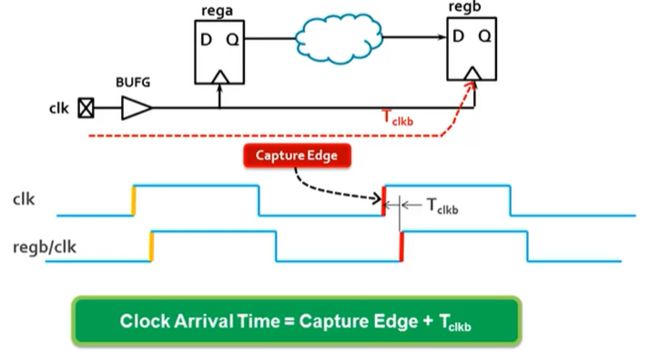

时钟到达时间

-

数据需求时间(建立情况下)

时序分类

- create_clock :FPGA内部的同步元件之间的路径

- set_input_delay : 外部器件末级触发器发送数据通过FPGA端口到达FPGA内部第一级接收的触发器的路径

- set_output_delay :FPGA的末级触发器通过端口到达下游芯片的路径

- set_max_delay :从输入端口到输出端口纯粹的组合逻辑

- clock group

- multicycle path

- false path

时序约束语法

创建时钟周期约束

- 时钟的定义

周期、占空比、相位

- primary clock

晶振提供的时钟、吉比特transceiver的输入引脚

create_clock -period 10 [get_ports sysclk]

- 生成时钟

MMCM、PLL、用户自己的分频逻辑,通过get_pins或get_ports来指定源时钟

create_generated_clock -name clkdiv2 -source [get_ports clkin] -divide_by 2 [get_pins REGA/Q]

create_generated_clock -name clkdiv2 -source [get_pins REGA/C] -divide_by 2 [get_pins REGA/Q]

create_generated_clock -name clkdiv2 -source [get_pins REGA/C] -edges {1 3 5} [get_pins REGA/Q]

-

report_clocks

-

时钟的分组的关系

同步时钟(synchronous clocks)

异步时钟(asynchronous clocks)

set_clock_groups -name xxx -asynchronous -group [get xxx] -group [get xxx]

set_clock_groups -name xxx -physically_exclusive -group [get xxx] -group [get xxx]

不可扩展时钟(unexpendable clocks)

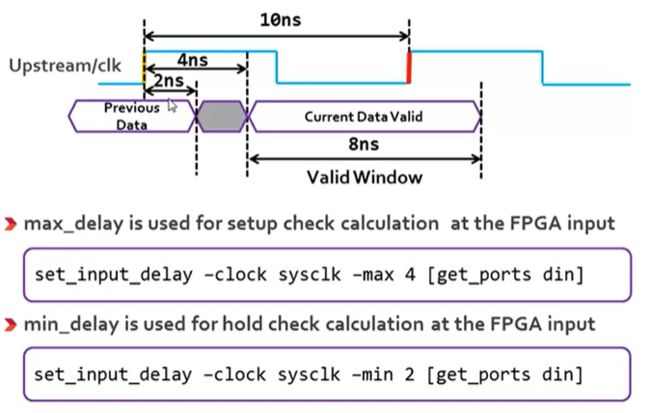

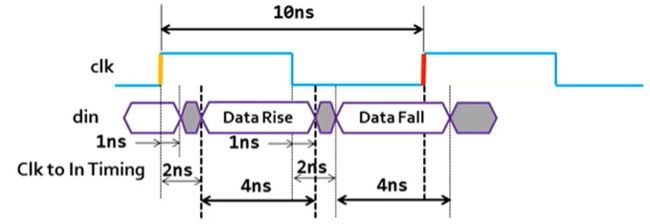

设置输入延时约束

set_input_delay 设置的延时表示数据到达时间相对于时钟的发起沿的延时。这个发起沿来自外部设备的时钟。数据到达时间是数据到达FPGA数据端口的时间。所以,这个约束就是告诉FPGA,外部设备的CLK与data之间的延迟关系。这样,FPGA就可以来调整内部时钟来适用它。

set_input_delay -clock sysclk -max 4 [get_ports clkin]

set_input_delay -clock sysclk -min 2 [get_ports clkin]

DDR input delay示例

set_input_delay 1 -min -clock clk [get_ports data_in]

set_input_delay 2 -max -clock clk [get_ports data_in]

set_input_delay 1 -min -clock clk [get_ports data_in] -clock_fall -add_delay

set_input_delay 2 -max -clock clk [get_ports data_in] -clock_fall -add_delay

clock_fall 告诉分析工具,当前时序分析使用下降沿作为发起沿。

add_delay告诉分析工具,当前语句和前面的语句同时有效,不要进行覆盖。

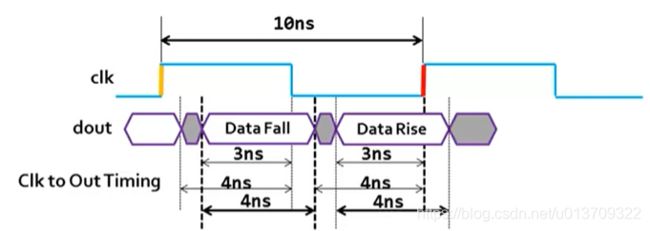

设置输出延时约束

set_output_delay设置延迟表示下游芯片接受的数据相对于捕获沿的时间间隔,延迟参数的大小等于数据到达的时间减去捕获沿时间。和input delay一样,它们都是以外部芯片的时钟作为参考时钟的。区别是,input delay选择的是发起沿,所以数据转换的时间在发起沿后面;output选择的是捕获沿,数据转变在前面。所以,总结来说,无论输入还是输出,delay的时间就是数据转变的时刻和参考时刻之间的时间间隔。对于输入约束,参考时刻是发起沿;对于输出约束,参考时刻是捕获沿。

set_output_delay -min -1 -clock clk [get_ports data_out]

set_output_delay -max 3 -clock clk [get_ports data_out]

set_output_delay -min -1 -clock clk [get_ports data_out] -clock_fall -add_delay

set_output_delay -max 3 -clock clk [get_ports data_out] -clock_fall -add_delay

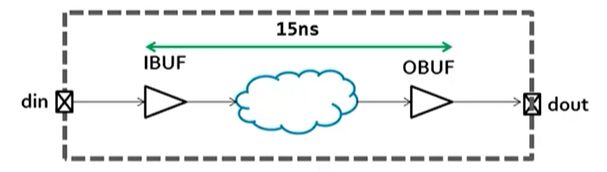

FPGA内部组合逻辑从输入端口到输出端口

set_max_delay 15 -from [get_ports din] to [get_ports dout]

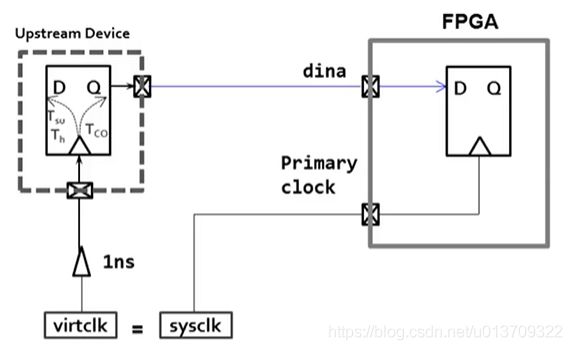

虚拟时钟

外部设备到FPGA只有数据端口,没有时钟端口,需要创建虚拟时钟。这种情况下,一般来说,外部设备和FPGA使用相同的时钟源。下面的例子就是外部设备和FPGA使用同一个时钟源,外部设备在时钟的输入处添加了1ns的延迟的时钟buffer。

create_clock -name sysclk -period 10 [get_ports clkin]

create_clock -name virclk -period 10

set_clock_latency -source 1 [get_clocks virclk]

set_input_delay -clock vitclk -max 4 [get_ports ain]

set_input_delay -clock vitclk -min 2 [get_ports ain]

对于 input delay,它的参考时钟可能是primary clock,也可能是使虚拟时钟。使用primary clock的情况下,外部器件和FPGA使用同一个时钟,那么,这个时钟一般就是外部设备的data端口所使用的clock。所以,这时的外部设备和FPGA同时连接data和clock。虚拟时钟的 clock对于FPGA和外部设备来说有一定的差异,比如上面的相位偏移。简而言之,primary clock和虚拟时钟的区别就是是不是同一个时钟,是同一个时钟就用primary clock,不是同一个时钟就用虚拟时钟。虚拟时钟源时钟和目的时钟之间的关系是固定的,不然无法分析。

设置多周期约束

start 和 end 用于选择参考时钟,start 表示参考时钟是源时钟,end 表示参考时钟是目的时钟。

当选择 -end 时,表示参考时钟选择目的时钟。

| 源时钟(-start),发送沿移动 | 目的时钟(-end),捕获沿移动 | |

|---|---|---|

| 建立 | <----(向后) | —>(向前)(默认) |

| 保持 | —>(向前)(默认) | <—(向后) |

-setup:表示该多周期路径所需要的时钟周期的个数

-hold:表示相对于缺省捕获沿,实际捕获沿应回调的时钟周期的个数

-end:表示参考时钟为捕获端所用时钟,对于-setup,缺省为-end

-start:表示参考时钟为发送端所用的时钟,对于-hold,缺省为-start

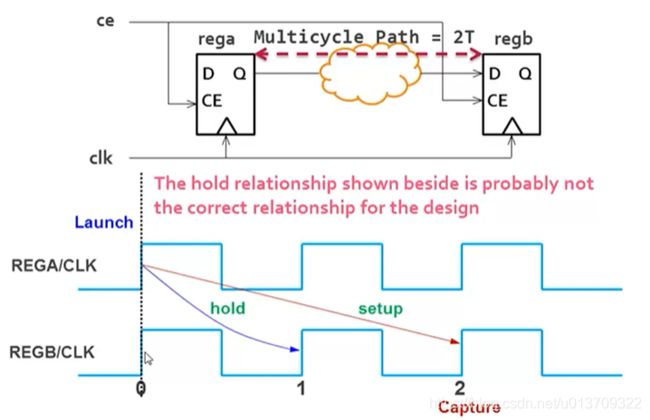

两倍时钟周期使能信号

set_multicycle_path -from [get_cells rega] -to [get_cells rega] -setup -end 2

set_multicycle_path -from [get_cells regb] -to [get_cells regb] -hold -end 1

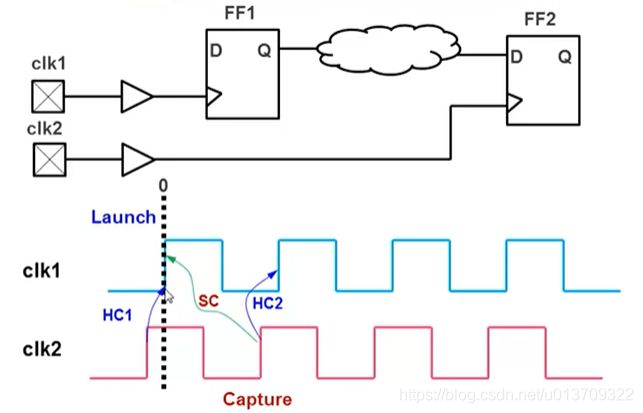

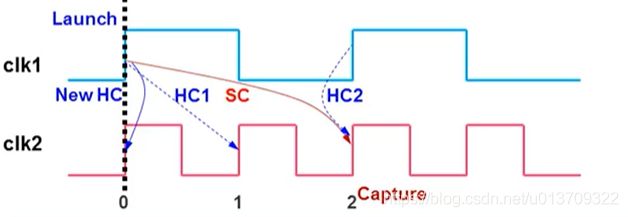

相同的时钟周期,目的时钟正向偏移

set_multicycle_path -from [get_clocks clk1] -to [get_clocks clk2] -setup -end 2

相同的时钟周期,目的时钟负向偏移

发端慢速,收端快速

set_multicycle_path -from [get_clocks clk1] -to [get_clocks clk2] -setup -end 2

set_multicycle_path -from [get_clocks clk1] -to [get_clocks clk2] -hold -end 1

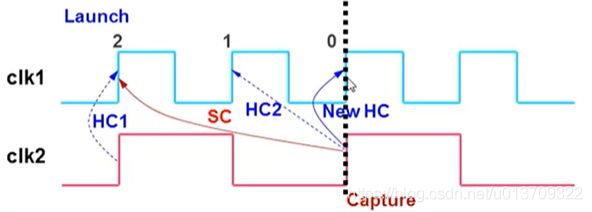

发端快速,收端慢速

set_multicycle_path -from [get_clocks clk1] -to [get_clocks clk2] -setup -start 2

set_multicycle_path -from [get_clocks clk1] -to [get_clocks clk2] -hold -start 1

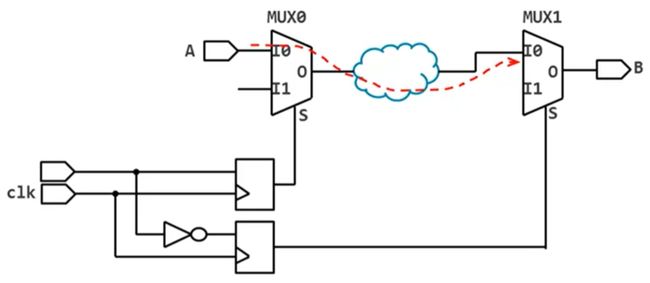

设置伪路径约束

伪路径是指在设计存在的路径,但是并不存在作用.在综合的时候不起作用,在实现的时候起作用。

设置伪路径可以去除无效的伪路径,可以节约编译的时间。

伪路径设置的命令 : set_false_path

set_false_path [from args] [to args] [through args]

例子

set_false_path -from S1 -through {x1, x2}

这个例子表示来自S1的路径,它们通过x1或者x2。{}中表示的是或的关系。

1. 组合逻辑中的伪路径

set_false_path -through [get_pins MUX0/I0] -through [get_pins MUX1/I1]

2. 时序路径中的伪路径

set_false_path -through [get_pins MUX0/I0] -through [get_pins MUX1/I0]

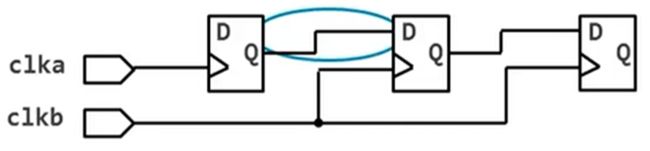

3. 跨时钟域中的伪路径

set_false_path -from [get_clocks clka] -to [get_clocks clkb]

set_false_path -from [get_clocks clkb] -to [get_clocks clka]

等价于

set_clock_groups -asynchronous -group [get_clocks clka] -groups [get_clocks clkb]

false path timing report

set_flase_path -from [get_ports rst_pin]

report timing -from [get_ports rst_pin]