SPI 及 NOR Flash 介绍

一、SPI

1.SPI的含义

SPI:串行外设设备接口(Serial Peripheral Interface),是一种高速的,全双工,同步的通信总线。SPI接口主要应用在存储芯片、AD转换器以及LCD中。SPI接口主要应用在存储芯片、AD转换器以及LCD中。

SPI 的引脚信息:

MISO(Master In / Slave Out)主设备数据输入,从设备数据输出。

MOSI(Master Out / Slave In)主设备数据输出,从设备数据输入。

SCLK(Serial Clock)时钟信号,由主设备产生。

CS(Chip Select)从设备片选信号,由主设备产生。

SPI 的工作原理

在主机和从机都有一个串行移位寄存器,主机通过向它的 SPI 串行寄存器写入一个字节来发起一次传输。串行移位寄存器通过 MOSI 信号线将字节传送给从机,从机也将自己的串行移位寄存器中的内容通过 MISO 信号线返回给主机。这样,两个移位寄存器中的内容就被交换。外设的写操作和读操作是同步完成的。如果只是进行写操作,主机只需忽略接收到的字节。反之,若主机要读取从机的一个字节,就必须发送一个空字节引发从机传输。

SPI 的传输方式

SPI 总线具有三种传输方式:全双工、单工以及半双工传输方式。

全双工通信:在任何时刻,主机与从机之间都可以同时进行数据的发送和接收。单工通信:在同一时刻,只有一个传输的方向,发送或者是接收。半双工通信:在同一时刻,只能为一个方向传输数据。

① SPI相关引脚

MISO(输入数据线)、MOSI(输出数据线)、SCK(时钟)、NSS(片选)

② 数据发送和接收

与缓冲区、移位寄存器以及引脚相关

③ 时钟信号

SPI时钟信号是通过SPI_CR1寄存器配置

④ 主控制逻辑

涉及两个控制寄存器SPI_CR1/2用于配置SPI工作,SPI_SR用于查看工作状态

2.SPI 工作模式

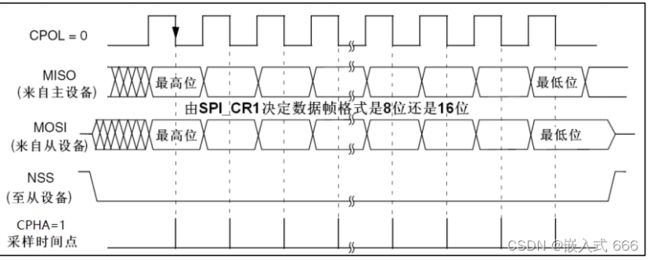

CPOL,详称 Clock Polarity,就是时钟极性,当主从机没有数据传输的时候 SCL 线的电平

状态(即空闲状态)。假如空闲状态是高电平,CPOL= 1;若空闲状态时低电平,那么 CPOL = 0。

CPHA,详称 Clock Phase,就是时钟相位。CPHA= 0 的情况就表示数据的采样是从第 1 个边沿信号上即奇数边沿,具体是上升沿还是下降沿的问题,是由 CPOL 决定的。CPHA = 1 的情况就是表示数据采样是从第 2 个边沿即偶数边沿,它的边沿极性要注意一点,不是和上面 CPHA = 0 一样的边沿情况。

由于 CPOL 和 CPHA 都有两种不同状态,所以 SPI 分成了 4 种模式。

4种工作模式时序图

1.串行时钟的奇数边沿上升沿采样时序图

首先由于配置了 CPOL= 0,可以看到当数据未发送或者发送完毕,SCL 的状态

是低电平,再者 CPHA = 0 即是奇数边沿采集。所以传输的数据会在奇数边沿上升沿被采集,

MOSI 和 MISO 数据的有效信号需要在 SCK 奇数边沿保持稳定且被采样,在非采样时刻,MOSI

和 MISO 的有效信号才发生变化。

2.串行时钟的偶数边沿下降沿采样图

由于 CPOL = 0,所以 SCL 的空闲状态依然是低电平,CPHA = 1 数据就从偶数边沿

采样,至于是上升沿还是下降沿,从上图就可以知道,是下降沿。这里有一个误区,空闲状态

是低电平的情况下,不是应该上升沿吗,为什么这里是下降沿?首先我们先明确这里是偶数边

沿采样,那么看图就很清晰,SCL 低电平空闲状态下,上升沿是在奇数边沿上,下降沿是在偶

数边沿上。

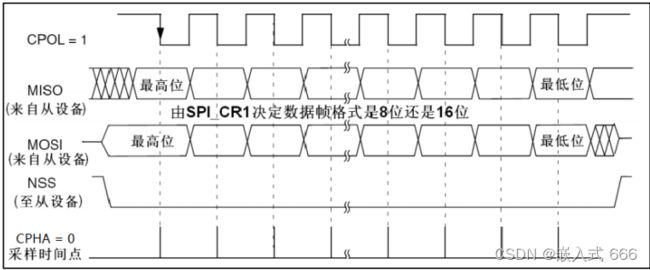

3.串行时钟的奇数边沿下降沿采样图

CPOL= 1,即 SCL 空闲状态为高电平,在 CPHA = 0,奇数边沿采样的情况下,数据在奇数边沿下降沿要保持稳定并等待采样。

4.串行时钟的偶数边沿上升沿采样图

图中是 CPOL= 1&&CPHA= 1 的情形,可以看到未发送数据和发送数据完毕,SCL

的状态是高电平,奇数边沿的边沿极性是上升沿,偶数边沿的边沿极性是下降沿。因为 CPHA

= 1,所以数据在偶数边沿上升沿被采样。在奇数边沿的时候 MOSI 和 MISO 会发生变化,在偶

数边沿时候是稳定的。

3. SPI 寄存器

1.SPI 控制寄存器 1(SPI_CR1)

该寄存器控制着 SPI 很多相关信息,包括主设备模式选择,传输方向,数据格式,时钟极性、时钟相位和使能等。在位 CPHA 置 1,数据采样从第二个时钟边沿开始;在位 CPOL 置 0,在空闲状态时,SCK 保持低电平;在位 MSTR 置 1,配置为主设备;在位 BR[2:0]置 7,使用 256 分频,速度最低;在位 SPE 置 1,开启 SPI 设备;在位 LSBFIRST 置0,MSB 先传输;在位 SSI 置 1,禁止软件从设备,即做主机;在位 SSM 置 1,软件片选 NSS 控制;在位 RXONLY 置 0,传输方式采用的是全双工模式;在位 DFF 置 0,使用 8 位数据帧格式。

2.SPI 状态寄存器(SPI_SR)

该寄存器是查询当前 SPI 的状态的,我们在实验中用到的是 TXE 位和 RXNE 位,即发送完成和接收完成是否的标记。

3.SPI 数据寄存器(SPI_DR)

该寄存器是 SPI 数据寄存器,是一个双寄存器,包括了发送缓存和接收缓存。当向该寄存

器写数据的时候,SPI 就会自动发送,当收到数据的时候,也是存在该寄存器内。

二、 NOR Flash 简介

.1.Flash 简介

Flash 是常见的用于存储数据的半导体器件,它具有容量大、可重复擦写、按“扇区/块”擦除、掉电后数据可继续保存的特性。常见的 Flash 主要有 NOR Flash 和 Nand Flash 两种类型NOR 和 NAND 是两种数字门电路,可以简单地认为 Flash 内部存储单元使用哪种门作存储单元就是哪类型的 Flash。U 盘,SSD,eMMC 等为 NAND 型,而 NOR Flash 则根据设计需要灵活应用于各类 PCB 上,如 BIOS,手机等。

NOR 与 NAND 在数据写入前都需要有擦除操作,但实际上 NOR Flash 的一个 bit 可以从 1变成 0,而要从 0 变 1 就要擦除后再写入,NAND Flash 这两种情况都需要擦除。擦除操作的最小单位为“扇区/块”,这意味着有时候即使只写一字节的数据,则这个“扇区/块”上之前的数据都可能会被擦除。

NOR 的地址线和数据线分开,它可以按“字节”读写数据,符合 CPU 的指令译码执行要求,所以假如 NOR 上存储了代码指令,CPU 给 NOR 一个地址,NOR 就能向 CPU 返回一个数据让 CPU 执行,中间不需要额外的处理操作,因此可以用 NOR Flash 直接作为嵌入式 MCU 的程序存储空间。

NAND 的数据和地址线共用,只能按“块”来读写数据,假如 NAND 上存储了代码指令,CPU 给 NAND 地址后,它无法直接返回该地址的数据,所以不符合指令译码要求。若代码存储在 NAND 上,可以把它先加载到 RAM 存储器上,再由 CPU 执行。所以在功能上可以认为 NOR 是一种断电后数据不丢失的 RAM,但它的擦除单位与 RAM 有区别,且读写速度比 RAM 要慢得多。

Flash 也有对应的缺点:一是 Flash 的使用寿命,另一个是可能的位反转。

使用寿命体现在:读写上是 FLASH 的擦除次数都是有限的(NOR Flash 普遍是 10 万次左右),当它的使用接近寿命的时候,可能会出现写操作失败。由于 NAND 通常是整块擦写,块内有一位失效整个块就会失效,这被称为坏块。使用 NAND Flash 最好通过算法扫描介质找出坏块并标记为不可用,因为坏块上的数据是不准确的。

位反转是数据位写入时为 1,但经过一定时间的环境变化后可能实际变为 0 的情况,反之亦然。位反转的原因很多,可能是器件特性也可能与环境、干扰有关,由于位反转的问题可能存在,所以 FLASH 存储器需要“探测/错误更正(EDC/ECC)”算法来确保数据的正确性。

2.NOR FLASH 工作时序

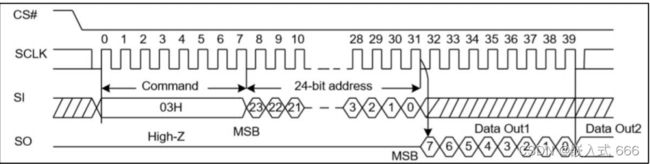

- NM25Q128 读操作时序图

可知读数据指令是 03H,可以读出一个字节或者多个字节。发起读操作时,先把 CS片选管脚拉低,然后通过 MOSI 引脚把 03H 发送芯片,之后再发送要读取的 24 位地址,这些数据在 CLK 上升沿时采样。芯片接收完 24 位地址之后,就会把相对应地址的数据在 CLK 引脚下降沿从 MISO 引脚发送出去。从图中可以看出只要 CLK 一直在工作,那么通过一条读指令就可以把整个芯片存储区的数据读出来。当主机把 CS 引脚拉高,数据传输停止。

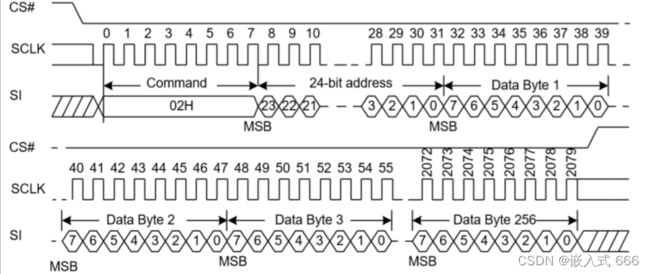

2.NM25Q128 页写时序

在发送页写指令之前,需要先发送“写使能”指令。然后主机拉低 CS 引脚,然后通过 MOSI引脚把 02H 发送到芯片,接着发送 24 位地址,最后你就可以发送你需要写的字节数据到芯片。完成数据写入之后,需要拉高 CS 引脚,停止数据传输。

- 扇区擦除时序图

扇区擦除指的是将一个扇区擦除。擦除扇区后,扇区的位全置 1,即扇区字节为 FFh。同样的,在执行扇区擦除之前,需要先执行写使能指令。这里需要注意的是当前 SPI 总线的状态,假如总线状态是 BUSY,那么这个扇区擦除是无效的,所以在拉低 CS 引脚准备发送数据前,需要先要确定 SPI 总线的状态,这就需要执行读状态寄存器指令,读取状态寄存器的 BUSY 位,需要等待 BUSY 位为 0,才可以执行擦除工作。接着按时序图分析,主机先拉低 CS 引脚,然后通过 MOSI 引脚发送指令代码 20h 到芯片,然后接着把 24 位扇区地址发送到芯片,然后需要拉高 CS 引脚,通过读取寄存器状态等待扇区擦除操作完成。

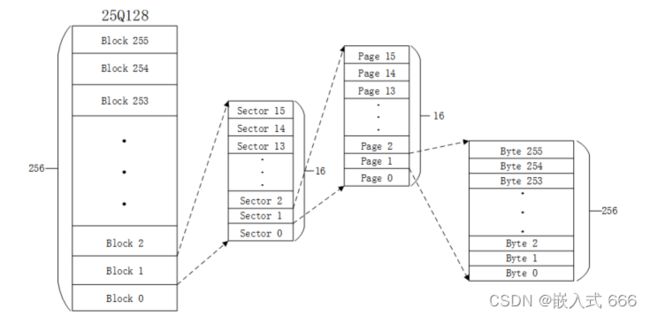

3.块、扇区、页和字节的关系