所谓的AI芯片到底指什么?

进入公司AI产业快有3个年头,AI芯片和传统芯片,甚至AI芯片和GPU,还有AI芯片的发展历史,面向未来场景的挑战都有很多话题,下面我们一起来聊聊AI芯片和传统芯片的区别哈。

芯片是半导体元件产品的统称,而集成电路,缩写是IC,就是将电路小型化,通过电子学和光学,将电路制造在半导体晶圆上面。

我们会分为4个小点进行介绍AI芯片前言解读。首先是AI芯片从CPU、GPU、到XPU的发展情况总体介绍,接着是AI芯片都有哪些系统架构,基于不同的系统架构,又引申出不同的AI芯片。第三部分来整体看看,AI芯片的产业链情况,了解AI芯片从设计到应用的一个分部。最后自然是了解AI芯片未来的发展趋势,展望未来。

AI芯片发展概述

首先我们说下到底什么是AI芯片,广义上讲,只要能够运行人工智能算法的芯片都叫作AI芯片。但是通常意义上的AI芯片,指的是针对AI算法做了特殊加速设计的芯片,当前阶段的AI算法一般以深度学习算法为主,也可以包括其它机器学习算法。

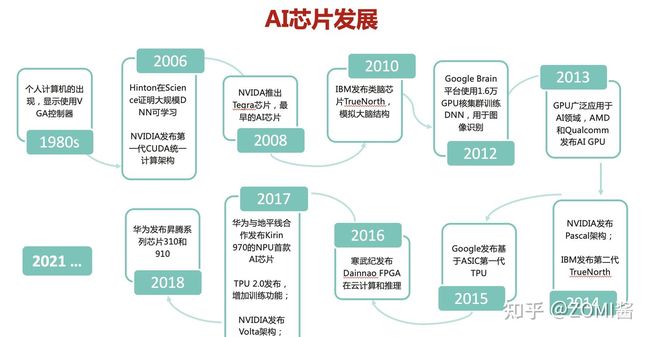

下面我们主要回顾下近20年以来AI芯片发展。在90年代和20世纪初,受制于算法、数据量等因素制约,这个阶段AI芯片并没有太多市场需求,通用CPU即可满足AI算法和应用的需要。

从2006年开始,Hinton在Science杂志上发表了使用神经网络降低数据维度的文章,为深度学习在大规模数据中可学习带来研究理论基础。同年,英伟达推出了CUDA,使开发者可以在GPU上面方便地进行编程。

在这之后的5年,人们发现GPU并行计算能力,恰好适应AI算法和数据并行计算的需求,开始逐渐地尝试使用GPU来运行AI算法和进行验证。

进入2012年后,云计算和移动设备广泛地发展起来,大量图像数据和用户数据积累,同年Google使用1.6万个GPU核组成的并行计算平台Google Brain训练AI模型,在语音和图像识别等领域获得了巨大成功。同年Alex利用2块GPU的并行能力,实现的AlexNet,将图像分类错误率从26%降低到15%,碾压第二名的分类性能,一举夺得ImageNet比赛冠军。

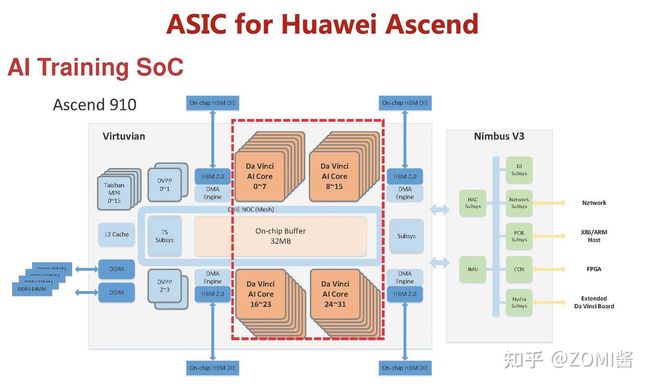

产业和学术对算力的需求是永无止尽的,随着AI对计算的需求不断增长和AI产业的爆发,2014年英伟达发布了首个为深度学习设计的GPU架构Pascal开始。到了2016年,Google公布了第一代ASIC芯片TPU,到2021年发展到了第四代。2017年,华为第一个将NPU集成到手机上,使用AI算法增强手机拍照能力。在2018年,华为昇腾910芯片ASIC架构细节公布,实现了7nm EUV工艺、32核达芬奇架构,FP16算力达到256 Tera-FLOPS。

AI芯片系统架构

下面是这个问题的回答核心啦。

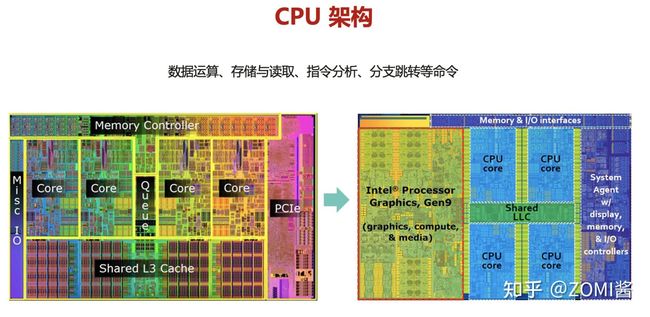

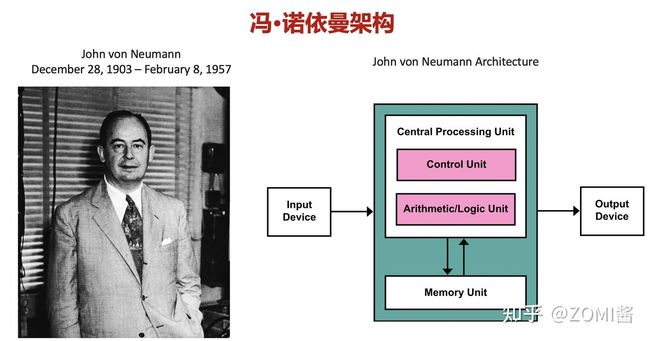

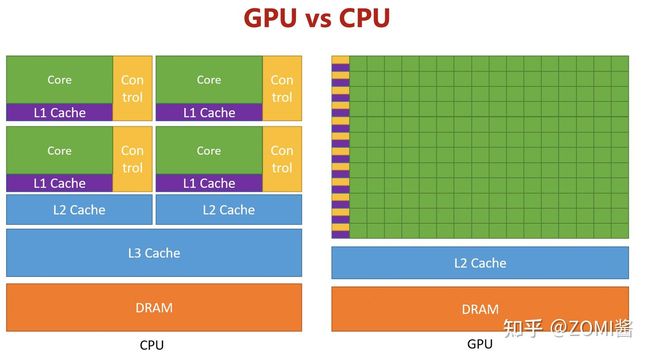

传统CPU结构中,除了数据运算,还需要执行数据的存储与读取、指令分析、分支跳转等命令。AI算法通常需要对海量数据进行处理,使用CPU执行算法,将会花费大量的时间,在数据指令的读取分析上,因此计算效率非常低。

随着AI产业的发展,业界出现了4种AI芯片架构。以冯·诺依曼传统计算架构为基础,用于加速硬件计算能力为主,有GPU、FPGA、ASIC 3种类型为代表,另外是颠覆冯·诺依曼架构,采用类脑神经结构独立设计,来提升计算能力。下面我们详细展开4种不同类型的架构。

第一种是GPU,通用的图像处理单元。GPU采用SIMD单指令多数据流的方式,也就是一条指令操作多个数据,拥有数量众多的计算单元和超长的图形图像处理流水线,刚发明的时候主要处理图像领域的并行加速运算,由于GPU内部,大部分的晶体管可以组成各类专用电路、多条流水线,使得GPU的计算速度远高于CPU,并拥有了更加强大的浮点运算能力,从而可以缓解深度学习算法的训练难题,释放AI潜能,因此广泛使用在深度学习算法领域。值得注意的一点是,GPU缺乏复杂的运算逻辑单元,必须由CPU进行调度。

英伟达作为GPU巨头,占据了七成的GPU和AI市场份额。在近几年的GTC大会上,CEO黄仁勋满嘴都是AI,可见AI对GPU发展的重要性不言而喻。

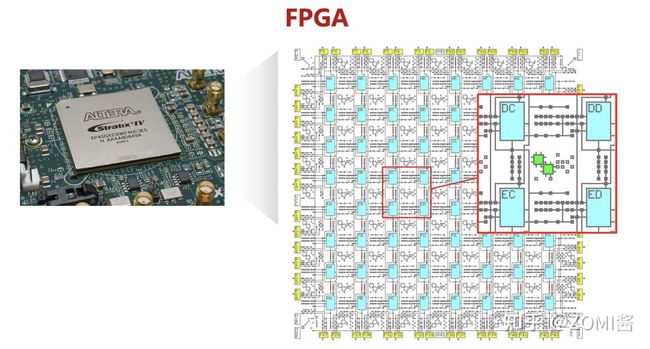

第二种是FPGA,通俗地理解就是,可以把硬件设计重复烧写在它的可编程存储器里面,使FPGA芯片可以执行不同的硬件设计和功能,所以被叫做「现场可编程逻辑阵列」。FPGA将指令锁定在硬件架构上,然后使用硬件指令流运行数据,简单理解就是将AI的计算架构用硬件电路实现出来,然后持续的将数据流输入系统,并完成计算。与GPU不同的是,FPGA可以同时拥有硬件流水线并行和数据并行处理能力,适用于以硬件流水线方式处理数据流,因此非常适用于AI推理阶段,相对于CPU与GPU有明显的性能或者能耗优势。

目前使用FPGA用于设计AI芯片国内有深鉴科技、微软Catapult项目。其中深鉴科技在2018年,以3亿美元的价格卖给FPGA巨头赛灵思。

由于FPGA编程难度大,对开发者要求高,于是出现了ASIC,专用集成电路,主要是实现AI特定算法,要求定制的芯片。所谓定制,那就是专门为AI算法,设计出来的架构,可以有助于提高芯片性能和功耗比,缺点是电路设计定制,导致相对开发周期长,不能扩展以外,好处就是在功耗、可靠性、芯片体积、性能等方面都有巨大的优势。

自从2016年Google发布基于ASIC架构的第一代TPU后,华为的昇腾系列芯片、寒武纪、比特大陆、地平线等厂商纷纷入局,即使AI算法发展迅猛,但是基于ASIC的AI芯片仍然是今天的主流。

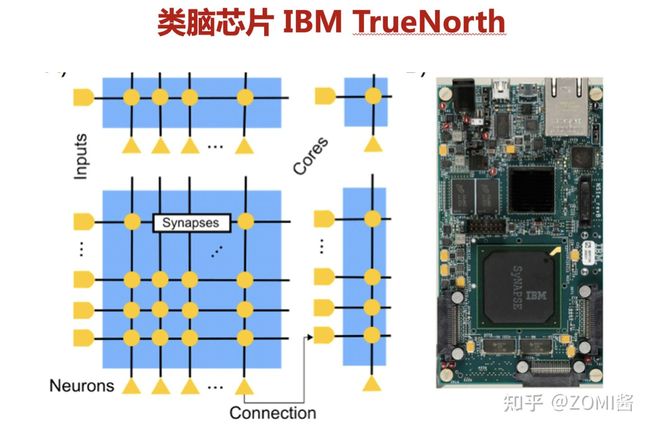

有人说,真正的人工智能芯片,未来发展的方向,会不会是类脑芯片呢?最后来谈一下,类脑芯片展,类脑芯片直接基于神经形态架构设计,用于模拟人脑功能进行感知方式、行为方式和思维方式的计算。但是研发难度巨大。

2014年,IBM推出第二代TrueNorth芯片,采用28nm工艺技术,里面包括了54亿个晶体管和 4096个处理核,相当于100万个可编程神经元,以及2.56亿个可编程突触,芯片的工作方式类似于人脑的神经元和突触之间的协同。

AI芯片的产业链

现在聊到AI芯片,肯定离不开AI芯片在产业链中的位置。那从芯片的整体产业环节来看,最上游的是芯片设计,中游是制造和封测,最后是下游的系统集成及应用。但是具体是怎么分工的吗?(聪)

感谢聪聪,我们来看一下这个图,AI芯片产业链环节中,我们这里以华为昇腾AI产业为例。首先是上游,昇腾910芯片采用的是ASIC专用集成电路,基于达芬奇架构来实现的,而达芬奇架构这款IP呢,则是通过华为海思设计的,所以海思是达芬奇这款IP的设计商。

设计完之后,就到中游,分别是AI芯片的晶圆制造和封装测试,但晶圆不仅是在封装时测试,制造后会有一次测试,封装后再进行一次。而现在大部分芯片的制造都依赖于台湾的TSMC,就是大名鼎鼎的台积电,还有中芯国际SIMC等芯片制造商。

最后是AI产业的下游,下游主要为系统集成及应用为主,华为昇腾AI产业作为AI系统集的主要集成商提供昇腾Atlas服务器,然后联合开发商,也就是俗称的ISV,来提供上层的AI解决方案。

AI芯片未来发展趋势

最后就是AI芯片的发展趋势啦,无论是华为昇腾产品的达芬奇架构、英伟达的Tensor Core、还是Google,深度学习需要海量数据进行计算,内存带宽的制约,已经成为整个系统的性能瓶颈。第二个就是海量内存和计算单元,访问频繁切换,导致整体功耗很难降下去。最后便是随着AI产业的快速变化,硬件如何适配算法是个难题。

我们不妨来预测一下AI芯片的4大发展趋势。

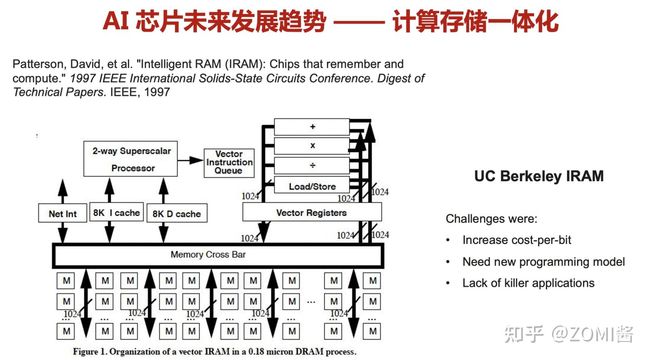

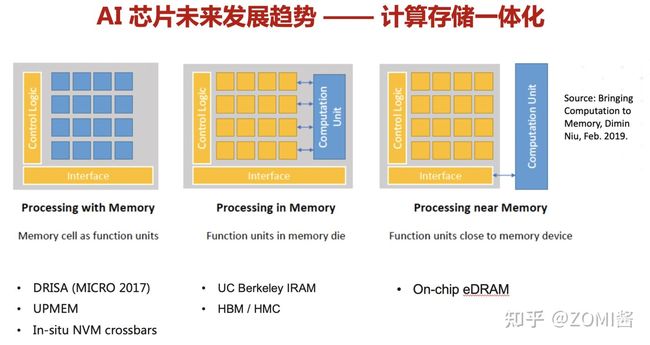

未来10年是加速计算架构变革的新十年。在计算存储一体化方面,也就是把计算单元和存储单元放在一起,使得AI系统的计算和数据吞吐量增大,还能显著地降低功耗。会不会出现一种新型非易失性存储器件,就是在存储阵列里面加上AI计算功能,从而节省数据搬移操作呢?现在硬件计算能力大于数据读取和访问性能,当计算单元不在是瓶颈,如何减少存储器的访问延时,将会成为下一个研究方向。

通常,离计算越近的存储器速度越快,每字节的成本也越高,同时容量也越受限,因此新型的存储结构也将应运而生。

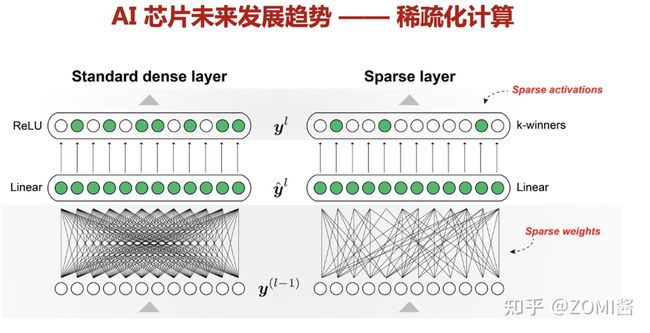

第二个趋势就是,稀疏化计算。随着千亿、到万亿网络模型提出,模型越来越大,但实际不是每个神经元,都能有效激活,这个时候稀疏计算,可以高效减少无用能效。特别是在推荐场景和图神经网络的应用,稀疏已经成为常态。

例如,哈佛大学就该问题提出了优化的五级流水线结构, 在最后一级输出了触发信号。在Activation层后对下一次计算的必要性进行预先判断,如果发现这是一个稀疏节点,则触发 SKIP信号,避免乘法运算的功耗,以达到减少无用功耗的目的。

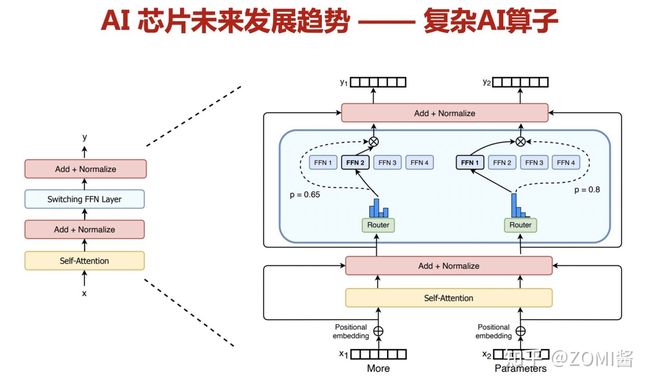

第三个趋势是支持更加复杂的AI算子。在标准的SIMD基础上,CNN的特殊结构复用,可以减少总线的数据通讯,Transformer结构对大数据在计算和存储之间切换,或者是在NLP和语音领域经常需要支持的动态shape,都需要合理地分解、映射这些不同复杂结构的算子,到有效的硬件上成为了一个值得研究的方向。

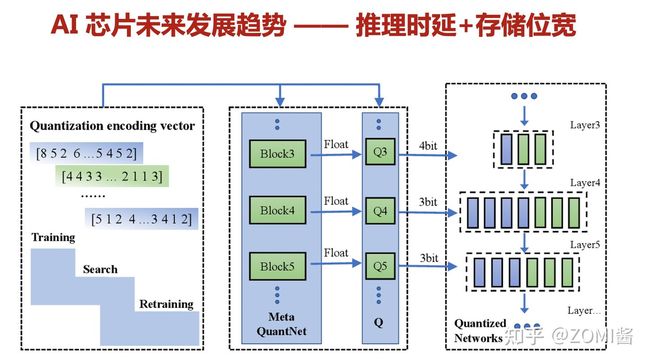

最后就是更快的推理时延和存储位宽。随着苹果、高通、华为都在手机芯片SoC上面推出AI推理硬件IP,近年来在手机SoC上,又引入可学习功能。未来如何在手机SoC上执行更快是业界很关注的一个点,包括经常看视频的抖音、bilibili,都需要对视频进行AI编解码,基于ISP进行AI影像处理。另外在理论计算领域,神经网络计算的位宽从32bit到16bit,出现了混合精度到目前8bit,甚至更低的比特数,都开始慢慢进入实践领域。

AI芯片,最后决定成败的因素会什么呢?我们应该选择,英伟达的GPU的硬件架构、华为达芬奇架构、Google TPU的脉动阵列架构呢?

总的来说,在ZOMI的观点来看,芯片架构的选择应该服务于整个芯片项目的成功,是很多因素博弈的结果。英伟达今天能在AI领域占据着头部市场,是归功于它的底层硬件架构,还是它完善的软硬件生态呢?这个问题呀,我觉得大家应该看得比我清楚。