从error 中学习

这学期有微机原理这门课,有学FPGA,开发环境用的是Xilinx ISE。它可以通过原理图、SM、HDL等方式输入。前两个星期稍微接触了一下,结合以前学51单片机的经历,然后google了一些资料代码什么的,初步实现了简单的按键控制灯的亮灭、流水灯功能,不过对verilog语法还不是很熟悉。

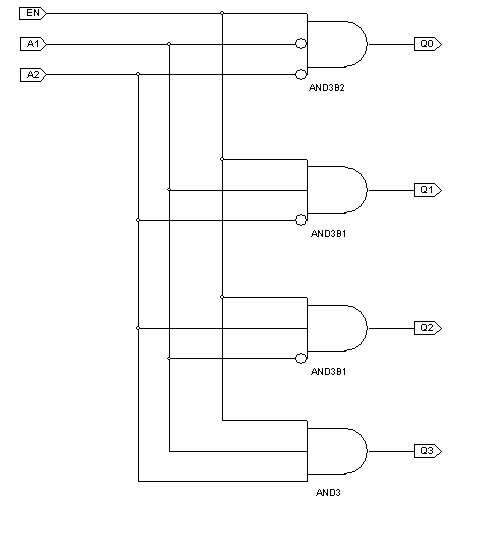

跑题了。今天想写这篇博文主要是为了记录和整理上课时遇到的一些问题。下午两节课,主要内容是熟悉ise的环境,然后根据指导书,用原理图输入的方法做一个译码器并仿真。

根据实验指导书,这部分内容第一步是要画出基本的门电路,然后用导线连接并添加输入输出,比较简单,和multisim差不多直接拖元件进去就好了,添加输入输出时偷了个懒,把A1、B1直接小写了。保存后点Check Schematic,没有error。

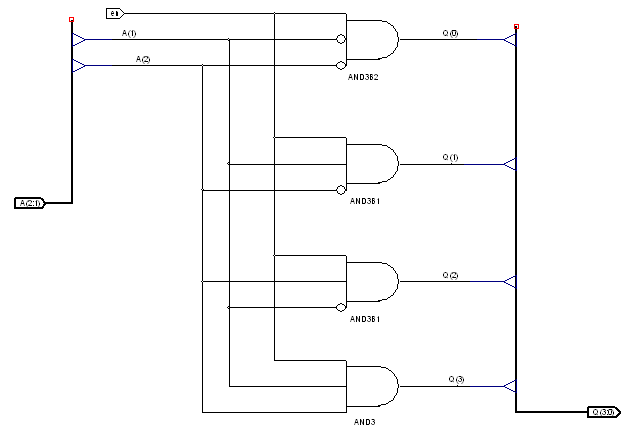

第二步是要把这个图复制到新建的source中,然后添加总线,设计成一个用总线表示输入、输出端口的2_4译码器的原理图。自己做了下,保存后点Check Schematic。结果跳出来一大堆error和warning。。。赶紧按照指导书重新做了一遍,结果还是一样:

ERROR:DesignEntry:239 - YMQ2.sch Incorrect bus tap at (896 704 992 704): destination branch 'a(1)' is not part of the source branch 'A(1:0)'.

ERROR:DesignEntry:215 - YMQ2.sch Net 'a(1)' is an illegal name, because there is no corresponding bit bus for this bit bus member.

当时就郁闷了,来来回回检查都不知道哪儿错了,google出来的全是一大堆英文,加上刚吃完午饭没休息就带着昏昏沉沉的大脑来了,根本看不了。。(虽然本来就不会看这一堆堆的全英文。。)最后当我再一次重连原理图并只把一个输入接上总线却还是报错后,我再一次问边上的同学帮忙,他早就做完这一步了,正在做仿真呢,而且之前问的时候他说估计是我哪里连线有问题。看了之后他也很奇怪,连线没问题,那到底问题出在什么地方呢。。再次检查各个部分的属性时他说会不会是那a、b出错了,换上大写的试试。

当时听到这我就顿悟了,怎么就没反应过来呢。。。之前我可是用过代码输入的呀。。。思路一下子就清晰了

如上图,在给总线端口命名的时候对话框中name 项输入的是A(1:0),输出总线是Q(3:0),这就相当于一个数组,之前写led灯的代码的时候都有

reg [24:0] count;//25位的寄存器类型的count计数变量

output [7:0] led;//8位的输出

看到这个冒号应该是很敏感的才对,至少看了error 中destination branch 'a(1)' is not part of the source branch 'A(1:0)'.也应该有所反应的,总线A(1:0)就像一个有2个元素的数组,里面应该是A(0),A(1),接出来a(0),a(1),前面的A就像数组名,名字都不一样怎么能被认出是里面的元素呢。。。

茅塞顿开的感觉。。

不用说,重命名以后error就没有了,不过上课时间也已所剩不多,仿真那部分自己课后做吧,兴奋,先把当时想到的这些记录下来,整理思考。

最后还有一点感想,这一切都是一开始偷懒没有每一步都按照指导书的说明而引起的,因为当时觉得这些变量或者名字怎么写没有太重要的区别,有时候偷懒能省下时间,但相反的情况也是很严重的,就像今天至少耗了一小时在这个问题上。。。但这也可以从另一个角度来看待,因为出现了error,暴露出了一些原来不知道的问题,解决了,就得到了新的收获和理解。看来以后想要收获多一些还得多偷偷懒啊o(∩_∩)o 或者至少先自己动手做一做,不能完全照抄指导书之类的,这样会隐藏很多潜在的问题。

还有一点,吃完饭得先休息一下,保持头脑的清醒非常非常重要,昏昏沉沉的大脑会让效率低得难以想象。

——从 error 中学习