ARM

title: arm

tags:

- ARM处理器

- 学习相关

categories:

- 课内

ARM课程相关笔记

等会贴一个文件代码,说实话这个csdn上的主题不是特别好康 ) (

第1章 嵌入式系统基础

1.1 嵌入式系统简介

定义:

理解:嵌入式系统核心就定制硬、软件。

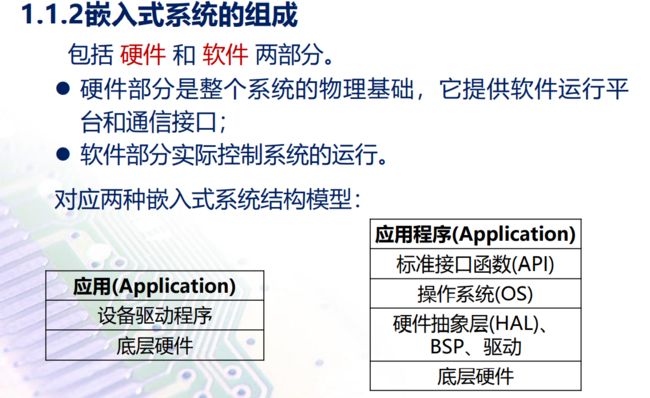

组成:

硬件

嵌入式系统的硬件包括:核心处理器、外围电路 和 外部设备三部分,如下图所示:

核心处理器

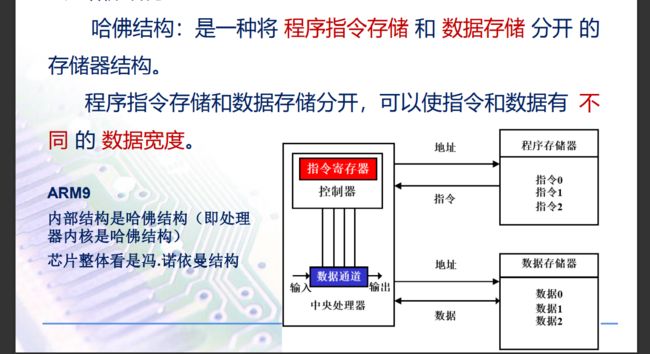

嵌入式微处理器可以采用 冯.诺依曼体系结构 和 哈佛体系结构;指令系统可以采用 精简指令集系统 和 复杂指令集 系统。

结构

指令集

软件

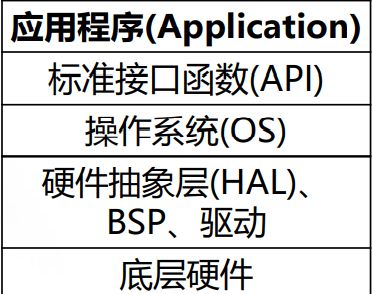

由嵌入式操作系统和嵌入式应用软件两大部分组成。

需要注意嵌入式系统和嵌入式操作系统是两个东西

有 的版本将应用程序接口 API 归属于 OS 层,就是按照 三层来 划分的。

特点

分类

1.2 嵌入式处理器

(1)嵌入式微处理器(MPU)

(2)嵌入式微控制器(MCU)

和嵌入式微处理器相比:微控制器的最大特点是单片化

(3)嵌入式DSP处理器 DSP 处理器是专门用于信号处理方面的处理器

(4)SOC片上系统 SOC最大特点是实现了软/硬件的无缝结合,直接在处理器芯片内部嵌入操作系统代码模块。

1.3 嵌入式系统开发环境

1.4 嵌入式操作系统

嵌入式操作系统可分为:实时操作系统 和 非实时操作系统。

按实时性的要求,可分为:

- 软实时系统

- 硬实时系统

按任务是否可被抢占,分为

- 可抢占型系统

- 不可抢占型系统

第2章 ARM处理器及系统结构

2.1 ARM 处理器简介

ARM(Advanced RISC Machines)有 3 种含义:

-

它是一个公司的名称;

-

是一类微处理器的通称;

-

还是一种技术的名称。

是专门从事基于 RISC 技术芯片开发的公司

优点

① 体积小、功耗低、低成本、高性能;

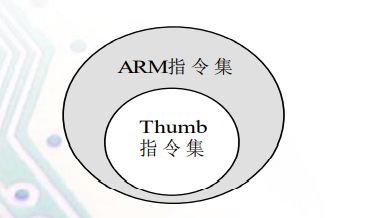

② 支持 Thumb(16位)/ARM(32位)双指令集,能 很好地兼容 8位/16位 器件;

③ 大量使用 寄存器,指令执行速度更快;

④ 大多数数据操作都在寄存器中完成;

⑤ 寻址方式灵活简单,执行效率高;

⑥ 指令长度固定

Thumb指令集: Thumb指令可以看做是ARM指令压缩形式的子集,是针对代码密度的问题而提出的,它具有16为的代码密度。

使得ARM可以处理16位指令,也能执行32位指令

代码密度

2.2 ARM 处理器系列

2.2.1 系列

一、ARMv4

二、ARMv4T

ARMv4T增加了16-bit Thumb 指令集

三、ARMv5TE

并在ARM指令集体系结构上扩展了增强的DSP 指令集:

四、ARMv5TEJ

增加了Jazelle扩展以支持Java 加速技术(处理器指令层对JAVA加速)。

五、ARMv6

SIMD扩展

Thumb-2和TrustZone 技术

六、ARMv7

ARMv7 定义了 3 种 不 同 的 处 理 器 配 置 ( processor profiles):

•Profile A是面向复杂、基于虚拟内存的OS和应用的

•Profile R是针对实时系统的

•Profile M是针对低成本应用的优化的微控制器

七、ARMv8

2011年11月,ARM公司发布了新一代处理器架构ARM V8,ARM的首个64位架构。

ARM处理器指令集的特点 ARM内核不是一个纯粹的RISC体系结构,ARM指令集 与纯粹的RISC的定义有以下几个不同。

① 一些特定指令的周期数可变,并不是每条ARM指令都是单周期的。

② 内嵌的桶形移位器产生了更为复杂的指令,扩展了指令的 功能,因此改善了内核的性能。

③ 支持16位的Thumb指令集,提高了代码密度。

④ 支持条件执行:每条指令都可以设置一个执行条件,只有 条件满足时才执行。

⑤ 增强指令:一些功能强大的数字信号处理指令被加入到 ARM指令集中

2.2.2 ARM体系结构的演变

-

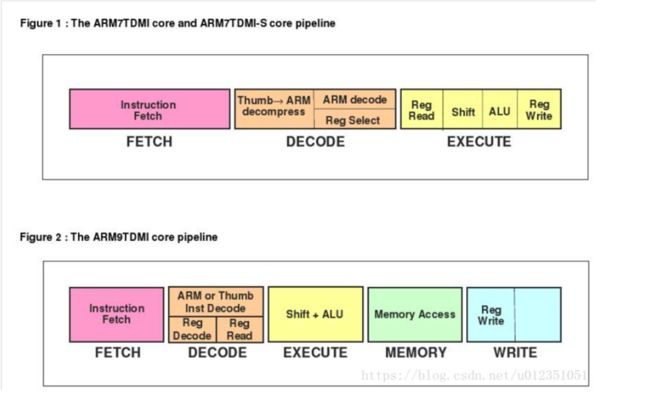

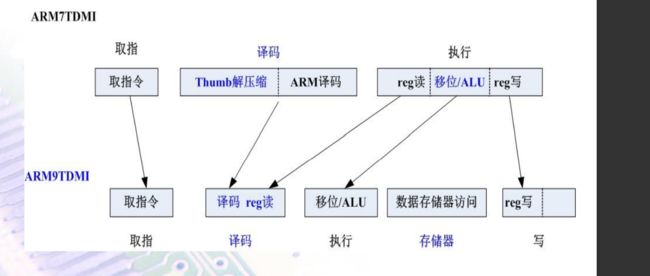

arm7 代码密度高并兼容16位的Thumb指令集;

-

arm9 采用 5级指令流水线。存储器系统根据 (改进型)哈弗体系结构(程序和数据空间独立的体系结构) 重新设计,区分了 数据总线 和 指令总线

我目前看到的资料ARM9的5条流水线是最多的,但是有说7条的,这个还有待考证

MPU支持实时操作系统;

- ARM9E 支持DSP指令集,适合于需要高速数字信号处理的场合;(有一张ppt说明了命名的规则)

- ARM10E 6条流水线

- ARM 11 内核有8级流水线

2.3 ARM9 处理器内核

2.3.1 ARM9系列MCU

一、ARM9TDMI

ARM9TDMI使用哈弗结构,通过cache可以同时读取指令和数据。

流水线从ARM7TDMI的 3级 增加到 5级。

二、ARM920T

三、ARM940T

2.3.2 流水线

…还是网上的图比较给力

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-BtlkNpCZ-1616828615683)(C:\Users\24482\AppData\Roaming\Typora\typora-user-images\image-20210323213217223.png)]

书上居然有…

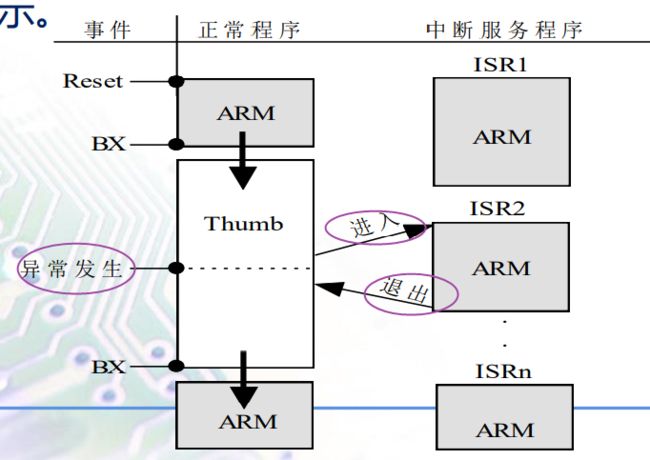

2.4 ARM 处理器工作状态 2种

2种工作状态

分别为ARM指令集和Thumb指令

其中ARM指令集 为32位(字)长度,具有最完整的功能;Thumb指令集为 16位(半字)长度,能实现ARM指令集的大部分功能

ARM指令集与Thumb指令集不能同时混合使用。

使用BX分支指令将ARM内核的操作 状态在ARM和Thumb之间进行切换

2.5 ARM 处理器运行模式 7种

(1)用户模式(USR): 正常程序执行模式,大部分任务执行在这种模式下。 用户模式是用户程序的工作模式。该没有权限去操作其它硬件资源,也不能切换到其它模式下。

(2)系统模式(SYS): 系统模式是特权模式,不受用户模式的限制。用户模式和系统模式共用一套寄存器,但比用户模式有更高的权限, 可以访问所有系统资源及进行模式切换。

(3)一般中断模式(IRQ): 一般中断模式也叫通用中断模式,用于处理一般的中断请求,通常在硬件产生中断信号之后自动进入该模式,该模式为特权模式,可以自由访问系统硬件资源。

(4)快速中断模式(FIQ): 快速中断模式是相对一般中断模式而言的,它是用来处理对时间要求比较紧急的中断请求,主要用于高速数据传输及通道处理中,其中断优先级相对普通中断更高。

(5)管理模式(Supervisor,SVC) : 管理模式是CPU上电后默认模式,因此在该模式下主要 用来做系统的初始化,软中断处理也在该模式下。系统复位或开机、软中断时进入到SVC模式下。

(6)中止模式(ABT): 中止模式用于支持虚拟内存或存储器保护,当用户程序 访问非法地址,没有权限读取的内存地址时,会进入该模式。

(7)未定义模式(UND): CPU在指令的译码阶段不能识别该指令操作时,会进入 未定义模式,进行未定义陷阱处理。

软中断和硬中断相关知识可参考以下链接1

- 特权模式 除用户模式外的其它6种处理器模式称为特权模式 (Privileged Modes)。在特权模式下,程序可以访问所有的系统资源,也可以任意的进行处理器模式切换。 只有在特权模式下才允许对当前程序状态寄存器(CPSR) 的所有控制位直接进行读/写访问,而在非特权模式下只允许 对CPSR的控制位进行间接访问(SWI方式)。

SWI中断指令2

- 异常模式 特权模式中除系统模式之外的其他5种模式又统称为异常 模式。它们除了可以通过在特权下的程序切换进入外,也可 以由特定的异常进入。其中管理模式也称为超级用户模式, 是为操作系统提供软中断的特有模式。 大多数的用户程序运行在用户模式下。当处理器工作在 用户模式时,需要进行处理器模式切换时,应用程序可以产 生异常处理,在异常处理过程中进行处理器模式切换。这种体系结构可以使操作系统控制整个系统资源的使用。

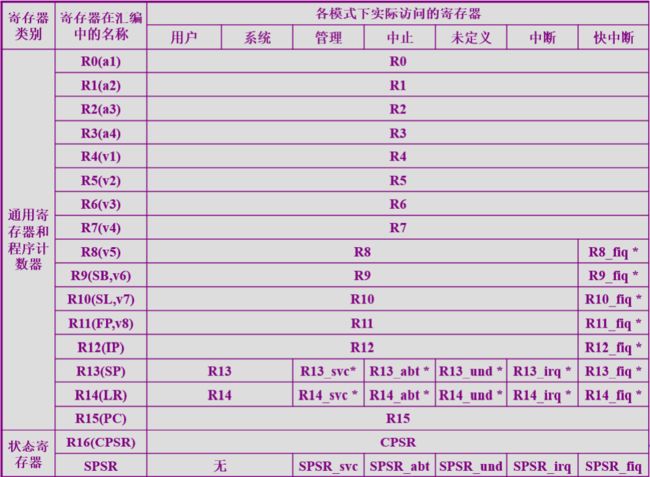

2.6 ARM 寄存器

37个用户可见寄存器

通用寄存器

(1)未分组寄存器,包括 R0~R7; 在所有处理器模式下对于每一个未分组寄存器来说,指 的都是同一个物理寄存器。

(2)分组寄存器,包括 R8~R14。 它们每一个访问的物理寄存器取决于当前的处理器模式。

值得记忆的有名字的寄存器

SP -> 中用户模式和系统模式共用一个,每种异常模式都有专用的R13寄存器。说ARM处理器允许用户程序有6个不同的堆栈空间

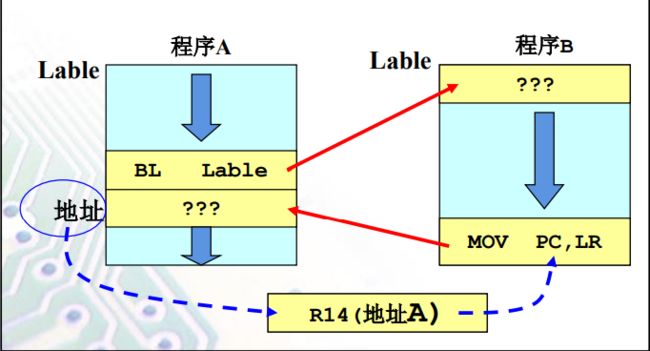

LR ->

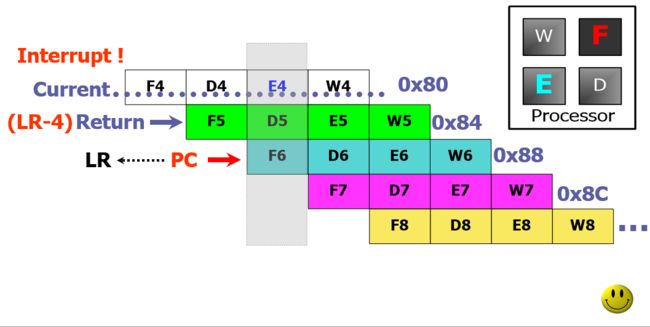

(1)在各种模式下,R14用来保存子程序的返回地址。当一 条BL或者BLX指令执行子程序调用时,R14设为子程序的返回地址。

BL: 带链接的跳转。 首先将当前指令的下一条指令地址保存在LR寄存器,然后跳转的lable。通常用于调用子程序,可通过在子程序的尾部添加mov pc, lr 返回。

更具体的汇编指令在第二章番外章 汇编指令

(2)当发生异常时,相关异常模式下的R14就设为异常返回地 址。异常的返回地址与子程序的返回类似。区别在于有些 异常有一个小常量的偏移。

PC

在ARM状态,位[1:0]为0,位[31:2]保存PC。在Thumb状态,位[0]为0,位[31:1]保存PC。

bit[m:n]表示从第n位到第m位

程序计数器R15(即PC)总是指向**“正在取指”的指令,而不是指向“正在执行”**的指令或正在“译码”的指令。

不再是PC+“1”

PC总是指向第3条指令,或者说PC总是指向当前正 在执行的指令地址再加2条指令的地址

具体区别看是ARM状态还是Thumb状态

状态寄存器

-

cpsr

(CPSR)可以在任何处理器模式下被访问 -

spsr

每一种异常器模式下,都有一个专用的物理寄存器做 备份程序状态寄存器(SPSR: SavedProgram Status Register )。当特定的异常中断发生时,这个物理寄存器 负责存放当前程序状态寄存器的内容。当异常处理程序返 回时,再将其内容恢复到当前程序状态寄存器。

标志位

- 条件标志位

这些条件标志位会根据程序中的算数指令或逻辑指令的 执行结果进行改变,而且这些条件标志位可由大多数指令检 测以决定指令是否执行。

- Q标志位(了解)

- 控制位

ARM与Thumb的寄存器

ARM状态寄存器与Thumb状态寄存器有如下的关系:

① Thumb状态R0 ~ R7与ARM状态R0 ~ R7相同。

② Thumb状态CPSR(无SPSR)与ARM状态CPSR相同。 由于Thumb指令集不包含MSR和MRS指令,如果用户 需要修改CPSR的任何标志位,必须回到ARM模式。

③ Thumb状态SP映射到ARM状态R13;

④ Thumb状态LR映射到ARM状态R14;

⑤ Thumb状态PC映射到ARM状态R15(PC)

注意:所有的异常处理都是在ARM状态下执行的,在Thumb 状态下,如果有任何中断或者异常标志出现,那么处理器就 会自动切换到ARM状态去进行异常处理,当异常处理完毕返 回时,处理器又会自动切换返回到Thumb状态,状态切换过 程如下图所示。

寄存器 R8~R12为高端寄存器。

Thumb状态中访问高端寄存器

MOV、ADD、CMP才能访问高端寄存器

2.7 ARM 存储系统

采用冯诺依曼体系,指令和数据共用一条32位数据线

只有装载、存储和交换指令可访问存储器中的数据。

在大端模式下,一个字的高地址放的是数据的低位;而在小端模式下,数据的低位放在内存中低地址。

ARM指令集不包含任何直接选择大小端存储器格式的指令

基于ARM的芯片可以通过硬件配置

对于S3C2440是通过软件来指定存储器格式的

存储器映射I/O

基于ARM内核的芯片具有许多的外设,这些外设访问的 标准方法是使用存储器映射的I/O(存储器统一编址),为外设的每个寄存器都分配一个地址。

2.8 中断和异常的基本概念(不考)

2.9 ARM 的异常 7种

ARM异常与中断不做严格意义上的区别。

ARM处理器可以响应的中断(异常)有:中断、快中断、 复位中断、软中断异常、预取指令中止异常、数据中止异常 和 未定义指令异常 7 种

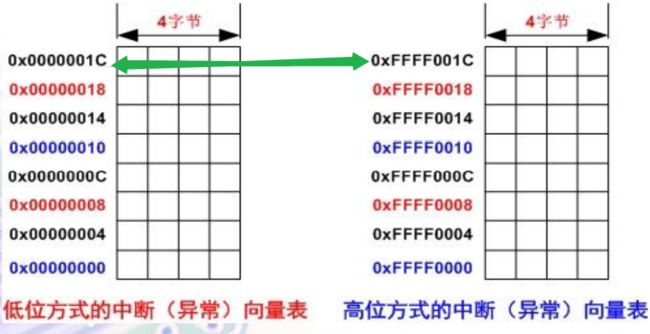

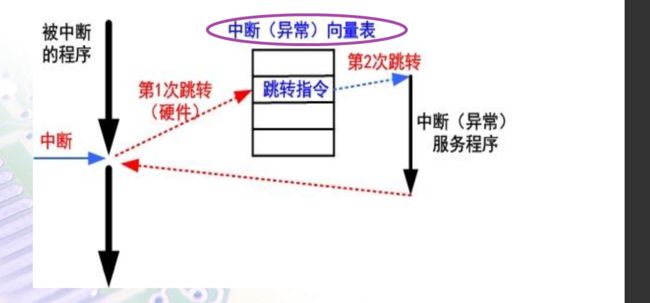

2.9.1 ARM的中断(异常)向量表

公共入口设置的必要性 记得当时讲的是堆栈

ARM有低端和高端两种向量表

2.9.2 ARM异常响应

一、进入异常 在异常发生后,ARM内核会作以下工作:

-

在适当的LR中保存下一条指令的地址,当异常入口来自: 无论是ARM状态还是Thumb状态,ARM都将当前运行指令地址加4或加8复制(取决于异常的类型) 到LR中;

-

把当前程序状态寄存器(CPSR)中的内容保存到模式私 有寄存器SPSR中;2.9 ARM的中断(异常)

-

将寄存器CPSR中的MODE域设置为中断(异常)应进入 的运行模式;

-

对CPSR的I位和F位进行相应的设置,以防止再次响应同 一个中断请求。

-

强制PC从相关的异常向量处取指,即到中断向量表中获 取中断向量,转向用户所编写的中断(异常)服务程序。 注:异常总是在ARM状态中进行处理。当处理器处于 Thumb状态时发生了异常,在异常向量地址装入PC时,会 自动切换到ARM状态。

二、异常返回

当异常结束时,异常处理程序必须做如下处理:

- 将SPSR的值复制回CPSR

- 将LR中的值减去偏移量后存入PC,偏移量根据异常

的类型而有所不同。

另一个东西+4或者+8根据流水线来决定,

有回写就是-8

无回写就是-4

程序执行时,PC的初值为程序第一条指令的地址

第2章 番外 汇编指令

MRS MSR

- MRS:M—move,R—表示通用寄存器,S—表示特殊寄存器,

- CPSID I:快速屏蔽中断,所有中断(除NMI,复位中断,还有硬件中断)

- BX LR:返回LR

ldr命令:把数据从内存加载到寄存器。

str命令:把数据从寄存器保存到内存。

第3章 ARM指令集

1、ARM指令集简介

一、用助记符表示的ARM指令

所有的指令长度 都是32位 ,并且大多数指令都在一个单独指令周期内执行。

-

指令是条件执行的;

-

ARM微处理器的指令集是加载/存储型的;

-

在多寄存器操作指令中一次最多可以完成 16个寄存器的数据传送

指令ADDEQS R0,R1,#8;

执行结果:R0 = R1+ 8

不带S,计算结果不影响CPSR寄存器。

加上后缀EQ,表示“满足条件相等则跳转”

二、指令的机器码

用32位的二进制数表示

三、指令的可选后缀

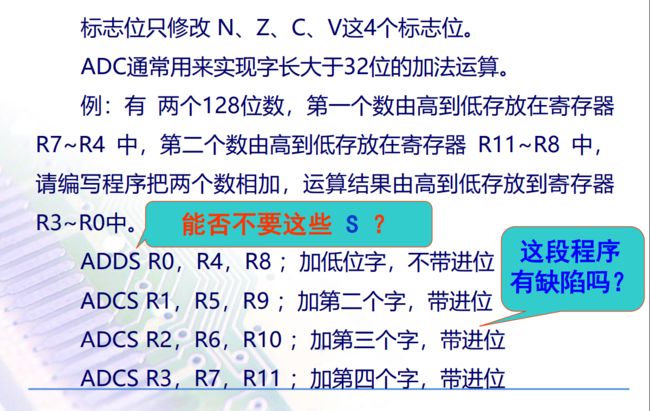

- S 后缀 指令中使用S后缀时,指令执行后程序状态寄存器的条件标 志位将被刷新

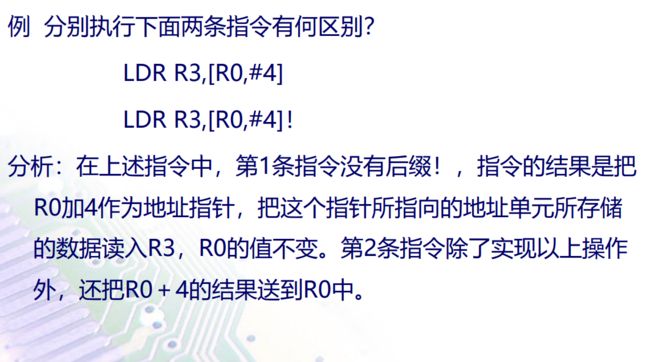

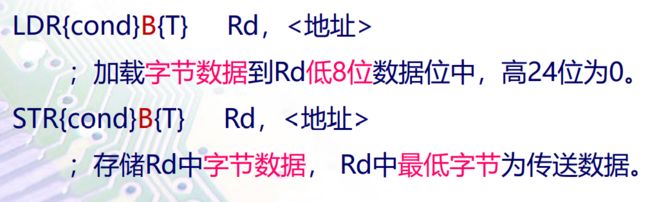

2) ! 后缀 如果指令地址表达式中含!

基址寄存器中的值(指令执行后)=指令执行前的值+地址偏移量

3)B后缀 B后缀的含义是:指令所涉及的数据是一个字节,

![]()

ARM 指令可以分为:

分支指令

数据处理指令

存储访问指令

协处理器指令

杂项指令五类

2、ARM指令寻址方式

这个图很重要

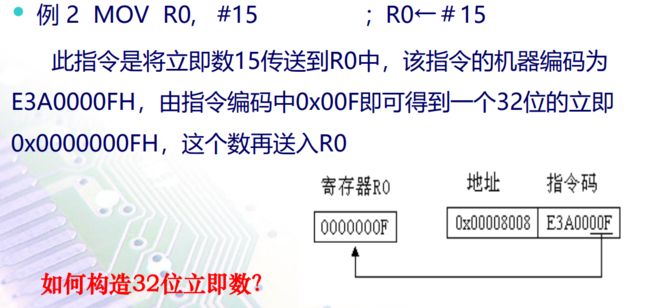

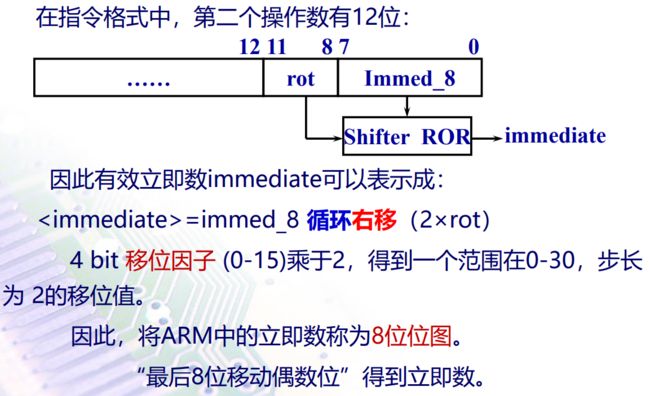

3.2.1 立即数寻址 8位位图法很重要

如何判断该立即数是否合法

8位位图

operand2的常数表达式有如下规定:“该常数必须对应8位位图,即常数是由一个8位的常数循环右移偶数位得到的。

我们可以从图片中看出:一条指令的后 12 位(bit 11~0),是指令中立即数占用的位数。其中这 12 位又分为两部分:前 7~0 位是数值部分;后 11~8 位是前 7~0 位要进行移位操作的移位数。3

如果一个立即数小于 0xFF(255)那么直接用前 7~0 位表示即可,此时不用移位,11~8 位的 Rotate_imm 等于 0。

如果前八位 immed_8 的数值大于 255,那么就看这个数是否能有 immed_8 中的某个数移位 2*Rotate_imm 位形成的。如果能,那么就是合法立即数;否则非法。

记得一定是移位偶数个

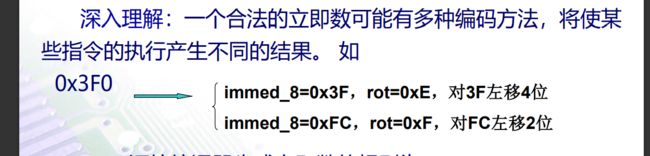

嘿我悟了

判断小技巧3

快速判断一个数是不是有效立即数的方法是看从左至右0的个数是否为偶数

我来解释一下:比如上面那个 #0x0000f200,其中我们猜测 Immed_8 为 1111 | 0010,这个数右边还有 0000 | 0000 |,是偶数个 0,因此是有效立即数。而我们看 0x132,我们猜测 Immed_8 为 1001 | 1001,右边只有一个 0,因此不是有效立即数。

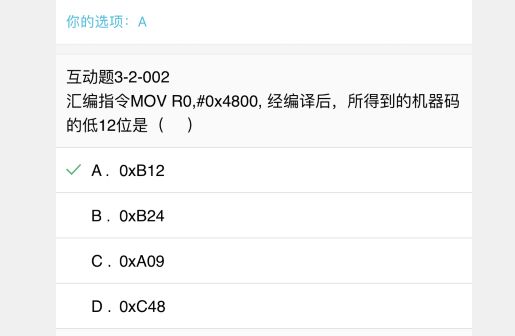

==这个题要使得偏移量最小!!!==真尼玛阴间

由机器码得到4800 并且偏移量最小

C48固然可以,但是偏移量是24

1011 0001 0010 右移 22 位变成 10|01 00|01 00|10 00|00 00|00 00

4 8 0 0

A: 0001|0011|0010 奇数

B: 0010|0110|0100 偶数

C: 0010|0110|0110 奇数

D: 0100|1100|1000 奇数

给定立即数0x00012800,求立即寻址时,指令的低12位是什么?4

可以看到,这个题目是例1的反向求解,已知立即数求指令

首先,将立即数转换为二进制0000 | 0000 | 0000 | 0001 | 0010 | 1000 | 0000 | 0000

第二步,将二进制中的关键8位提取出来,因为循环移位必定是移动偶数位的,所以我们提取的时候要保证我们找的关键8位在原二进制中是处于偶数位的

因此在这里我们提取的是01 | 0010 | 10,而不是1 | 0010 | 100(这里的|对应原二进制|的位置,便于读者观察),关键8位的16进制表示为0x4a

第三步,将提取出来的关键8位放到二进制的最右边,构成一个待移动二进制串

0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0100 | 1010

第四步,对第三步的待移动二进制串进行循环右移操作,使得循环右移后的结果与原二进制串一致,记录移动的位数,即

0000 | 0000 | 0000 | 0000 | 0000 | 0000 | 0100 | 1010 循环右移 => 0000 | 0000 | 0000 | 0001 | 0010 | 1000 | 0000 | 0000

得移动位数为22位,等于0xb * 2

第五步,合并第二步得到的关键8位和第四步的移动位数,为0xb4a

3.2.2 寄存器寻址

3.2.3 寄存器移位寻址

- 寄存器移位寻址

- 第二操作数移位方式

当第二操作数为寄存器型时,在执行寄存器寻址操作时,也可以对第二操作数寄存器进行移位,此时第二操作数形式为: ADD Rd, Rn, Rm,{shift} 其中: ➢Rm 称为第二操作数寄存器

LSL 逻辑左移 空出的最低有效位用0填充。

LSR 逻辑右移 空出的最高有效位用0填充。

ASL 算术左移 LSL同

ASR 算术右移 如果源操作数是正数,空出的最高有效位用0填充,如果是负数 用1填充。

ROR 循环右移

RRX 带扩展的循环右移 将寄存器的内容循环右移1位,空位用原来C标志位填充

- 第二操作数的移位位数

可有立即数或是寄存器给出

3.2.4 寄存器间接寻址

操作数本身存放在存储器中

3.2.5 基址变址寻址

-

前变址

先基址+偏址,生成操作数地址,再做指令指定的操作

STR r0,[r1,#12] -

自动变址

先基址+偏移,生成操作数地址,做指令指定的操作。然后自动修改基址寄存器。

LDR R0,[R1,#4]! //这里有感叹号 -

后变址寻址

基址寄存器不加偏移作为操作数地址。

完成指令操作后,用(基址+偏移)的值修改基址寄存器。

STR r0,[r1],#12 // 注意[]位置

3.2.6 多寄存器寻址

用一条指令最多可传送16个通用寄存 器的值。连续的寄存器间用“-”连接,否则用“ , ”

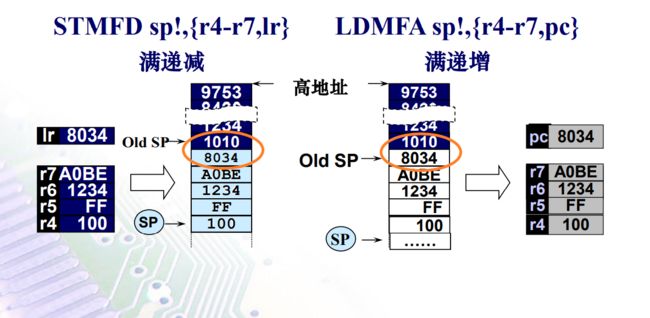

对于所有LDM/STM指令而言,寄存器序号低的,在低地址单元,序号大的在高地址单元!

即LR等先于R0等入栈出栈

3.2.7 堆栈寻址

LDMIA/STMIA Increment After(先传送,后地址加4)

LDMIB/STMIB Increment Before(先地址加4 ,后传送)

LDMDA/STMDA Decrement After(先传送,后地址减4)

LDMDB/STMDB Decrement Before (先地址减4,后传送)

满递增堆栈FA(Full Ascending):堆栈指针指向最后压 入的数据,且由低地址向高地址生长。

满递减堆栈FD(Full Descending ) :堆栈指针指向最后 压入的数据,且由高地址向低地址生长。

空递增堆栈EA(Empty Ascending):堆栈指针指向下一 个将要放入数据的空位置,且由低地址向高地址生长。

空递减堆栈ED(Empty Descending):堆栈指针指向下一 个将要放入数据的空位置,且由高地址向低地址生长。

重点在D和A上

注意入栈出栈第一个操作数是多少

3.2.8 相对寻址

好像不是很重要来着唉嘿

3、ARM指令集

3.3.1 分支指令

跳转指令 B 及带连接的跳转指令 BL

写汇编程序时,可以跳转到一个绝对地址,

B 0x1234

编译器会把该绝对地址转换为相对地址放入指令中

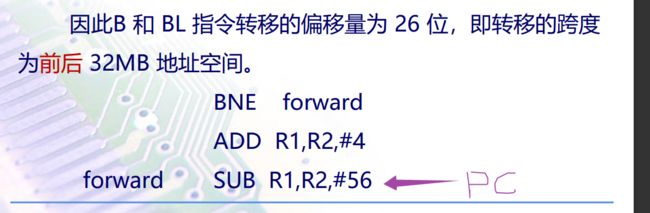

signed_immed_24 间接提供目标地址,真正的目标地址是由处理器根据这个有符号数和当前的PC值计算出来的。

具体计算为:先将 signed_immed_24 左移两位(即具有26位的偏移量),并扩展为32位有符号数,然后再将这32位有符号数与 PC 的当前值相加,得到实际的跳转地址。

因此B 和 BL 指令转移的偏移量为 26 位,即转移的跨度为前后 32MB 地址空间。

所以这个题的偏移量是0,流水线的缘故

带状态切换的跳转指令BX

BX 指令的格式为: BX{} Rm

• cond表示指令执行条件

• Rm[0]为1时,强制程序从ARM指令状态跳转到Thumb指令状态。

• Rm[0]为0时,强制程序从Thumb 指令状态跳转到ARM指令状态。

• 功能: 跳转到指令中所指定的目标地址,并实现状态切换

• Rm寄存器,值是绝对地址值,不是偏移量,在指令执行后,Rm中的地址值与#0XFFFF FFFE 进行 “与” 运算,再被复制到程序计数器PC。

把除了最后一位的其他位置1有什么用

•(T<-Rm[0])

下图为 CPSR

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-LpqbTWZR-1616828615699)(C:\Users\24482\AppData\Roaming\Typora\typora-user-images\image-20210326164922581.png)]

3.3.2 数据处理指令

1、ARM数据处理指令的功能

主要完成寄存器中数据的算术和逻辑运算操作。

2、ARM数据处理指令的特点

• 操作数来源:所有的操作数要么来自寄存器,要么来自立即数,不会来自存储器。

• 操作结果:如果有结果,则结果一定是为32位宽、或64位宽(长乘法指令),并且放在一个或两个寄存器中,不会写入存储器。

• 有第二个操作数(除了乘法指令) Operand2 :切记其三种形式:立即数、寄存器、寄存器移位。

• 乘法指令的操作数:全部是寄存器。

数据处理指令对程序状态寄存器CPSR的影响:

比较指令 (CMP和CMN)

测试指令 (TST和TEQ) 不需要后缀S,它们总会直接影响CPSR中的状态标志。

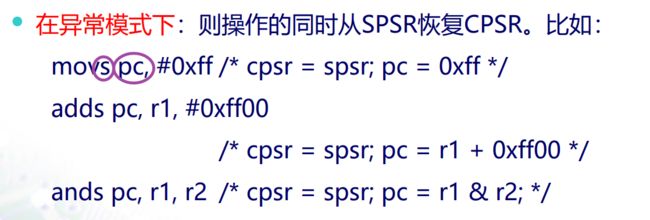

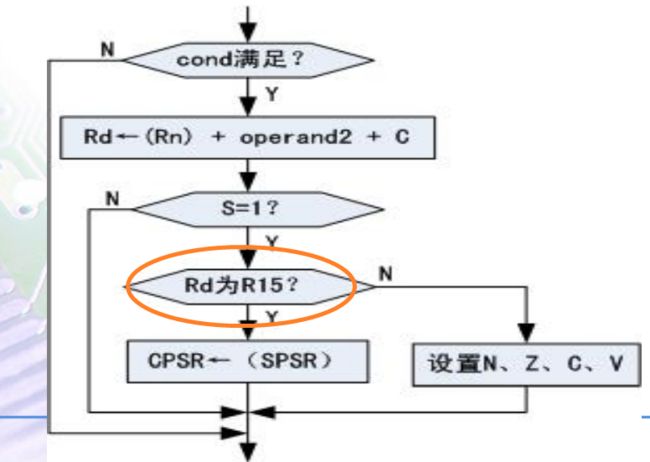

关于恢复CPSR原值问题:

如果指令带有S后缀(除了比较指令以外),同时又以PC为目标寄存器进行操作:

• 在异常模式下:则操作的同时从SPSR恢复CPSR

用户和系统模式下无spsr

不可以因为不符合8位位图

流程

要注意是否是PC的操作

不行,因为有进位的要求

逆(反)向减法指令

RSB——逆(反)向减法指令

指令格式:RSB{cond}{S} Rd,Rn,operand2

RSB指令用operand2减去寄存器Rn,结果保存到Rd中

设置原因:

op2不可为立即数

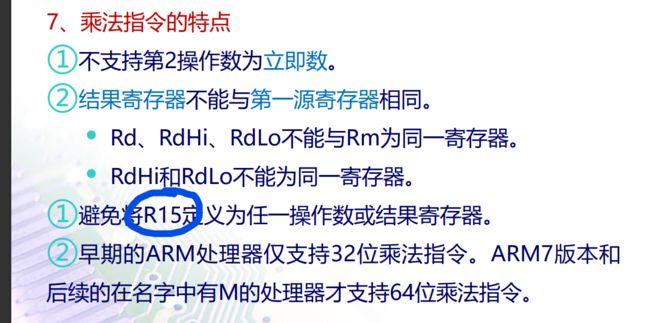

乘法

指令格式:

MUL指令将Rm和Rs中的值相乘,结果的低32位保存到 Rd中。 注:Rd ≠ Rm (不能是一样的)

且PC不可以

MUL——32位乘法指令

MUL{cond}{S} Rd,Rm,Rs;Rd←Rm*Rs

MLA——32位乘加指令

MLA{cond}{S} Rd,Rm,Rs,Rn; Rd←Rm*Rs+Rn

UMULL—64位无符号乘法指令

UMULL{cond}{S} RdLo,RdHi,Rm,Rs; RdHi, RdLo← Rm*Rs

低32位保存到RdLo中,高32位保存到RdHi中

UMLAL—64位无符号乘加指令

UMLAL{cond}{S} RdLo,RdHi,Rm,Rs;RdHi, RdLo← Rm*Rs+ RdHi, RdLo

64位乘积与RdHi、RdLo相加

SMULL—64位有符号乘法指令

SMULL{cond}{S} RdLo,RdHi,Rm,Rs; RdHi, RdLo← Rm*Rs

SMLAL—64位有符号乘加指令

SMLAL{cond}{S} RdLo,RdHi,Rm,Rs; RdHi, RdLo← Rm*Rs+ RdHi, RdLo

暂时没有很懂有符号和无符号的CPSR区别

逻辑运算指令

AND{cond}{S} Rd,Rn,operand2; OP2 AND Rn -> Rd

ORR{cond}{S} Rd,Rn,operand2; OP2 OR Rn -> Rd

EOR{cond}{S} Rd,Rn,operand2; 异或

BIC{cond}{S} Rd,Rn,operand2

;BIC指令将寄存器Rn的值与operand2的值的反码按位逻

;辑“与”操作,结果保存到Rd中。

MOV

CMP

CMP{cond} Rn,operand2;

但不存储运算结果,只根据操作的结果更新CPSR中的相应条件标志

CMP指令与SUBS指令的区别

是否保存结果

CMN

CMN指令将寄存器Rn的值减去operand2的负数(即加上operand2的值)

CMN R0,#-1 也不可以,其-1的补码是不可以当作立即数的

什么时候是补码 负数的存在形式就是补码

TST 按位与

TST{cond} Rn,operand2;

TST R0,#0x01 ;判断R0的最低位是否为0

TEQ 按位异或

3.3.3 存储器访问指令

由于ARM处理器对外设寄存器、I/O映射空间与存储器统一编址因此,对外围设备的I/O操作也用此类指令。

- LDR和STR,单寄存器加载/存储指令

- LDM和STM,多寄存器加载/存储指令 16个

- SWP,寄存器和存储器数据交换指令

3.3.3.1 单寄存器的存取指令

寄存器和存储器间传

送单个字节和字的最灵活方式

- 单字和无符号字节的加载/存储指令

- 半字和有符号字节的加载/存储指令

有符号数和无符号数的扩展

无符号数添 0

单字和无符号字节的加载/存储指令

T是特权模式下把他当作用户模式

什么是特权模式

用于存储器保护 避免越界操作,因为用户模式的限制比较多

半字和有符号字节的加载/存储指令

3.3.3.2 多寄存器的存取指令

spsr作用

3.3.4 协处理器指令

3.3.5 杂项指令

参考文献

如果链接失效还请麻烦各位自己找寻下相关消息~ :happy:

SWI

ARM 立即寻址之立即数的形成 —— 如何判断有效立即数

%E4%B8%AD%E6%96%AD%E5%92%8C%E7%A1%AC%E4%B8%AD%E6%96%AD%E7%9A%84%E5%8C%BA%E5%88%AB

软硬中断的相关知识

SWI

ARM 立即寻址之立即数的形成 —— 如何判断有效立即数

一个立即数寻址的题目

https://blog.csdn.net/ll148305879/article/details/90902282?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522161651054116780261931023%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fall.%2522%257D&request_id=161651054116780261931023&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2allfirst_rank_v2~rank_v29-2-90902282.pc_search_result_cache&utm_term=%E8%BD%AF%E4%B8%AD%E6%96%AD%E5%92%8C%E7%A1%AC%E4%B8%AD%E6%96%AD%E7%9A%84%E5%8C%BA%E5%88%AB

软硬中断的相关知识 ↩︎https://blog.csdn.net/zqixiao_09/article/details/50776191?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522161651119016780269888720%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fall.%2522%257D&request_id=161651119016780269888720&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2allfirst_rank_v2~rank_v29-2-50776191.pc_search_result_cache&utm_term=swi ↩︎

https://blog.csdn.net/sinat_41104353/article/details/83097466?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522161667555916780274187148%2522%252C%2522scm%2522%253A%252220140713.130102334.pc%255Fall.%2522%257D&request_id=161667555916780274187148&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2allfirst_rank_v2~rank_v29-1-83097466.pc_search_result_cache&utm_term=ARM%E7%AB%8B%E5%8D%B3%E6%95%B0%E5%AF%BB%E5%9D%80 ↩︎ ↩︎

https://blog.csdn.net/qq_35544379/article/details/105006517 ↩︎