AD9361 介绍 (上)

AD936x 系列快速入口

增益控制、时钟和PLL、ENSM 在AD9361 介绍 (中)

MGC、Slow AGC、Fast AGC补充: AD9361 补充(上)

通过AD936x Evaluation Software加深了解: AD936x 配置软件介绍 上

为什么复信号可以具有任意频谱结构 复信号频谱

为什么正交采样(复采样)的采样率最低为信号带宽B,就可保证采样信号信息不丢失?:正交采样(复频率域角度)

正在进行 OFDM调制(一)…

文章目录

- 学习资料

- 一、结构

- 二、辅助功能

-

- 2.1 AuxDAC(Auxiliary DAC)

- 2.2 AuxADC(Auxiliary ADC)

- 2.3 内部温度传感器

- 2.4 GPO

- 三、接收链

- 四、传输链

- 五、滤波器

-

- 5.1 接收链路滤波器

-

- 5.11 Rx TIA LPF

- 5.12 Rx BB LPF

- 5.13 Rx HB3/DEC3

- 5.14 Rx HB2

- 5.15 Rx HB1

- 5.16 Rx FIR

- 5.2 发送链路滤波器

-

- 5.21 Tx FIR

- 5.22 Tx HB1

- 5.23 Tx HB2

- 5.24 Tx HB3/INT3

- 5.25 Tx BB LPF

- 5.26 Tx Secondary LPF

学习资料

1. ADI官方资料

2. AD9361 Reference Manual UG-570 和 Register Map Reference Manual UG-671

3. Data Sheet

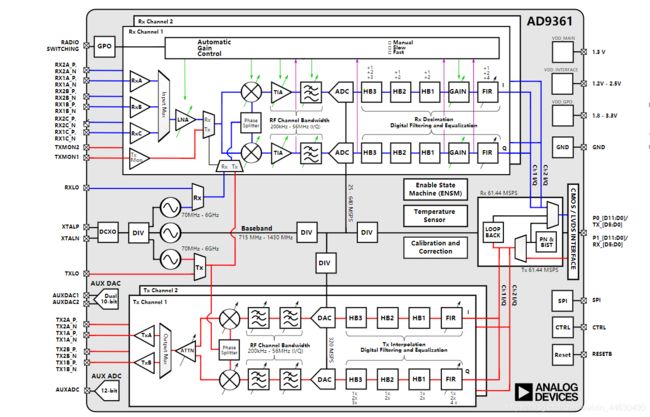

一、结构

二、辅助功能

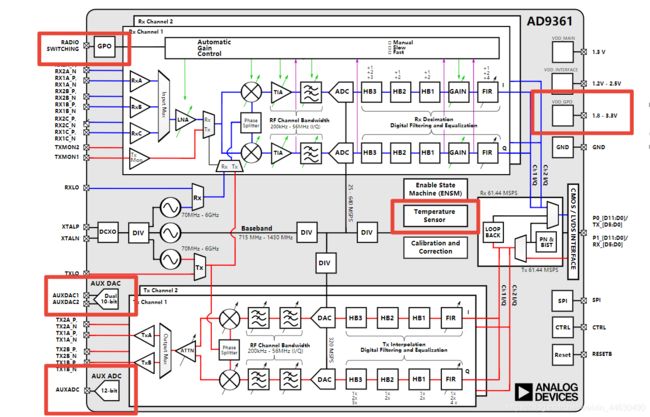

AD9361中的辅助功能——两个10位辅助 DAC,一个12位辅助 ADC,一个内部温度传感器,以及四个通用输出(GPO)引脚,这些功能有助于简化系统任务及降低总体系统成本。

2.1 AuxDAC(Auxiliary DAC)

AuxDAC是10位通用DAC, 可以将 AuxDAC 设置为手动操作,也可以设置为在TDD 操作期间自动切换,以减少对 BBP 的控制要求。AuxDAC 使用 ad9361_auxdac _ setup 函数进行配置。默认情况下,当设备第一次启动时,AuxDAC是禁用的。

在某些应用中,最好在使能信号转换后延迟AuxDAC转换。每个AuxDAC在寄存器0x30至寄存器0x33中都有自己的接收和发送模式延迟设置。每个LSB约等于1 微秒。寄存器0x3A必须根据参考时钟设置来配置1 微秒的延迟,将位[D6:D0]设置为每微秒参考时钟周期数减1。

2.2 AuxADC(Auxiliary ADC)

AuxADC是一个12位的辅助转换器,其输入电平范围为0 V到1.3 V,转换时间可调。AuxADC通过ad9361_auxadc_setup函数进行配置。

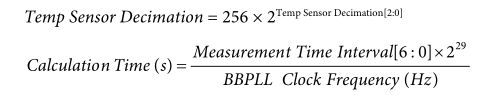

默认情况下,AuxADC关闭。AuxADC时钟通过分频基带锁相环频率产生。上式决定了AuxADC时钟频率和抽取率。

AD9361包括一个内部温度传感器,可以使用AuxADC测量。AuxADC在同一时刻只能测量内部温度或AuxADC引脚上的电压。

- AuxADC默认是关闭的,其时钟是由基带锁相环频率分频产生的。

2.3 内部温度传感器

要用AuxADC测量温度,可以使用ad9361_auxadc_setup函数配置,然后使用ad9361_get_temp函数进行读取。温度字的斜率约为1.14 LSB/℃。需要单点factory 或 bench 校准来将绝对温度与温度字相等。

寄存器0x0F的位[D2:D0]根据上式设置温度传感器模式下AuxADC的抽取率,寄存器0x0D的位D7:D1根据上式设置温度传感器定期读取温度读数的速率。如果要手动执行温度测量(寄存器0x0D的位D0清零),则当寄存器0x0C的位D0(开始温度读数)置位时,测量开始。

- 测量温度时,AuxADC的时钟频率被设置为BBPLL频率的64分频。

2.4 GPO

AD9361有四个GPO引脚,可以使用ad9361_gpo_setup函数设置,GPO可以控制天线开关或LNA使能。控制GPO有两种选择,在BBP中通过SPI手动写,或通过ENSM自动控制。

当使用外部LNA时,AD9361可以选择从接收增益表中选择GPO_0和GPO_1,以控制两个接收通道中每一个的LNA增益。GPO的供电电压来自AD9361上的引脚VDD_GPO (B8)。

设置寄存器0x026的位D4可将GPO置于手动控制模式。使用寄存器0x027的高位半字节(四位)作为GPO逻辑电平控制。GPO_3使用D7;GPO_2使用D6,GPO_1使用D5,GPO_0使用D4。为0时,GPO为逻辑低电平。为1时,GPO为逻辑高电平。在这种模式下,寄存器0x26的低位半字节被忽略。

为ENSM控制 GPOs 时, GPOs 的初始状态应设置在寄存器0x27的下半字节,其中 GPO_0对应位D0, GPO_1对应位D1, GPO_2对应位D2, GPO_3对应位D3。为0时,在 sleep, wait,和alert状态下,GPO为逻辑低电平,为1时,GPO为逻辑高电平。

寄存器0x20包含决定GPO如何响应 从Alert状态变化的位。上半字节控制哪些GPO引脚在进入接收模式时会改变状态,下半字节控制哪些GPO引脚在移到发送模式时会改变状态。例如,假设寄存器0x26为0x00 (ENSM控制使能),寄存器0x27为0xFF(将所有GPO引脚初始化为1),寄存器0x20 = 0x24(在接收端切换GPO_1引脚,在发送端切换GPO_2引脚)。当器件进入报警状态时,所有GPO引脚将变为高电平。当器件进入Tx时,只有引脚GPO_2引脚会变为低电平。当器件进入Rx时,GPO_1引脚将切换为低电平。

有些应用需要在DUT状态转换和GPO引脚切换之间插入延迟。为了满足这些需求,可以将GPO寄存器编程到所需的延迟。寄存器0x28至寄存器0x2B设置从alert状态变化到接收的延迟,而寄存器0x02C至寄存器0x02F设置从 alert 状态变化到发送的延迟。每个LSB为1µs。延迟设置仅在TXNRX和ENABLE引脚用于控制状态机时有效。当使用SPI控制状态机时,延迟设置将不起作用。根据参考时钟,将寄存器0x3A分辨率为1 µs/LSB。将位[D6:D0]设置为每微秒参考时钟周期数减1。在FDD模式下,应用 Tx enable和Tx delays ,忽略Rx enable 和 Rx delays 。

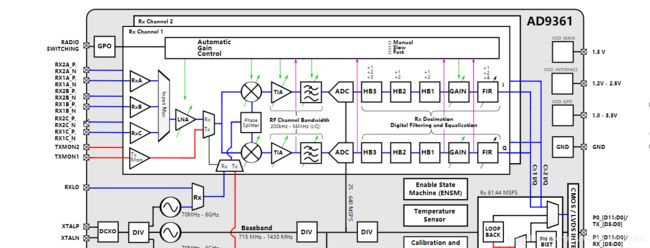

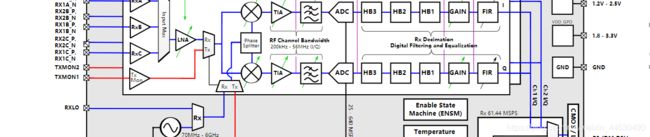

三、接收链

AD9361接收部分有两个独立控制的通道Rx Channel 1 和 Rx Channel 2 可以接收来自不同来源的信号,从而允许该设备在共享通用频率合成器的同时在多输入多输出(MIMO)系统中使用。

每个通道具有三个输入,这些输入可以多路复用到信号链,从而使AD9361适用于具有多个天线输入的分集系统。接收链数据首先经过低噪声放大器(LNA),然后是同相(I)和正交(Q)放大器,混频器和频带整形滤波器,可将接收到的信号下变频为基带以进行数字化。

基带RX信号路径由两个可编程模拟低通滤波器,一个12位ADC和四级数字抽取滤波器组成。四个抽取滤波器中的每一个都可以被旁路。每个低通滤波器的转折频率是可编程的。

- 接收器LNA输入端口可以在单端模式(差分输入的任一侧都可以用作单端输入)或差分模式下使用(建议将LNA输入配置为差分模式,以实现最佳噪声系数)

- RxA RxB RxC :三个输入。RX1A_N, RX1A_P 接收通道1的差分输入A。每个引脚都可作为单端输入将未使用的引脚接地,或者一起形成差分对。

- Input Mux :多路复用

- LNA:低噪声放大器

- TIA: 跨阻抗放大器,位于混频器和Rx基带模拟滤波器之间,3dB角点频率可编程,当调用ad9361_set_rx_rf_bandwidth函数时,对Rx TIA的3dB频率进行编程。

- BB LPF是一个三阶巴特沃斯低通滤波器,具有可编程的3 dB角频。

- ADC:12位sigma-delta(Σ-Δ)ADC

- HB1 HB2 HB3 :半带滤波器,数字滤波器

- FIR :数字滤波器,是一个可编程的多相FIR滤波器

- 当工作频率等于或低于3 GHz时,任何LNA输入端口都将提供最佳性能, 当工作频率高于3 GHz时,利用Rx1A和Rx2A LNA输入端口获得最佳性能,B和C端口在3 GHz以上时性能会下降

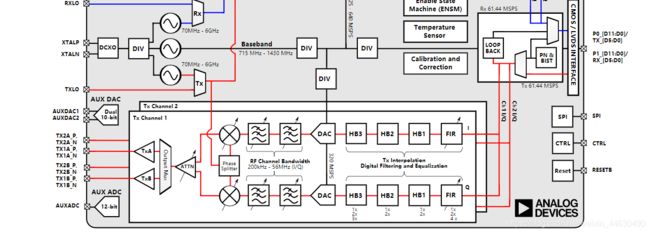

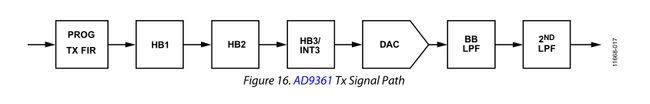

四、传输链

AD9361发送部分由两个相同且独立控制的通道Tx Channel 1 和 Tx Channel 2 组成,同时共用一个通用型频率合成器。

TX信号路径从数字接口接收IQ格式的12位补码数据,并且每个通道(I和Q)通过具有内插选项的完全可编程的128抽头FIR滤波器。之后进入到一系列附加的插值滤波器,这些滤波器在到达12位DAC之前提供附加的滤波和数据速率插值。如果需要,可以分别控制和旁路FIR滤波器以及三个插值滤波器。

- FIR :数字滤波器,是一个可编程的多相FIR滤波器。

- HB1 HB2 HB3 :半带滤波器,数字滤波器

- DAC:12位DAC

- BB LPF:是一个三阶巴特沃斯低通滤波器,具有可编程的3 dB角频l率。

- Secondary LPF : Tx次级LPF是一个单极低通滤波器,具有可编程的3 dB角频率。

- Ouput Mux :多路复用

- TxA TxB :两个输出,TX2A_N, TX2A_P,发射通道2差分输出A, 发送器输出端口只能在差分模式下使用

当转换为基带模拟信号时, I和Q信号将进行滤波,以移除采样伪像,然后进入上变频混频器使 I和Q信号将重新组合起来,并在载波频率下进行调制。组合信号还会通过模拟滤波器,进行额外的频带整形处理,然后再将信号传输至输出放大器。

发送器模块还为每个通道提供一个TX监控模块。该模块监视发送器输出,并通过一个未使用的接收器通道将其送回BBP,以实现信号监控。 TX监控器模块仅在接收器空闲的TDD模式下可用。

- TX MON 1:发射通道1功率监控输入,若未使用此引脚,则将其接地。

- TX MON 2:发射通道2功率监控输入,若未使用此引脚,则将其接地。

五、滤波器

5.1 接收链路滤波器

AD9361 Rx信号通路由两个可编程模拟低通滤波器、一个12位ADC和四个阶段的数字抽取滤波器组成。四个抽取滤波器都可以被旁路。ADC前的模拟低通滤波器用来降低杂散信号水平。这些滤波器的角点频率是用ad9361_set_rx_rf_bandwidth函数调用编程的。

由正交采样(复频率域角度)可知,AD9361 正交采样时I路和Q路 直接将信号搬到了0中频,低通滤波器为B/2即可,每个A/D采样率最低为复信号带宽B就不会出现频谱混叠,完整得到原信号所携带的信息。

5.11 Rx TIA LPF

Rx TIA LPF是一个单极低通滤波器,具有可编程的3 dB角频率。转角频率可在1 MHz至70 MHz范围内编程。Rx TIA LPF通常被校准到基带信道带宽的2.5倍。AD9361 最大接收信号带宽B为56MHz, B/2为28MHz,3 dB角频率校准到基带信道带宽的2.5倍,28*2.5=70MHz,正好转角频率可在1 MHz至70 MHz范围内编程。

5.12 Rx BB LPF

Rx BB LPF是一个三阶巴特沃斯低通滤波器,具有可编程的3 dB角频。转角频率可编程范围为200 kHz至39.2 MHz。Rx BB LPF通常被校准到基带通道带宽的1.4倍。AD9361 最大接收信号带宽B为56MHz, B/2为28MHz,3 dB角频率校准到基带信道带宽的1.4倍,28*1.4=39.2MHz,正好转角频率可在200 kHz至39.2 MHz范围内编程。

ADC后面的四个模块组成了接收路径的数字滤波,这些可编程滤波器在信号数字化后提供带宽限制以及减少带外噪声与杂散信号,同时对信号进行抽取以生成正确数据速率。在每个滤波器中,抽取是在滤波完成后执行的,每个固定系数滤波器的采样时钟总是等于输入数据时钟,使用ad9361_calculate_ rf_clock_chain函数来配置。

5.13 Rx HB3/DEC3

Rx HB3/DEC3提供了两个不同的固定抽取系数。Rx HB3/DEC3抽取系数为2或3,或者被旁路。抽取系数为2时,Rx HB3的系数如下:[1,4,6,4,1],抽取系数为3时,Rx DEC3的系数如下:[55,83,0,−393,−580,0,1914,4041,5120,4041,1914,0,−580,−393,0,83,55]。

- 如果该滤波器的抽取因子设置为3,那么Tx HB3/INT3滤波器的插值因子也必须设置为3,以便时钟正确对齐。

5.14 Rx HB2

Rx HB2是一个固定系数半带抽取滤波器,可以抽取2倍,也可以被旁路。Rx HB2具有如下系数:[−9,0,73,128,73,0,−9]。

5.15 Rx HB1

Rx HB1是一种固定系数半带抽取滤波器,可以抽取2倍,也可以被旁路。Rx HB1具有如下系数:[−8,0,42,0,−147,0,619,1013,619,0,−147,0,42,0,−8]。

5.16 Rx FIR

Rx信号路径中的最后一个数字滤波器是一个可编程的多相FIR滤波器。Rx FIR滤波器可以抽取2倍或4倍,如果不需要,可以被旁路。滤波器系数是16个为一组配置的,最小阶数为16,最大为128。

Rx FIR还具有−12 dB,−6 dB, 0 dB,或+6 dB的可编程增益。为最大化动态范围,滤波器提供了固定+6dB增益,因此FIR滤波器可编程增益通常设置为−6dB,以产生0 dB的净增益。

Rx FIR有两个可选的采样时钟,要么ADC_CLK或ADC_CLK/2。

- 采样时钟与滤波器输出数据率的比值乘以16为可用抽头数量。例如,如果输出数据速率为50 MHz,采样时钟为200MHz,那么采样时钟与输出数据速率的比值为200/50=4,可用的抽头总数是4*16=64个。

不像Tx FIR滤波器, Rx FIR有足够的内部内存,可以设置最大数量的抽头用于抽取。如果满足前面描述的时钟比率,所有128个抽头都可以使用。这个滤波器是使用ad9361_set_rx_fir_config函数设置的。

5.2 发送链路滤波器

Tx信号路径从AD9361数字接口接收12位二进制补码I-Q格式的数据,每个通道(I和Q)通过四个数字插值滤波器将该数据传递到12位DAC。四个插值滤波器中的每一个都可以被旁路。在进入射频混频器之前通过两个低通滤波器,ad9361_set_tx_rf_bandwidth函数可对每个低通滤波器的角点频率进行编程。

可编程数字滤波器提供了从数字到模拟转换之前所需的带宽限制,还可以对数据进行插值,从数字接口输入数据速率转换为DAC转换所需的速率,在每个滤波器中,首先进行插值,再滤波。

5.21 Tx FIR

Tx FIR是一个可编程的多相FIR滤波器,Tx FIR滤波器可以内插2或4倍,如果不需要可以被旁路。这个滤波器在ad9361_set_tx_fir_config函数中被配置。滤波器系数是16个为一组配置的,最小阶数为16,最大为128。Tx FIR也有一个可编程的增益——0 dB或−6 dB。

Tx FIR使用DAC_CLK (Tx DAC采样时钟)作为它的采样时钟。DAC_CLK可以设置为ADC_CLK,也可以设置为ADC_CLK/2。

- DAC_CLK与输入数据速率的比值乘以16是可用的抽头数。例如,如果输入数据速率为25 MHz, DAC_CLK为100 MHz,那么DAC_CLK与输入数据速率的比值为100/25=4,可用的抽头总数是4*16=64个。

另一个限制是Tx FIR滤波器内部的内存,如果插值因子设置为1,可用的抽头数量将被限制为64个,如果使用了大于1的插值率,那么可以利用内存空间来包含更多的抽头。

5.22 Tx HB1

Tx HB1是一种固定系数半带内插滤波器,可以内插2倍,也可以被旁路。Tx HB1具有以下系数:[−53,0,313,0,−1155,0,4989,8192,4989,0,−1155,0,313,0,−53]。

5.23 Tx HB2

Tx HB2是一个固定系数半带内插滤波器,可以内插2倍,也可以被旁路。Tx HB2的系数为[−9,0,73,128,73,0,−9]。

5.24 Tx HB3/INT3

Tx HB3/INT3提供了两个不同的固定内插系数。Tx HB3/INT3可以内插2倍或3倍,或者旁路掉。Tx HB3的系数如下:[1,2,1],Tx INT3的系数如下:[36,−19,0,−156,−12,0,479,223,0,−1215,−993,0,3569,6277,8192,6277,3569,0,−993,−1215,0,223,479,0,−12,−156,0,−19,36]。

- 如果这个滤波器的插值因子设置为3,那么Rx HB3/DEC3滤波器的抽取因子也必须设置为3,这样时钟才能正确对齐。

DAC之后的模拟低通滤波器来减少杂散干扰。这些滤波器的角点频率是用ad9361_set_tx_rf_bandwidth函数调用编程的。

5.25 Tx BB LPF

UG570 第10页 有一句 Note that the BBBW is half the complex bandwidth and coerced between 20 MHz to 0.625 MHz 和 问题1:the complex RF bandwidth which should be 2 x BBBW 和 问题2: And transmit the wind noise into the tx path,but the spectrum width is limited as 40Mhz.And if I use the ad9361_set_tx_rf_bandwidth() function to set tx rf bandwidth less than 40Mhz , it works.

Tx BBBW 20 MHz到0.625 MHz,即AD9361 发射信号带宽B为40MHz, B/2为20MHz

Tx BB LPF是一个三阶巴特沃思低通滤波器,具有可编程的3 dB角频。Tx BB LPF角频率可在625 kHz至32 MHz范围内编程,Tx BB LPF通常被校准到基带通道带宽的1.6倍。3 dB角频率校准到基带信道带宽的1.6倍,20*1.6=32MHz,正好转角频率可在625 kHz至32 MHz范围内编程。

5.26 Tx Secondary LPF

Tx Secondary LPF是一个单极低通滤波器,具有可编程的3 dB角频率。在2.7 MHz至100 MHz范围内可编程,Tx Secondary LPF通常被校准到基带通道带宽的5倍。3 dB角频率校准到基带信道带宽的5倍,20*5=100MHz,转角频率可在2.7 MHz至100 MHz范围内编程。

从参考手册和寄存器手册等资料学习总结,如有不对的地方,欢迎大家在评论区指正,非常感谢!