XIlinx提供的DDR3 IP与 UG586

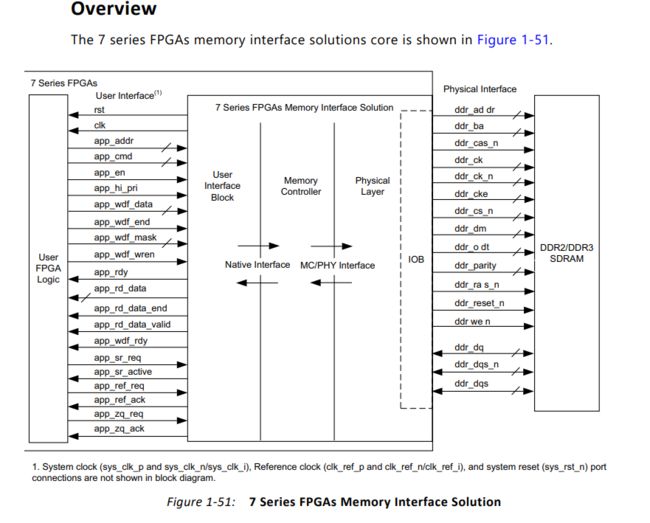

DDR系统需要关注的三样东西:控制器、PHY、SDRAM颗粒,但这是实现一个DDR3 IP所需要的,如果只希望调用IP的话,则只需要调用IP即可,目前时间紧急,我先学一学如何使用IP,解决卡脖子的问题,自研日后再说。

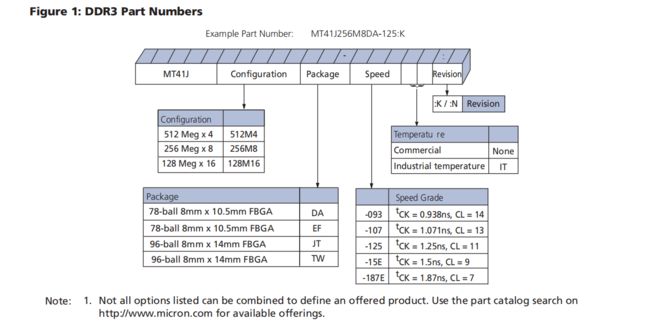

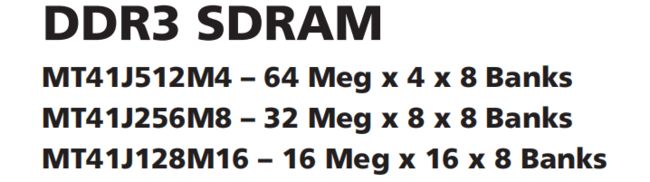

使用的DDR3器件:MT41J128M16JT-093K

总览

DDR3 IP配置

第一部分

选择此选项可生成内存控制器。生成内存控制器将创建 RTL、XDC、implementation 和simulation 文件。

Verify Pin Changes and Update Design

选择此功能可验证已通过 MIG 生成的设计的修改后的 XDC。此选项允许您更改引脚分配并立即验证它,它会更新输入 XDC 文件以与当前版本的 MG 兼容。更新 XDC 时,它会保留输入 XDC 的引脚分配。此选项还将使用您在此页面中选择的组件名称生成新设计。

多控制器

通过 DDR3 SDRAM、QDR1+-SRAM 或 RLDRAM 的组合,最多可生成 8 个控制器。可容纳的控制器数量可能受到数据宽度和器件中可用存储体数量的限制。有关详细信息,请参阅用户指南 控制器数量 。

不使能则为APP接口:

Xilinx DDR3 —— MIG IP核的原理(APP接口)_XPii的博客-CSDN博客

第二部分 选择可拓展器件

3

第三部分 选择内存接口类型。

请参阅用户指南,了解每个 FPGA 系列支持的控制器的详细列表。下面的列表显示了特定 FPGA、速度等级和所选设计条目的当前可用接口。

4.

DDR的时钟速率

时序标准

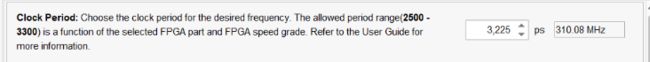

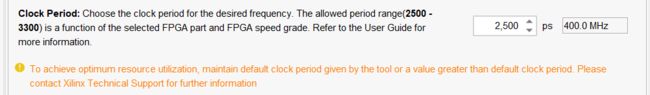

时钟周期:选择所需频率的时钟周期。允许的周期范围(2500 -3300)是所选 FPGA 部件和 FPGA 速度等级的函数。请参阅用户指南了解更多信息。

所以此处配置的实际上是时钟频率。

Clock Period

①Clock Period设置的参数就是 MIG 的PHY 接口对DDR3的时钟,也就是DDR3芯片实际跑的IO时钟频率,它由system clock(主时钟)倍频而来,最大频率不能超过DDR3 和MIG支持的最大频率中的最小值。

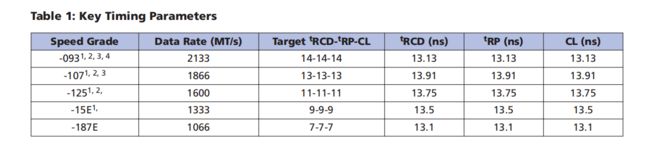

器件名称:MT41J128M16JT-125:K

tCK = 1.25ns,就可以算出芯片支持的最大IO时钟频率:1/1.25ns = 800Mhz;此处的IO时钟频率也就是DDR3的频率。

双边沿都发送,所以数据传输速率:1600M。

但是A7只支持800MHZ的PHY(数据传输速率)速率,所以工作时钟频率只能设置为400MHZ,但是K7可以支持1600MHZ的PHY所以可以设置为1250PS = 1.25NS。

PHY 与控制器时钟比率:(低于 350M 才可选)

选择 PHY 与内存控制器时钟比率。 PHY 以上面选择的内存时钟周期运行。控制器以 PHY 速率的 1/4 或 1/2 运行。所选的内存时钟周期将限制选择。

PHY to Controller Clock Ratio:DDR3 物理芯片运行时钟和 MIG IP 核的用户端(FPGA)的时钟之比, 一般有 4:1 和 2:1 两个选项,本次实验选 4:1。由于 DDR 芯片的运行时钟是 400Mhz,因此 MIG IP 核的用户时钟(ui_clk)就是 100Mhz。一般来说高速传输的场合选择 4:1,要求低延时的场合选择 2:1。这里还要指 出,当 DDR3 时钟选择选择了 350M 到最高的 400M,比例默认只为 4:1,低于 350M 才有 4:1 和 2:1 两个选 项。

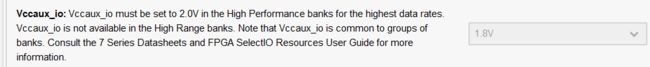

Vccaux_io

在高性能组中,Vccaux_io 必须设置为 2.0V,以获得最高数据速率。Vccaux_io 在高范围组中不可用。请注意,Vccaux_io 对于Bank组来说是通用的。有关更多信息,请参阅 7 系列数据表和 FPGA SelectIlO 资源用户指南。

这是 FPGA 高性能 bank(High Performance bank)的供电电压。它的设置取决于 MIG 控制器运行的周期/频率。当用户让控制器工作在最快频率的时候,系统会默认为 1.8V,当然在 1.8V 下用 户可以运行低一点的频率。本实验默认 1.8V。

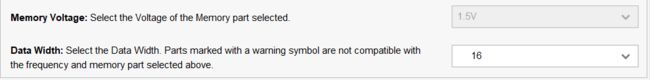

内存类型:

选择内存类型。标有警告符号的类型与上述频率选择不兼容。

内存部分:

选择内存部分。标有警告符号的部分与上述频率选择不兼容。如果此处未列出所需的部件,请查找等效部件或使用“创建自定义部件”按钮创建部件。RLDRAM II 不支持“创建自定义部件”功能。

根据实际需求选择。

数据位宽

同样根据实际需求选择。

实在找不到自己翻手册配。

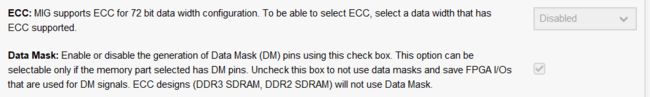

ECC:ECC 校验使能

MIG 支持 72 位数据宽度配置的 ECC。为了能够选择 ECC,请选择支持 ECC 的数据宽度。

数据位宽为 72 位的时候才能使用。

Data Mask:数据掩码

使用此复选框启用或禁用数据掩码 (DM) 引脚的生成。仅当所选存储器部分具有 DM 引脚时才可选择此选项。取消选中此框可不使用数据掩码并保存用于 DM 信号的 FPGAIO。 ECC 设计(DDR3 SDRAM、DDR2 SDRAM)不会使用数据掩码。

数据屏蔽管脚使能。勾选它才会产生屏蔽信号。

Number of Bank Machines:

Bank Machine 的数量是用来对具体的每个或某几个来单独控制的,选择多 了控制效率就会高,相应的占用的资源也多,本实验选择 4 个,平均一个 Bank Machine 控制两个 BANK

(本次实验的 DDR3 芯片是八个 bank)。

ORDERING:

该信号用来决定 MIG 控制器是否可以对它收到的指令进行重新排序,选择 Normal 则允 许,Strict 则禁止。本实验选择 Normal,从而获得更高效率。

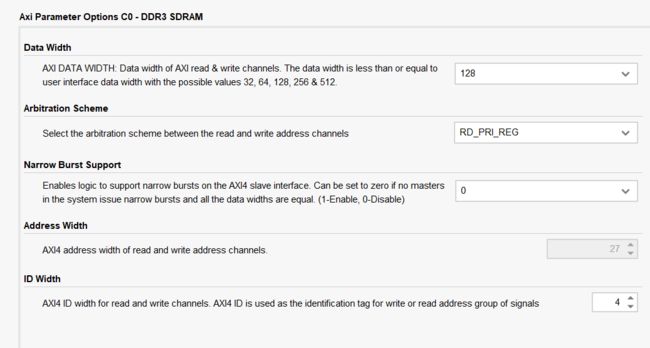

第四部分 Axi 参数配置

数据宽度

AXI DATA WIDTH:AXl 读写通道的数据宽度。

数据宽度小于或等于用户接口数据宽度,可能值为 32,64,128,256&512。

仲裁方案

选择读写地址通道之间的仲裁方案

窄突发支持

使逻辑能够支持 AXl4 从接口上的窄突发。如果系统中没有主机发出窄突发并且所有数据宽度都相等,则可以设置为零。 (1-启用,0-禁用)

地址宽度

AXI4 读写地址通道的地址宽度。

ID 宽度

AXI4 读写通道的 ID 宽度。 AX4 ID用作写入或读取信号组地址的识别标签

第五部分 存储器配置

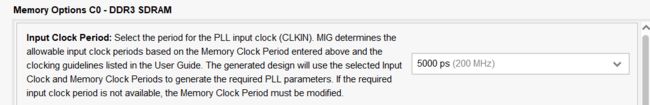

输入时钟周期:(重要)

选择 PLL 输入时钟 (CLKIN) 的周期。MIG 根据上面输入的内存时钟周期和用户指南中列出的时钟指南确定允许的输入时钟周期。生成的设计将使用选定的输入时钟和内存时钟周期来生成所需的 PLL 参数。如果所需的输入时钟周期不可用,则必须修改内存时钟周期。

MIG内部有PLL用来完成从输入时钟频率到DDR3工作频率的倍频。

推荐选择200Mhz,因为参考时钟也是200Mhz,配置的时候参考时钟可以直接使用系统时钟,减少端口信号。

Read Burst Type and Length:

突发类型决定突发内的数据排序。有关详细信息,请参阅内存数据表。突发长度 8 是唯一受支持的值。(基本没人用交叉,到底是谁在用呢)

突发类型选择,突发类型有顺序突发和交叉突发两种,本实验选择

顺序突发(Sequential),其突发长度固定为 8。

Output Driver Impdance Control:

输出阻抗控制。本实验选择 RZQ/7。

RTT(标称) - 片上端接 (ODT)~终结电阻,可进行动态控制。

选择组件或 DIMM 接口上 DQ、DQS/DQS# 和 DM 信号的 ODT 标称值。对于数据速率,必须将其设置为 RZQ/6 i(40 欧姆) 1333 Mbps 及以上。在 2 插槽 DIMM 配置中,该值将用于写入期间未写入的插槽,也将用于读取期间未选择的插槽。使用板级仿真来选择最佳值。

Controller Chip Select Pin:

片选管脚引出使能。本实验选择 enable,

当此选择设置为“禁用”时,片选 (CS#) 引脚可在外部连接为低电平,以在地址/命令组中保存一个引脚。禁用仅对单列配置有效。

实际上DDR3或者说SDRAM的所有指令,包括NOP下,CS_N都设置为0,这里默认为0可以省略一个管脚。

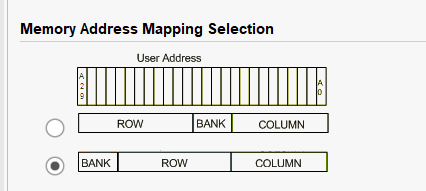

寻址方式选择

BANK_ROW_COLUMN:

寻址方式选择。本实验选择第二种,即 BANK-ROW-COLUMN 的形式,这是一种最常规的 DDR3 寻址方式,即要指定某个地址,先指定 bank,再指定行,最后指定列,这样就确定 了一个具体地址。

一般来说这样寻址方式有利于降低功耗,但是读写性能(效率)上不如 “ROW_BANK_COLUMN”。

第六部分 FPGA配置

System Clock类型:

MIG IP核输入给内部PLL的时钟类型,就是上一部分这个。/

可选择“No Buffer”,直接选单端时钟是默认有buffer?

因为IP核的输入系统时钟是单端时钟, 是由内部的MMCM产生的,MMCM所产生的时钟默认添加了buffer。

Reference Clock参考时钟类型:

MIG IP 核参考时钟。同样可选择“No Buffer”,将由时钟模块生成,IP 核参考时钟要求是 200Mhz。如果之前在:

使用了 200Mhz 的系统时钟,则参考时钟就可以直接使用系统时钟(use system clock)

System Reset Polarity:

复位有效电平选择。

Sample Data Depth:采样深度选择。

此功能允许在 ChipScope 工具上监视 IP 中存在的各种调试信号。

调试信号包括各个 PHY 校准阶段的状态信号。启用此功能会将所有调试信号连接到 exampledesign 顶部模块中的 ChipScope ILA 和 VIO 内核。

调试接口中每条总线都有部分接地,用户可以将接地信号替换为所需的信号。

当“Debug Signals Control”选择“OFF”时,所有采样深度是不可选的。

Internal Vref:

内部参考管脚,表示将某些参考管脚当成普通的输入管脚来用。

由于开发板的 IO 资源 较为紧张,这里需要选择“ON”,把参考管脚当做普通的输入管脚来用。

内部 Vref 可用于允许将 Vref 引脚用作普通 IO 引脚。该选项只能在 800 Mbps 和更低的数据速率下使用。这可以为每个使用输入的组释放 2 个引脚。此设置对仅具有输出的组没有影响。

IO Power Reduction:管脚节能

IO 管脚节省功耗设置。选择“ON”,即开启。

通过在写入期间和不活动期间自动禁用 DQ/DQS IBUF 和内部终止,显着降低平均 IO 功率

XADC Instantiation:温度补偿

XADC 模块例化。使用 MIG IP 核运行的时候需要进行温度补偿,可以直接选择 XADC 模块的温度数据引到 MIG IP 核来使用,否则需要额外提供温度数据,选择“Enable”。

存储器接口使用 XADC 块的温度读数来执行温度补偿,并使读数在数据窗口中保持居中。每个设备有一个 XADC 块,如果 XADC 当前未在设计中的任何地方使用,请启用此选项以拥有该块实例化。

如果已使用 XADC,请禁用此 MIG 选项。

然后,用户需要向顶级 12 位 device_temp_i 输入端口提供温度值。有关详细信息,请参阅答复记录 51687 或 UG586。

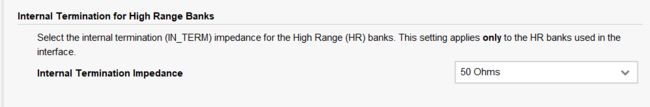

第七部分 内部高性能 bank 端接匹配阻抗

选择高范围 (HR) 组的内部终端 (N_TERM) 阻抗。

此设置仅适用于界面中使用的 HR BANK。内部终端阻抗 50 Ohms

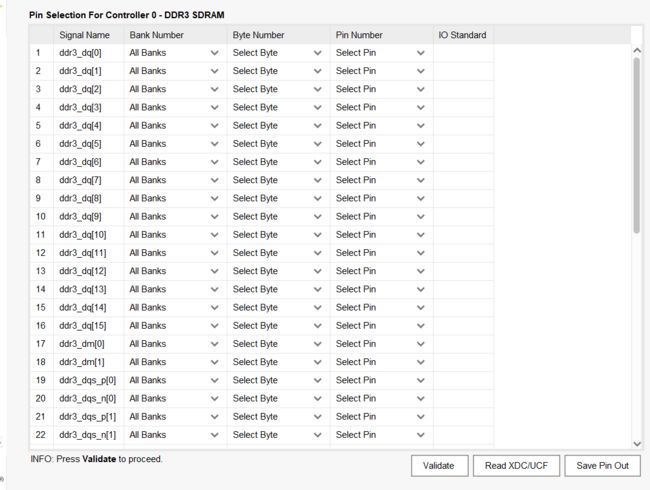

第八部分 管脚模式选择

如果选择第二种则可以直接导入。

第九部分 BANK选择

第八部分选择了第一种的情况下:

在下面的架构视图中选择数据和地址控制的字节组。

数据和地址控制必须在 3 个垂直组内选择。接口不能水平跨越。

“Bank/s) 14,15 包含配置引脚。MlG 尝试避免使用这些 Bank 进行默认配置。如果为内存控制器选择了 Bank(s) 14,15,则应验证 XDC 以确保与配置引脚不发生冲突。

有关完整信息,请参阅 UG586 Bank 和 Pin 规则。

Bank 选择可能仅限于高性能列,以满足所选的接口数据速率

第二种:

导入后则直接跳到倒数第二步。