10.25verilog复习,代码规范复盘,触发器复习

verliog复习

1.模块的输入输出(reg与wire)

输入是线性,wire,

输出较复杂需要之前的状态,不仅仅是由当下输入来的信号的与或非组合而成的,需要保存之前状态的,输出类型是reg。

比如计数器,需要在之前计数的基础上再加1,所以是reg型,但输入是wire

wire就是起到一个信号传递的作用,它不保存信号

而reg会在一定条件下保存信号

即就是用wire去接收信号,处理信号,转化信号用reg(时序逻辑,与之前状态有关,需要存储)

一些简单的信号合并(通过与非门就可以实现的组合逻辑)可以直接用wire,实际上组合逻辑也是模块,只不过很简单,信号进去后就直接出来,没有存储

2.assign与always

reg型就用always,wire就用assign

reg就用<=,wire就用=

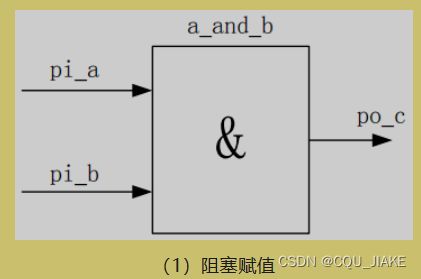

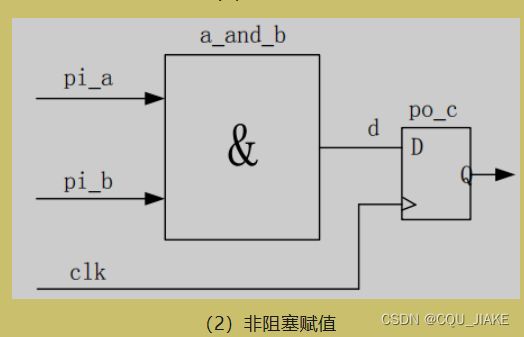

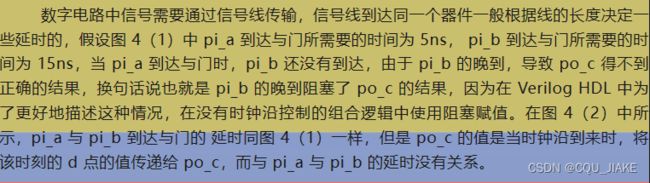

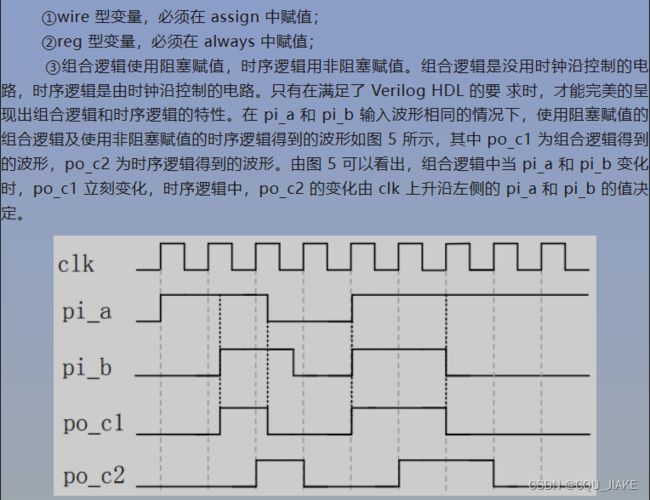

3.阻塞与非阻塞赋值

时序逻辑中使用非阻塞赋值,组合逻辑中使用阻塞赋值

关于位宽

一个信号的位宽有两种理解

位宽与信号为wire或reg无关,wire与reg只是反映怎么处理信号,与信号本身无关

信号本身特点之一为位宽,wire可以有位宽,reg也可以有位宽,与是否是wire或reg无关

1.每位有实际意义,大小无意义

一个是这个信号代表的是一组信号,每一位都代表一个具体开关(或类似的)的01取值

比如用一组16位宽的信号输出去描述16个led灯的亮灭,就是只用了一个信号,其位宽为16

其在管脚文件下,每个位下的信号都有其实际意义,比如开关、亮灭

2.大小有实际意义,每位无意义

第二就是说是描述的是一个信号,就是这一个多位宽信号只有一个实际意义,其每位单拎出来没有任何意义,纯粹是因为这个要记录的数太大,01表示不了,所以用多位宽、借助多位去记录这一个比较大的数

其在管脚文件下每位无实际意义,但可通过Led去反映每位的一个实际情况

十进制举例理解

对第一种情况而言就比如身份证,并不是用来计数的,而是由好多十进制数组合在一起,组成一个数,这个数就是身份证号,其实际大小并无意义,有意义的是其中的每位及位之间的组合,再比如生日之类的,以及状态压缩之类的,就是用一个数,通过这个数的每一位,及位之间的组合去记录、反映一些事情

对第二种就是十进制运算,加减法,实际大小有意义,但每一位并无意义

代码规范与复盘、理解

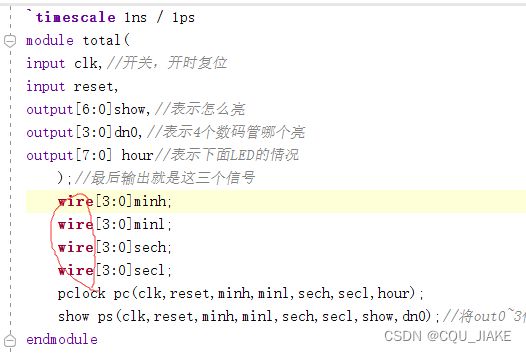

1.模块间信号调用

板块之间的信号调用,用wire去传递

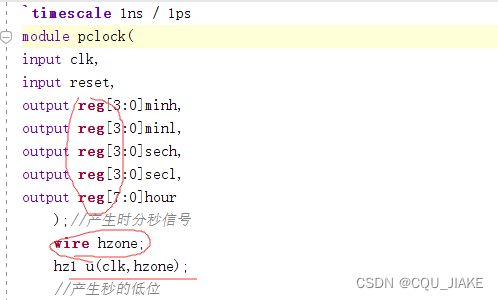

2.输出的reg信号

hzone作为线去传递信号

寄存器只是在板块内进行处理时所用的元件,板块出来后都是wire,都是线

板块进出都是wire,都是线,只不过reg在板块内发挥为寄存器,要借助寄存器,但是输出时,出了板块,处理完后,就是wire型

即pcclok输出信号的几个reg,其reg声明只是在板块内起作用,表示这个板块内部是时序逻辑,需要用到之前的状态,信号的赋值要用always与<=,但其输出后都是wire,

即就是用wire去接收信号,处理信号,转化信号用reg(时序逻辑,与之前状态有关,需要存储)

一些简单的信号合并(通过与非门就可以实现的组合逻辑)可以直接用wire,实际上组合逻辑也是模块,只不过很简单,信号进去后就直接出来,没有存储

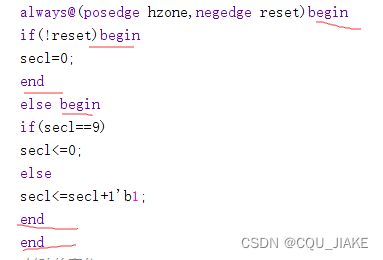

3.if里的begin,end

verliog始终要记得begin与end,写了begin就先写end再写里面内容

4.reg型一律用<=

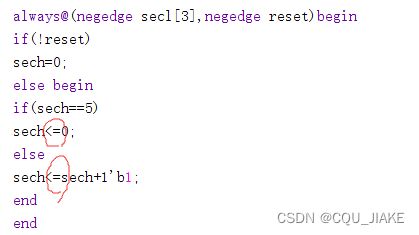

5.多位宽信号的触发沿

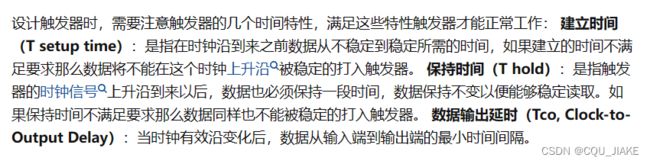

触发器

module DFF(

input D,

input CLK, //输入信号

output Q //输出信号

);

always@(posedge clk) // 时序逻辑

begin

Q <= D; //非阻塞赋值

end

endmodule