时序约束实战(vivado中时序分析软件的使用)

FPGA时序分析_居安士的博客-CSDN博客_fpga时序分析

FPGA时序约束_居安士的博客-CSDN博客

之前的两篇总结了一些时序分析和约束的概念,如何根据这些概念,在vivado里进行时序约束,下面对步骤进行总结:

目录

(1)创建约束文件

(2)管脚约束

(3)主时钟约束

(4)output_delay约束

(5)查看时序报告

(1)创建约束文件

在创建文件时选择约束文件constraint,之后creat,然后重命名,finish

(2)管脚约束

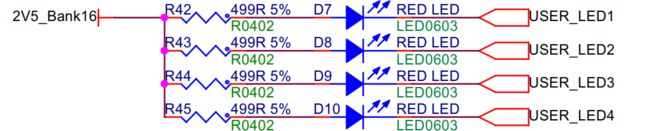

这里直接用led流水灯例子来说明

constraints里面会出现约束文件.xdc文件,接下来根据FPGA原理图在约束文件里面把管脚和电平标明。

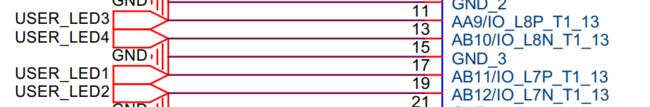

可见LED1对应AB11,LED2对应AB12,LED3对应AA9,LED4对应AB10

set_property PACKAGE_PIN Y18 [get_ports clk_50m]

set_property IOSTANDARD LVCMOS33 [get_ports clk_50m]

set_property PACKAGE_PIN AB11 [get_ports {led_out[0]}]

set_property PACKAGE_PIN AB12 [get_ports {led_out[1]}]

set_property PACKAGE_PIN AA9 [get_ports {led_out[2]}]

set_property PACKAGE_PIN AB10 [get_ports {led_out[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_out[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_out[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_out[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_out[3]}]前两行是时钟约束,信号名称需要和代码对应起来

后面是管脚约束,将led信号放在芯片的引脚:set_property PACKAGE_PIN xxx [get_ports xxx]

将led所在引脚的电气标准设置为LVCMOS33:set_property IOSTANDARD LVCMOS33 [get_ports xxx]

(3)主时钟约束

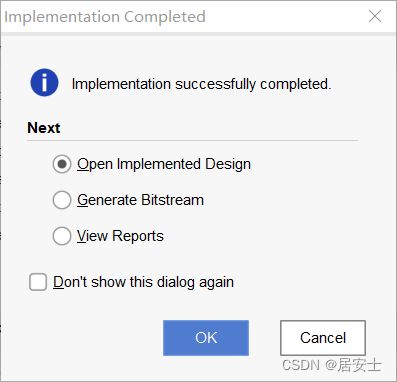

首先进行综合实现(run implementation),在弹出的对话框选择 open implemented Design

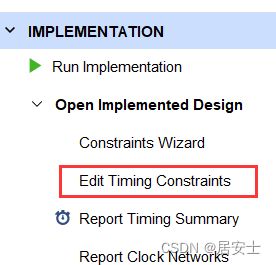

再点击右侧implementation栏下面的 open——Edit,右上角弹出一个新的界面

点击 creat clock,再点击“+”,在弹出来的框里面写名字

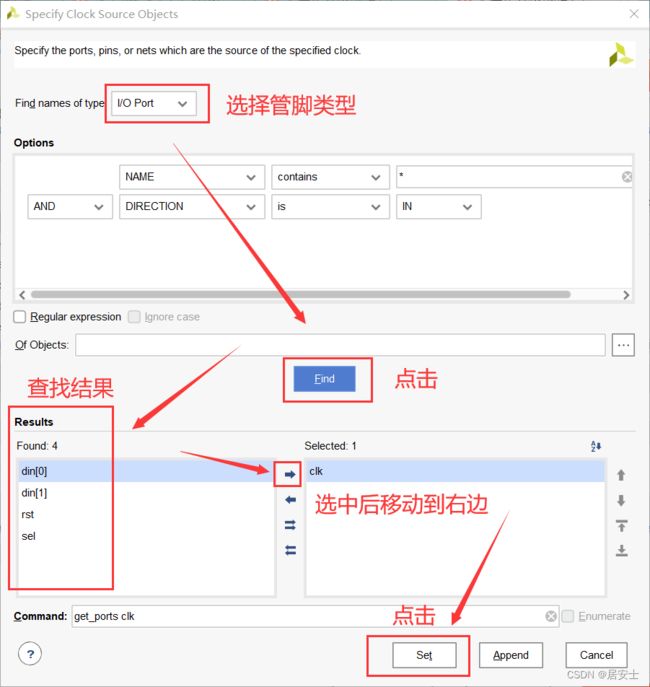

clock name和source objects可以写同一个,点击 source objects右边的“...” 会出现下面界面,按照步骤操作:

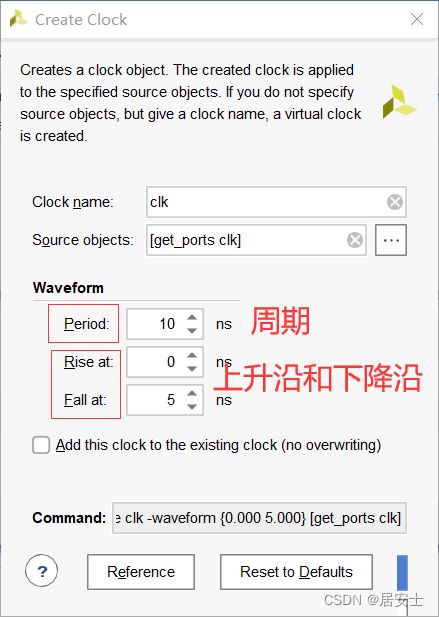

然后可以设置周期和上升沿下降沿,设置完成点击“ok” ,之后会发现成功创建了一条约束,但是显示unsaveed,

之后我们在整个vivado 的大界面,Ctrl+s 进行保存

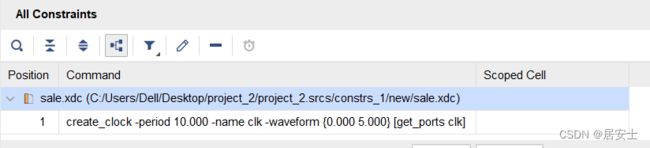

这个时候我们可以看到,一条时钟约束被成功添加,周期10ns,占空比50%,上升沿0,下降沿5

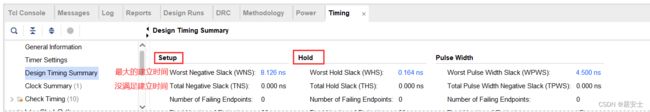

然后重新进行布局布线和实现,就可以查看时序报告了,如果有时序违例会标红

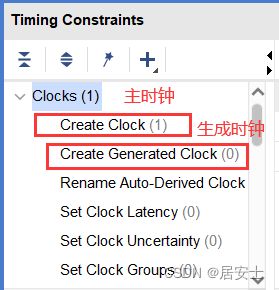

其他的约束同理:

生成时钟约束

(4)output_delay约束

首先选择set_output_delay,点击“+”,根据数据手册修改时间

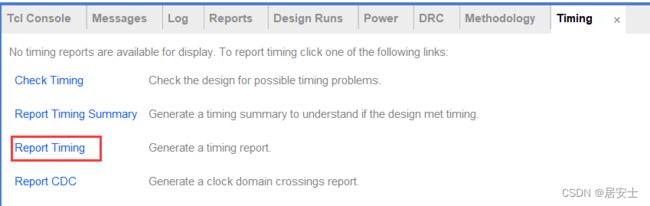

(5)查看时序报告

在timing栏点击最下面的小字,鼠标右键,出现close

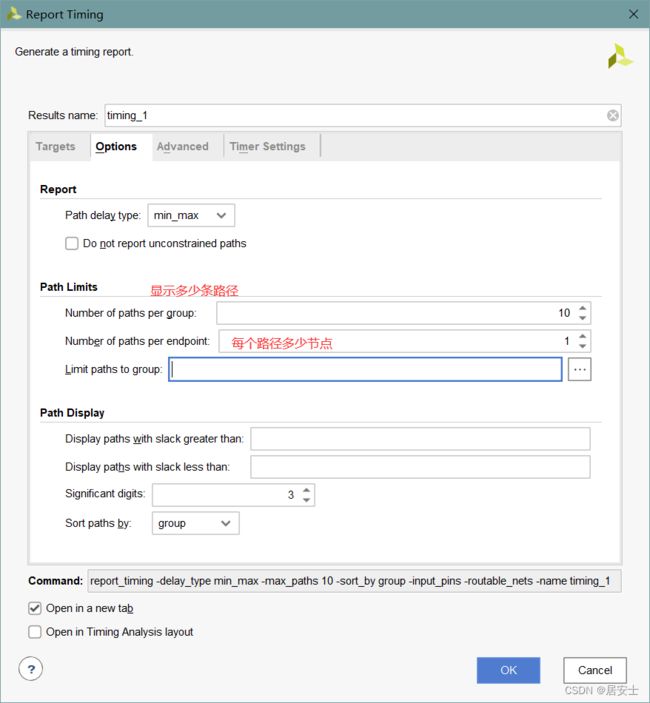

点击report timing,可以打印时序报告

targets里可以设置具体的时序路径 ,option里面可以设置路径个数和节点个数,设置好了之后点击“OK”

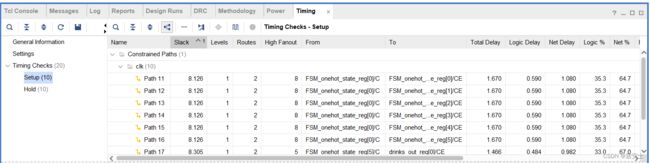

生成时序报告如下:

如果想要看某一条路径的细节,可以双击某条路径,右上方会自动弹出

里面会有源时钟路径,数据路径,目的时钟路径,可以看到每一部分的时间,以及slack时间

由于我目前还是初学,没有遇到过出现时序违例的情况,这篇只是介绍一下vivado里面时序分析的步骤,后面随着学习的深入,这篇会及时补充