Verilog语言要素(三)

1 Verilog语言要素

1.3 常量(Constant Numbers)

规范原文如下:

- Constant numbers can be specified as integer constants or real constants.

实际上Verilog有3种类型的常量:

integer(整型)

real(实型)

string(字符串型)

1.3.1 数量(Numbers)

1.3.2 整形常量(Integer Constants)

规范原文如下:

- Integer constants can be specified in decimal, hexadecimal, octal, or binary format. There are two forms to express integer constants. – 有基和无基

- The number of bits that make up an unsized number (which is a simple decimal number or a base-format number without the size specification) shall be at least 32.

1.3.2.1 简单十进制格式

规范原文如下:

- The first form is a simple decimal number, which shall be specified as a sequence of digits 0 through 9, optionally starting with a plus or minus unary operator.

- Simple decimal numbers without the size and the base format shall be treated as signed integers.

规范举例如下:

- 659 // is a decimal number

- -5 // is a decimal number preceded by a minus operator

- 27_195_000 // underscore are ignored

1.3.2.2 标准化基数格式

规范原文如下:

- The second form specifies a based constant, which shall be composed of up to three tokens—an optional size constant, an apostrophe character (') followed by a base format character, and the digits representing the value of the number. - 第2种格式:有基常数

- The first token, a size constant, shall specify the size of the constant in terms of its exact number of bits. It shall be specified as a nonzero unsigned decimal number. – 简单理解就是正整数;size在工程实现中存在的必要性(如乘法器资源)

- The second token, a base_format, shall consist of a case-insensitive letter specifying the base for the number, optionally preceded by the single character s (or S) to indicate a signed quantity, preceded by the apostrophe character. The apostrophe character and the base format character shall not be separated by any white space. - 撇号和基是一体无间隔的

- The third token, an unsigned number, shall consist of digits that are legal for the specified base format. The unsigned number token shall immediately follow the base format, optionally preceded by white space. - base format和unsigned number之间可以有空格

– an unsigned number有些难理解,以4’sb1001为例:

s表示1001是有符号数,最高位是符号位,1表示1001是负数,且1001是以2的补码形式表示的负数

4’sb1001可以写成4’sd9,从2进制1001到10进制9的转换体现了1001是unsigned number

4’sd9的表述看着有点别扭,原因是4位有符号数的表示范围为十进制的-8~7

总结:the third token是用不同进制表示的unsigned number,而the second token中的s|S指示如何解释the third token - It shall be legal to macro-substitute these three tokens. – 3个组成部分都可以进行宏替换

- The numbers specified with the base format shall be treated as signed integers if the s designator is included or as unsigned integers if the base format only is used. The s designator does not affect the bit pattern specified, only its interpretation. - 有s=有符号数,无s=无符号数;s/S只影响对unsigned number的解释

- A plus or minus operator preceding the size constant is a unary plus or minus operator. A plus or minus operator between the base format and the number is an illegal syntax. - ±符号不能出现在second token和third token之间

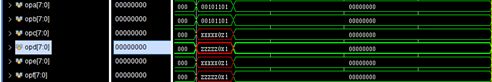

- An x represents the unknown value in hexadecimal, octal, and binary constants. An x shall set 4 bits to unknown in the hexadecimal base, 3 bits in the octal base, and 1 bit in the binary base. - 1个x分别表示4-bit、3-bit和1-bit的值是x

- A z represents the high-impedance value in hexadecimal, octal, and binary constants. An z shall set 4 bits to unknown in the hexadecimal base, 3 bits in the octal base, and 1 bit in the binary base.

- The use of x and z in defining the value of a number is case insensitive. – x、z不区分大小写

- If the size of the unsigned number is smaller than the size specified for the constant, the unsigned number shall be padded to the left with zeros. If the leftmost bit in the unsigned number is an x or a z, then an x or a z shall be used to pad to the left, respectively. – 参见1.3.2.2.2.1小节实例

- If the size of the unsigned number is larger than the size specified for the constant, the unsigned number shall be truncated from the left. – 右对齐左截断

- In a decimal constant, the unsigned number token shall not contain any x or z digits, unless there is exactly one digit in the token, indicating that every bit in the decimal constant is x or z. - 10‘dx或10’dz

- The number of bits that make up an unsized number (which is a simple decimal number or a number without the size specification) shall be at least 32. – 未指定size时size≥32

- The underscore character (_) shall be legal anywhere in a number except as the first character. The underscore character is ignored. - 下划线用于分割大位宽数据

1.3.2.2.1 格式

格式定义如下:

[size]`[signed] base unsigned_number

格式说明如下:

- size:非零十进制整数值,是可选的;

- signed:s或S不区分大小写,是可选的,带signed作为有符号数解释,不带signed作为无符号数解释;

- base:二进制(b或B)、八进制(o或O)、十进制(d或D)和十六进制(h或H),不区分大小写。

规范举例如下:

Example 1 – Unsized constant numbers - 659 // is a decimal number

- 'h837FF // is a hexadecimal number

- 'o7640 // is an octal number

- 4af // is illegal (hexadecimal format requires 'h)

Example 2 – Sized constant numbers - 4’b1001 // is a 4-bit binary number

- 5’D3 // is a 5-bit decimal number

- 3’b01x // is a 3-bit binary number with LSB unknown

- 12’hx // is a 12-bit unknown number

- 16’hz // is a 16-bit impedance number

Example 3 – Using sign with constant numbers - 8’d-6 // this is illegal syntax

- -8’d6 // this defines the two’s complement of 6 held in 8 bits equivalent to -(8’d6)

- 4’shf // this denotes the 4-bit number ‘1111’ to be interpreted as a 2’s complement number or ‘-1’

- -4’sd15 // this is equivalent to -(-4’d1) or ‘0001’

- 16’sd? // the same as 16’sbz

Example 4 – Using underscore character in numbers - 27_195_000

- 16’h0011_0101_0001_1111

- 32’h12ab_f001

1.3.2.2.2 位宽

1.3.2.2.2.1 size和constant不等

- 若constant的最高位为x或z时,用x或z补齐size大小的位宽

- 若constant的最高位不为x或z时,无论有无符号,用0补齐size大小的位宽

- 参见规范原文部分第11条

个人建议如下: - size要和constant的位宽相等,以免引起不必要的补位操作。

1.3.2.2.2.2 赋值表达式两侧位宽不等

- 首先是位宽扩展:如果是无符号数,高位补齐0;如果是有符号数,高位补齐符号位;

- 然后是求补操作:如果前边有“-”单目运算符,则对补齐位宽后的数求补;如果前边没有“-”单目运算符,则对补齐位宽后的数不做任何操作;

- 最后求补方法是:对操作数的所有位(包括符号位)取反然后加1;

- 原则是:无论“数”是有符号还是无符号、是源码还是补码,减去一个数等于对这个数求补。

1.3.3 实型常量(Real Constants)

- Real numbers can be specified in either decimal notation or in scientific notation.

- Real numbers expressed with a decimal point shall have at least one digit on each side of the decimal point. – 小数点两边必须都有数

1.3.3.1 简单十进制格式

规范举例如下:

1.2

0.1

2394.26331

以下写法非法:

. 12 // 小数点两边必须都有数

9. // 小数点两边必须都有数

1.3.3.2 科学计数法格式

举例如下:

1.2E12 // the exponent symbol can be e or E

1.30e-2

0.1e-0 // 可以是-0?

23E10 // 可以没有小数点

29E-2 // 可以没有小数点

236.123_763_e-12 // underscores are ignored

以下写法非法:

4.E3

.2e-7 // 小数点两边必须都有数

注:Verilog语法挺奇怪的,用科学计数法表示的数即使不带小数点也算作小数

1.3.3.3 实数转换为整数

规范原文如下:

- Real numbers shall be converted to integers by rounding the real number to the nearest integer, rather than by truncating it.

- Implicit conversion shall take place when a real number is assigned to an integer.

- The ties shall be rounded away from zero. - ties是什么意思?中间值?

规范举例如下:

- The real numbers 35.7 and 35.5 both become 36 when converted to an integer and 35.2 becomes 35.

- Converting –1.5 to integer yields –2, converting 1.5 to integer yields 2.

规范总结如下:

- 35.5位于35和36的正中间,-1.5位于-1和-2的正中间,为什么35.5向36舍入,-1.5向-2舍入?是不是说35.5和-1.5输入规范原文第3条的ties,应该向远离0点的一侧舍入?

1.3.4 字符串常量(Strings)

规范原文如下:

- A string is a sequence of characters enclosed by double quotes (“”) and contained on a single line. – 字符串不能跨行

- Strings used as operands in expressions and assignments shall be treated as unsigned integer constants represented by a sequence of 8-bit ASCII values, with one 8-bit ASCII value representing one character. – 无符号整形常量

- Strings can be manipulated using the Verilog HDL operators. – 字符串本身也是操作数,只是这种操作数以ASCII码字符的形式表示

规范总结如下:

- 字符串是双引号内的字符序列,不能分成多行书写,不能使用单引号(只有一个字符也不行);

- 用8位ASCII值表示的字符可以看作是无符号整形常量。

1.3.4.1 用于状态机仿真

1.3.4.2 用于变量赋值

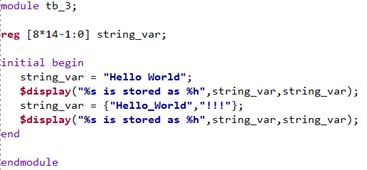

规范原文如下:

- When a variable is larger than required to hold a string value being assigned, the value is right-justified, and the leftmost bits are padded with zeros, as is done with nonstring values. – 变量位宽比字符串大,字符串右对齐左补0

- If a string is larger than the destination string variable, the string is right-justified, and the leftmost characters are truncated. – 字符串位宽比变量大,字符串右对齐左截断

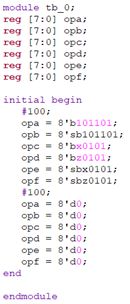

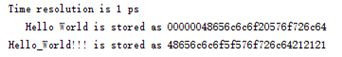

- 因为变量string_var最大可以表示14个字符,而“Hello World”只有11个字符,所以在打印显示时前3个字符是空白;

- 字符串中的空格和下划线也算一个字符。

实例问题如下:

- ASCII码0x00对应的字符是NUL,显示出来和ASCII码0x20对应的字符SP一样,为什么?