AD9371 官方例程HDL JESD204B相关IP端口信号

AD9371 系列快速入口

AD9371+ZCU102 移植到 ZCU106 : AD9371 官方例程构建及单音信号收发

ad9371_tx_jesd -->util_ad9371_xcvr接口映射: AD9371 官方例程之 tx_jesd 与 xcvr接口映射

AD9371 官方例程 时钟间的关系与生成 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成(一)

AD9371 官方例程 时钟间的关系与生成 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成 (二)

采样率和各个时钟之间的关系 : AD9371 官方例程HDL详解之JESD204B TX侧时钟生成 (三)

文章目录

- 一、TX

-

- 传输层

- 链路层

- 物理层配置IP

- 二、RX

-

- 传输层

- 链路层

- 物理层配置IP

- 三、物理层IP

一、TX

传输层

s_axi、s_axi_aclk、s_axi_aresetn :AXI lite 配置接口,时钟,复位

dac_dunf:数据下溢标志,无有效数据

dac_data_0 1 2 3:应用层提供的数据,[ M3S1, M3S0, M2S1, M2S0, M1S1, M1S0, M0S1, M0S0]

link:提供给链路层的组帧好的数据

dac_enable 和 dac_valid:官方例程提供给其应用层的信号,后续根据自己基带逻辑选择性使用

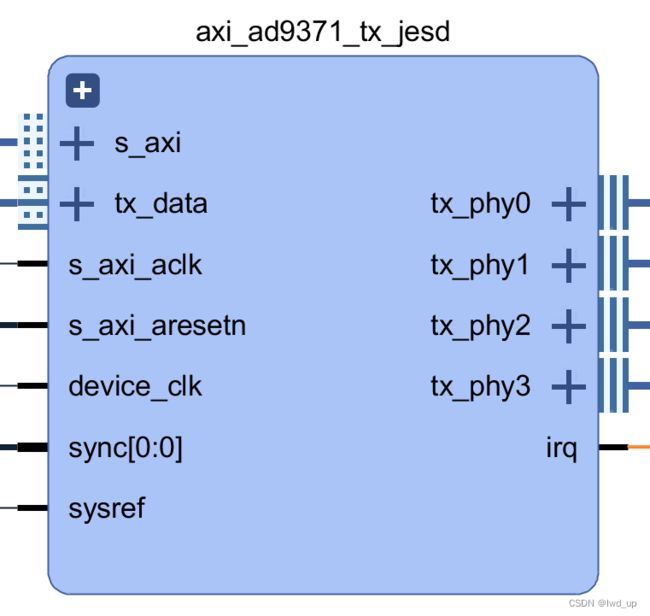

链路层

s_axi、s_axi_aclk、s_axi_aresetn :同上

tx_data:传输层提供给链路层的数据

device_clk:IP工作的主要逻辑时钟

sync:AD9371的 JESD204B rx 模块提供的 sync 协议信号

sysref:AD9528提供给AD9371和FPGA的 LMFC同步信号

tx_phy0 1 2 3:链路层给物理层各个lane的数据

irq:tx_axi 产生的中断信号

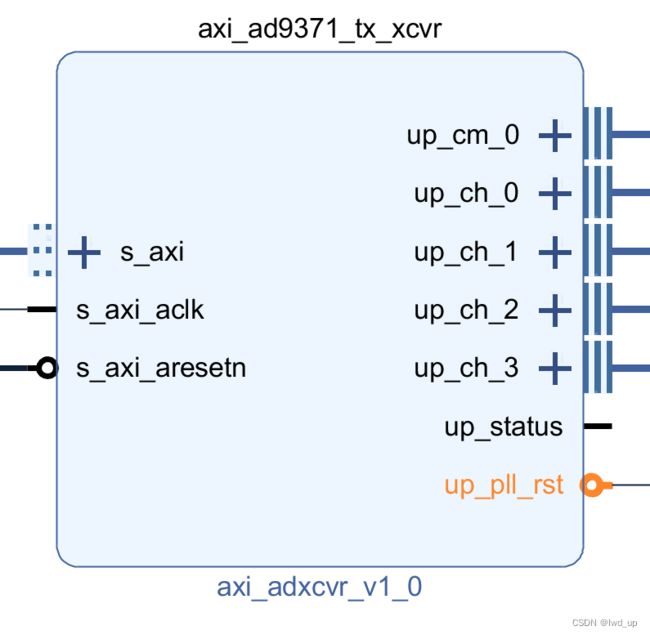

物理层配置IP

up_ch_0 1 2 3 : 物理层 每个 TX Channel DRP端口

up_pll_rst: QPLL复位

二、RX

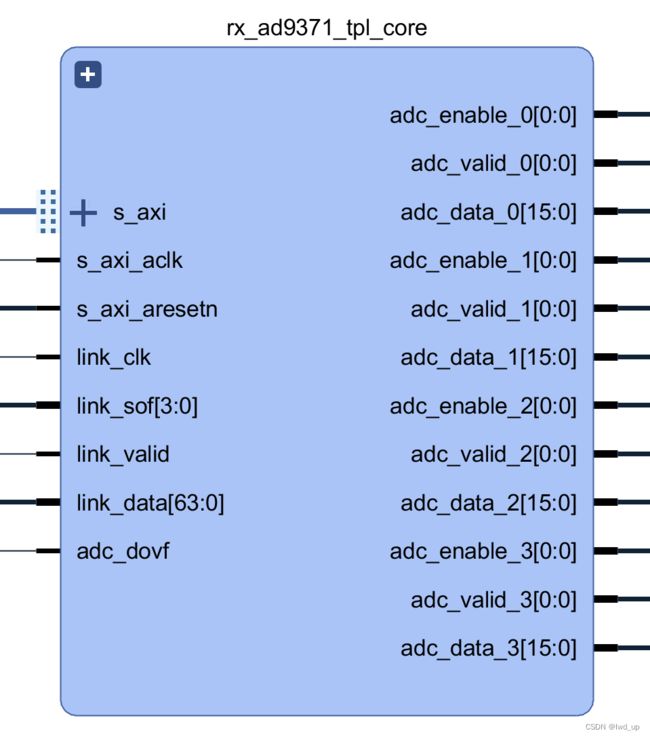

传输层

link_clk:IP主要工作时钟,同链路层时钟

link_sof:链路层传递的数据帧起始标志(未验证)

link_valid、link_data:链路层传递的有效标志和数据

s_axi、s_axi_aclk、s_axi_aresetn :同上

adc_dovf:应用层数据上溢标志,有效数据写满了

adc_data_0 1 2 3:提供给应用层的数据,[ M3S0, M2S0, M1S0, M0S0]

adc_enable 和 adc_valid:官方例程提供给其应用层的信号,后续根据自己基带逻辑选择性使用

链路层

s_axi、s_axi_aclk、s_axi_aresetn :同上

rx_phy0 1 :物理层给链路层各个lane的数据

sysref:AD9528提供给AD9371和FPGA的 LMFC同步信号

device_clk:IP工作的主要逻辑时钟

irq:rx_axi 产生的中断信号

sync: rx 模块提供给AD9371 JESD204B的 sync 协议信号

phy_en_char_align:CGS阶段,提供给物理层的字符对齐使能信号

rx_sof:rx帧起始标志

rx_data_tvalid、rx_data_tdata:链路层提供给传输层的有效标志和数据

物理层配置IP

m_axi:Eye-Scan DMA 接口,连接到 S_AXI_HP3

up_cm_0:物理层 COMMON DRP端口

up_ch_0 1 : 物理层 每个 RX Channel DRP端口

up_es_0 1 : 物理层 每个Channel Eye-Scan DRP端口

up_pll_rst: CPLL复位

三、物理层IP

up_cm、up_es、up_rx、up_tx :见 TX 和 RX 物理层配置IP

tx_0 1 2 3 :tx 链路层提供给物理层的发送数据

up_rstn、up_clk:DRP 复位和时钟

qpll_ref_clk_0: QPLL参考时钟

cpll_ref_clk_0 1 2 3:各个Channel CPLL参考时钟

rx_N_p、rx_N_n:AD9371和 FPGA LANE 之间传递数据的高速串行差分信号

rx_clk_0 1 2 3:各个Channel的 RXUSRCLK,RXUSRCLK2输入信号

rx_calign_0 1 2 3 :字符对齐使能信号

tx_clk_0 1 2 3:各个Channel的 TXUSRCLK,TXUSRCLK2输入信号

rx_0 1 2 3:rx 物理层提供给链路层的接收数据

rx_out_clk:RXOUTCLK

tx_out_clk:TXOUTCLK

tx_N_p、tx_N_n:AD9371和 FPGA LANE 之间传递数据的高速串行差分信号

RX_OS 和 RX基本一样,不过多描述