- 【爬虫】针对FingerprintJS反爬,selenium破解策略

steamedobun

项目管理爬虫爬虫selenium测试工具

目录FingerprintJS原理概述Selenium基础与应对思路代码实现实战(结合Selenium和UndetectedChromedriver绕过FingerprintJS)Canvas指纹随机化FingerprintJS原理概述FingerprintJS主要通过收集浏览器的各种特征信息来生成独一无二的指纹,这些信息包括但不限于:浏览器版本信息:不同浏览器版本在处理网页元素、执行JavaSc

- C、C++、Java到Python,编程入门学习什么语言好?

明天会比今天更好

C/C++编程入门编程语言程序员

最近,TIOBE更新了7月的编程语言榜单,常年霸榜的C、Java和Python依然蝉联前三位。万万没想到的是,R语言居然冲到了第八位,创下了史上最佳记录。而且后续随着业内对数据统计和挖掘需求的上涨,R语言热度颇有些势不可挡的架势。然而作为程序员吃饭的工具,编程语言之间也形成了某种鄙视链,各大论坛里弥漫着剑拔弩张的气氛,众口难调。也难怪有很多初学者会有疑惑,为什么会有这么多编程语言,我到底应该学什么

- 如何在Google Chrome浏览器中设置代理服务

m0_74824170

面试学习路线阿里巴巴chromephp前端

在日常使用互联网时,很多用户希望通过代理服务器来增强隐私保护、突破地理限制或访问受限内容。谷歌浏览器(GoogleChrome)作为全球最常用的浏览器之一,并不直接提供代理设置的选项,但我们可以通过操作系统的设置或借助第三方扩展来实现代理配置。一、什么是代理服务代理服务是指当用户发出请求时,代理服务器会代替用户向目标网站发送请求并接收响应。通过这种方式,代理服务器可以隐藏用户的真实IP地址,从而提

- 深入解析现代计算机内存访问机制:从虚拟地址到物理地址的转换与缓存优化

109702008

#linux系统编程#linux内核人工智能linuxc语言

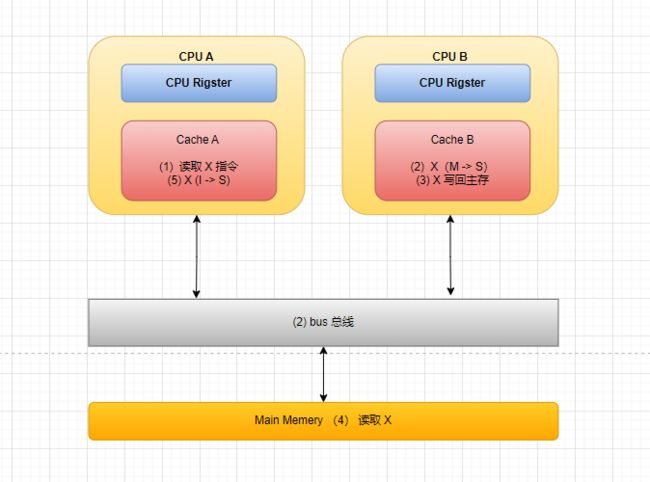

在现代计算机系统中,内存访问是一个复杂而高效的过程,涉及到多个硬件和软件组件的协同工作。本文将深入探讨从虚拟地址到物理地址的转换过程,以及缓存机制如何优化这一过程,确保数据访问的高效性。1.虚拟内存与虚拟地址在现代操作系统中,每个进程都有自己的虚拟地址空间。虚拟内存是一种抽象机制,它允许每个进程看到一个独立的、连续的内存空间,而无需关心物理内存的实际布局。虚拟地址是进程看到的内存地址,而物理地址是

- Java虚拟机的历程(jvm01)

小猫猫猫◍˃ᵕ˂◍

java开发语言

Java虚拟机的历程(jvm01)Java虚拟机(JVM)作为Java语言的核心技术之一,自诞生以来经历了多次迭代与演变。不同的虚拟机在性能、功能以及适用场景上各有侧重。本文将介绍Java虚拟机发展历程中的一些重要虚拟机,涵盖经典虚拟机(ClassicVM、ExactVM)、影响力最大的虚拟机(HotSpot、JRockit、J9)、移动端虚拟机(KVM)、性能最高的虚拟机(Azul、Liquid

- prometheus 服务java服务接入基础镜像配置

窗外的寒风

prometheusjavapython

环境变量设置:如果不经常修改配置,推荐在java镜像中把prometheus配置通过环境变量的方式统一配置,可以使用下面的参数,把端口进行暴漏(配置安全检查端口9998,启用所有安全检查接口,配置普罗米修斯的监测间隔,设置java服务名,把普罗米修斯的接口提升到根目录)ENVSPRING_APPLICATION_JSON='{"management.server.port":"9998","man

- leetcode——二叉树的直径(java)

gentle_ice

leetcode算法java数据结构

给你一棵二叉树的根节点,返回该树的直径。二叉树的直径是指树中任意两个节点之间最长路径的长度。这条路径可能经过也可能不经过根节点root。两节点之间路径的长度由它们之间边数表示。示例1:输入:root=[1,2,3,4,5]输出:3解释:3,取路径[4,2,1,3]或[5,2,1,3]的长度。示例2:输入:root=[1,2]输出:1解题方法:(递归)1.递归入口,当前根节点非空,否则返回-1。2.

- 赛博算卦之周易六十四卦JAVA实现:六幺算尽天下事,梅花化解天下苦。

钮钴禄·爱因斯晨

java学习java

佬们过年好呀~新年第一篇博客让我们来场赛博算命吧!更多文章:个人主页系列文章:JAVA专栏欢迎各位大佬来访哦~互三必回!!!文章目录#一、文化背景概述1.文化起源2.起卦步骤#二、卦象解读#三、justdoit!代码展示1.解析2.代码实现#四、总结#参考文献#一、文化背景概述1.文化起源六爻和六十四卦的文化起源可追溯至远古,那时人们为预测未来开展占卜,从龟甲兽骨裂纹到蓍草竹签筮法,逐步孕育了爻的

- java工作流模式、背包模式、适配器工厂模式整合架构,让服务任务编排更便捷

窗外的寒风

适配器模式架构

工作流和背包模式虽然不在23种常用设计模式中,但是在对任务编排处理类的业务代码使用起来是非常有用的。下面给大家介绍下工作流模式:例如,我之前有个项目需要对模型进行转换,因为不同配置的模型需要使用的转换方法不同,且单个模型需要经历多次的执行转换脚本,那就可以把每个脚本抽离出来封装为工作流中的一个字节点,通过对节点编排适应不同的转换任务,代码流程清晰,转换流程通过配置文件进行配置。背包模式呢,其实并不

- 如何使用 Nginx 配置反向代理?

IT专家-大狗

nginx运维

Nginx是一款高性能的开源Web服务器和反向代理服务器,广泛应用于负载均衡、缓存和静态文件服务。配置Nginx进行反向代理可以有效提高服务器性能,同时保护后端服务。本文将带您了解如何使用Nginx配置反向代理,并结合实际场景,使用Chrome浏览器进行调试和验证。什么是反向代理?反向代理是一种服务器设置,客户端的请求会首先经过代理服务器,再由代理服务器将请求转发至后端服务器。反向代理的主要功能包

- leetcode——二叉树的最大深度(java)

gentle_ice

javaleetcode算法数据结构

给定一个二叉树root,返回其最大深度。二叉树的最大深度是指从根节点到最远叶子节点的最长路径上的节点数。示例1:输入:root=[3,9,20,null,null,15,7]输出:3示例2:输入:root=[1,null,2]输出:2解题方法:(自底向上递归)1.递归入口:当前节点非空;否则,返回0;2.然后开始进入左子树递归获取左子树的深度;进入右子树递归获取右子树的深度。3.最后返回左子树与右

- npm常用命令

zhanggongzichu

npm前端node.js

以往nodejs版本Node.js—Node.js版本CNPMBinariesMirror查看当前版本npm-v查看node安装在哪里wherenode清除缓存npmcacheclean--force淘宝镜像(只支持下载,不支持上传发布)npmconfigsetregistryhttps://registry.npm.taobao.org设置公司私服地址npmconfigsetregistry私服

- JAVA常见面试题-RabbitMQ

waviss

JAVA常见面试题java开发语言面试

RabbitMQ数据类型Map:如果发送的消息类型是map类型,可以通过SerializationUtils.deserialize方法将消息转换成map类型。String(含json字符串类型):RabbitMQ原理RabbitMQ大致分为生产者、队列、消费者,在实际情况中生产者将消息发送到Exchange(交换器),再通过Banding操作将与队列关联起来。在绑定(Banding)Exchan

- java语句翻译_java基础语句翻译

我爱专利

java语句翻译

publicstaticvoidmain(String[]args){System.out.println("人生中的第一个代码-----");}}package包的关键字类文件的首行位置com.zhiyou100包名;结束标志语句的结束com.zhiyou100com。zhiyou100包说明当前类HelloWorld是在com。zhiyou100包内public关键字修饰符公共的修饰符权限任何

- Java面试题-rabbitmq-001

码者人生

面试题java技术面试题集java面试题java面试题rabbitmq

使用RabbitMQ有什么好处?消息基于什么传输?消息怎么路由?如何做到信息的可靠性?确保消息正确地发送至RabbitMQ?确保消息接受方消费了消息?休息不丢失不重复?如何避免消息重复投递或重复消费?为什么使用集群RabbitMQ节点不完全拷贝特性集群节点类型单节点系统必须是磁盘节点?RabbitMQ要求集群中至少有一个磁盘节点?mq的缺点

- NPM 使用介绍

lly202406

开发语言

NPM使用介绍引言NPM(NodePackageManager)是Node.js生态系统中的一个核心工具,用于管理JavaScript项目的依赖包。无论是开发一个小型脚本还是构建大型应用程序,NPM都能极大地提高开发效率。本文将详细介绍NPM的使用方法,包括安装、配置、依赖管理、包发布等,帮助您快速上手NPM。安装NPM在开始使用NPM之前,您需要确保已经安装了Node.js。NPM与Node.j

- 【华为机试真题JavaScript】尼科彻斯定理

forest_long

华为机试真题-JS动态规划javascriptpythonjava华为

目录题目描述输入描述输出描述参考示例参考代码机试介绍写在最后题目描述验证尼科彻斯定理,即:任何一个整数m的立方都可以写成m个连续奇数之和。例如:1^3=12^3=3+53^3=7+9+114^3=13+15+17+19输入一个正整数m(m≤100),将m的立方写成m个连续奇数之和的形式输出。数据范围:1≤m≤100进阶:时间复杂度:O(m),空间复杂度:O(1)输入描述输入一个int整数输出描述输

- SpringBoot:RabbitMQ-延迟队列

csdnlaoban

程序员java-rabbitmqspringbootrabbitmq

《一线大厂Java面试题解析+核心总结学习笔记+最新讲解视频+实战项目源码》,点击传送门,即可获取!com.alibabafastjson1.2.46org.springframework.bootspring-boot-starter-weborg.springframework.bootspring-boot-starter-testtest属性配置在application.propertie

- java.lang.NoSuchMethodException: org.apache.catalina.deploy.WebXml addServlet

漫无目的行走的月亮

java.lang.NoSuchMethodException:org.apache.catalina.deploy.WebXmladdServlet-------------------------------------------------------------------------------------------------------------------?解决此异常的方法是

- Java代码-八种数组排序方法

忧郁小王子x

算法java

一.冒泡排序1.1概述对于一组,多次将数组中的数两两比较,较大或者较小的数向后排(经过一轮比较后,最大/最小的数就会到结尾),循环直至有序排列。1.2代码实现importjava.lang.reflect.Array;importjava.util.Arrays;importjava.util.Scanner;publicclassmaopao{publicstaticvoidmain(Strin

- 【Java】Java Lambda List转List

奔向理想的星辰大海

云原生技术研发开发语言java

JavaLambdaList转List的实现方法引言在Java开发中,Lambda表达式是一种非常强大和常用的特性,它允许我们以一种更加简洁和灵活的方式编写代码。在处理集合类数据时,我们经常需要对列表进行转换操作,将其转换为另一种类型的列表。本文将介绍如何使用JavaLambda表达式将一个List转换为另一个List。实现步骤为了更好地理解整个过程,我们可以使用表格来展示每个步骤的具体操作。下面

- 面向切面之集中式登录架构设计

roy_xing

android架构

普通登录流程图集中式登录流程图把共有的业务通过AOP统一管理这里我们就需要使用AspectJ来实现面向切面的集中式登录什么是AspectJAspectJ是一个面向切面的框架,它扩展了Java语言。AspectJ定义了AOP语法,它有一个专门的编译器用来生成遵守Java字节编码规范的Class文件。Aspect是切面是切入点(PointCuts)和通知(Advice)的集合。Pointcut切入点通

- 语言模型与向量模型:深入解析与实例剖析

♢.*

语言模型人工智能自然语言处理

亲爱的小伙伴们,在求知的漫漫旅途中,若你对深度学习的奥秘、Java与Python的奇妙世界,亦或是读研论文的撰写攻略有所探寻,那不妨给我一个小小的关注吧。我会精心筹备,在未来的日子里不定期地为大家呈上这些领域的知识宝藏与实用经验分享。每一个点赞,都如同春日里的一缕阳光,给予我满满的动力与温暖,让我们在学习成长的道路上相伴而行,共同进步✨。期待你的关注与点赞哟!在自然语言处理领域,语言模型和向量模型

- Java二维数组排序

purpleFairyx

二维数组排序比较器Lambda表达式

今天在刷力扣的时候,有道题卡住了,没办法去看题解,发现题解是将其二维数组排序了,我才猛然发现我还不了解二位数组排序的知识。所以来记录一下。答案中的代码是这样的,假设需要排序的数组intervals:int[][]intervals={{2,3},{2,9},{4,5},{3,7},{6,7},{8,9},{1,10}};Arrays.sort(intervals,newComparator(){@

- 【Elasticsearch 】自定义分词器

程风破~

Elasticsearchelasticsearch大数据搜索引擎

博主简介:CSDN博客专家,历代文学网(PC端可以访问:https://literature.sinhy.com/#/?__c=1000,移动端可微信小程序搜索“历代文学”)总架构师,15年工作经验,精通Java编程,高并发设计,Springboot和微服务,熟悉Linux,ESXI虚拟化以及云原生Docker和K8s,热衷于探索科技的边界,并将理论知识转化为实际应用。保持对新技术的好奇心,乐于分

- 如何写好C++类

铮铭

c++

先讲一个笑话:同时学习两年Java的程序员在一起讨论的是面向对象和设计模式,而同时学习两年C++的程序员,在一起讨论的是template和各种语言规范到底怎么回事情。下面就从公开的资料中撸一撸如何写好一个c++类,从头文件(.h)需要包含的文件开始:1、#define保护:符号的命名最好是以下形式:___H_,比如foo项目中的foo/src/bar/baz.h文件应该这样保护:#ifndefFO

- Cisco NX-OS ACI 16.0(8f)M - 适用于 ACI 模式下的 Nexus 9000 系列交换机系统软件

cisco

CiscoNX-OSSystemSoftware-ACI16.0(8f)M适用于ACI模式下的CiscoNexus9000系列交换机系统软件请访问原文链接:https://sysin.org/blog/cisco-aci-16/查看最新版。原创作品,转载请保留出处。作者主页:sysin.orgCiscoNX-OS网络操作系统软件CiscoNX-OS操作系统助力网络紧跟业务发展步伐。NX-OS网络操

- IDEA+Java+SSH+Bootstrap+Mysql实现在线考试系统(含论文)

2401_89694162

javaintellij-ideassh

–Recordsoft_managerINSERTINTOt_managerVALUES(1,‘管理员’,‘admin’,‘admin’);–Tablestructurefort_paperDROPTABLEIFEXISTSt_paper;CREATETABLEt_paper(idint(11)NOTNULLAUTO_INCREMENT,joinDatedatetime(0)NULLDEFAULT

- Python 调用常见大模型 API 全解析

♢.*

python开发语言语言模型nlp

亲爱的小伙伴们,在求知的漫漫旅途中,若你对深度学习的奥秘、JAVA、PYTHON与SAP的奇妙世界,亦或是读研论文的撰写攻略有所探寻,那不妨给我一个小小的关注吧。我会精心筹备,在未来的日子里不定期地为大家呈上这些领域的知识宝藏与实用经验分享。每一个点赞,都如同春日里的一缕阳光,给予我满满的动力与温暖,让我们在学习成长的道路上相伴而行,共同进步✨。期待你的关注与点赞哟!调用通义千问接口获取APIKe

- java FastJSON自定义序列化和反序列化(扩展点)方法总结!10个步骤让你轻松掌握

墨瑾轩

一起学学Java【一】开发语言java

关注墨瑾轩,带你探索编程的奥秘!超萌技术攻略,轻松晋级编程高手技术宝库已备好,就等你来挖掘订阅墨瑾轩,智趣学习不孤单即刻启航,编程之旅更有趣嘿,小伙伴们!今天我们要一起探讨一个非常实用的话题——如何使用FastJSON自定义序列化和反序列化。你知道吗?FastJSON是阿里巴巴开源的一个高性能JSON库,广泛应用于Java项目中。虽然FastJSON提供了丰富的内置功能,但有时候我们还需要根据具体

- Java开发中,spring mvc 的线程怎么调用?

小麦麦子

springmvc

今天逛知乎,看到最近很多人都在问spring mvc 的线程http://www.maiziedu.com/course/java/ 的启动问题,觉得挺有意思的,那哥们儿问的也听仔细,下面的回答也很详尽,分享出来,希望遇对遇到类似问题的Java开发程序猿有所帮助。

问题:

在用spring mvc架构的网站上,设一线程在虚拟机启动时运行,线程里有一全局

- maven依赖范围

bitcarter

maven

1.test 测试的时候才会依赖,编译和打包不依赖,如junit不被打包

2.compile 只有编译和打包时才会依赖

3.provided 编译和测试的时候依赖,打包不依赖,如:tomcat的一些公用jar包

4.runtime 运行时依赖,编译不依赖

5.默认compile

依赖范围compile是支持传递的,test不支持传递

1.传递的意思是项目A,引用

- Jaxb org.xml.sax.saxparseexception : premature end of file

darrenzhu

xmlprematureJAXB

如果在使用JAXB把xml文件unmarshal成vo(XSD自动生成的vo)时碰到如下错误:

org.xml.sax.saxparseexception : premature end of file

很有可能时你直接读取文件为inputstream,然后将inputstream作为构建unmarshal需要的source参数。InputSource inputSource = new In

- CSS Specificity

周凡杨

html权重Specificitycss

有时候对于页面元素设置了样式,可为什么页面的显示没有匹配上呢? because specificity

CSS 的选择符是有权重的,当不同的选择符的样式设置有冲突时,浏览器会采用权重高的选择符设置的样式。

规则:

HTML标签的权重是1

Class 的权重是10

Id 的权重是100

- java与servlet

g21121

servlet

servlet 搞java web开发的人一定不会陌生,而且大家还会时常用到它。

下面是java官方网站上对servlet的介绍: java官网对于servlet的解释 写道

Java Servlet Technology Overview Servlets are the Java platform technology of choice for extending and enha

- eclipse中安装maven插件

510888780

eclipsemaven

1.首先去官网下载 Maven:

http://www.apache.org/dyn/closer.cgi/maven/binaries/apache-maven-3.2.3-bin.tar.gz

下载完成之后将其解压,

我将解压后的文件夹:apache-maven-3.2.3,

并将它放在 D:\tools目录下,

即 maven 最终的路径是:D:\tools\apache-mave

- jpa@OneToOne关联关系

布衣凌宇

jpa

Nruser里的pruserid关联到Pruser的主键id,实现对一个表的增删改,另一个表的数据随之增删改。

Nruser实体类

//*****************************************************************

@Entity

@Table(name="nruser")

@DynamicInsert @Dynam

- 我的spring学习笔记11-Spring中关于声明式事务的配置

aijuans

spring事务配置

这两天学到事务管理这一块,结合到之前的terasoluna框架,觉得书本上讲的还是简单阿。我就把我从书本上学到的再结合实际的项目以及网上看到的一些内容,对声明式事务管理做个整理吧。我看得Spring in Action第二版中只提到了用TransactionProxyFactoryBean和<tx:advice/>,定义注释驱动这三种,我承认后两种的内容很好,很强大。但是实际的项目当中

- java 动态代理简单实现

antlove

javahandlerproxydynamicservice

dynamicproxy.service.HelloService

package dynamicproxy.service;

public interface HelloService {

public void sayHello();

}

dynamicproxy.service.impl.HelloServiceImpl

package dynamicp

- JDBC连接数据库

百合不是茶

JDBC编程JAVA操作oracle数据库

如果我们要想连接oracle公司的数据库,就要首先下载oralce公司的驱动程序,将这个驱动程序的jar包导入到我们工程中;

JDBC链接数据库的代码和固定写法;

1,加载oracle数据库的驱动;

&nb

- 单例模式中的多线程分析

bijian1013

javathread多线程java多线程

谈到单例模式,我们立马会想到饿汉式和懒汉式加载,所谓饿汉式就是在创建类时就创建好了实例,懒汉式在获取实例时才去创建实例,即延迟加载。

饿汉式:

package com.bijian.study;

public class Singleton {

private Singleton() {

}

// 注意这是private 只供内部调用

private static

- javascript读取和修改原型特别需要注意原型的读写不具有对等性

bijian1013

JavaScriptprototype

对于从原型对象继承而来的成员,其读和写具有内在的不对等性。比如有一个对象A,假设它的原型对象是B,B的原型对象是null。如果我们需要读取A对象的name属性值,那么JS会优先在A中查找,如果找到了name属性那么就返回;如果A中没有name属性,那么就到原型B中查找name,如果找到了就返回;如果原型B中也没有

- 【持久化框架MyBatis3六】MyBatis3集成第三方DataSource

bit1129

dataSource

MyBatis内置了数据源的支持,如:

<environments default="development">

<environment id="development">

<transactionManager type="JDBC" />

<data

- 我程序中用到的urldecode和base64decode,MD5

bitcarter

cMD5base64decodeurldecode

这里是base64decode和urldecode,Md5在附件中。因为我是在后台所以需要解码:

string Base64Decode(const char* Data,int DataByte,int& OutByte)

{

//解码表

const char DecodeTable[] =

{

0, 0, 0, 0, 0, 0

- 腾讯资深运维专家周小军:QQ与微信架构的惊天秘密

ronin47

社交领域一直是互联网创业的大热门,从PC到移动端,从OICQ、MSN到QQ。到了移动互联网时代,社交领域应用开始彻底爆发,直奔黄金期。腾讯在过去几年里,社交平台更是火到爆,QQ和微信坐拥几亿的粉丝,QQ空间和朋友圈各种刷屏,写心得,晒照片,秀视频,那么谁来为企鹅保驾护航呢?支撑QQ和微信海量数据背后的架构又有哪些惊天内幕呢?本期大讲堂的内容来自今年2月份ChinaUnix对腾讯社交网络运营服务中心

- java-69-旋转数组的最小元素。把一个数组最开始的若干个元素搬到数组的末尾,我们称之为数组的旋转。输入一个排好序的数组的一个旋转,输出旋转数组的最小元素

bylijinnan

java

public class MinOfShiftedArray {

/**

* Q69 旋转数组的最小元素

* 把一个数组最开始的若干个元素搬到数组的末尾,我们称之为数组的旋转。输入一个排好序的数组的一个旋转,输出旋转数组的最小元素。

* 例如数组{3, 4, 5, 1, 2}为{1, 2, 3, 4, 5}的一个旋转,该数组的最小值为1。

*/

publ

- 看博客,应该是有方向的

Cb123456

反省看博客

看博客,应该是有方向的:

我现在就复习以前的,在补补以前不会的,现在还不会的,同时完善完善项目,也看看别人的博客.

我刚突然想到的:

1.应该看计算机组成原理,数据结构,一些算法,还有关于android,java的。

2.对于我,也快大四了,看一些职业规划的,以及一些学习的经验,看看别人的工作总结的.

为什么要写

- [开源与商业]做开源项目的人生活上一定要朴素,尽量减少对官方和商业体系的依赖

comsci

开源项目

为什么这样说呢? 因为科学和技术的发展有时候需要一个平缓和长期的积累过程,但是行政和商业体系本身充满各种不稳定性和不确定性,如果你希望长期从事某个科研项目,但是却又必须依赖于某种行政和商业体系,那其中的过程必定充满各种风险。。。

所以,为避免这种不确定性风险,我

- 一个 sql优化 ([精华] 一个查询优化的分析调整全过程!很值得一看 )

cwqcwqmax9

sql

见 http://www.itpub.net/forum.php?mod=viewthread&tid=239011

Web翻页优化实例

提交时间: 2004-6-18 15:37:49 回复 发消息

环境:

Linux ve

- Hibernat and Ibatis

dashuaifu

Hibernateibatis

Hibernate VS iBATIS 简介 Hibernate 是当前最流行的O/R mapping框架,当前版本是3.05。它出身于sf.net,现在已经成为Jboss的一部分了 iBATIS 是另外一种优秀的O/R mapping框架,当前版本是2.0。目前属于apache的一个子项目了。 相对Hibernate“O/R”而言,iBATIS 是一种“Sql Mappi

- 备份MYSQL脚本

dcj3sjt126com

mysql

#!/bin/sh

# this shell to backup mysql

#

[email protected] (QQ:1413161683 DuChengJiu)

_dbDir=/var/lib/mysql/

_today=`date +%w`

_bakDir=/usr/backup/$_today

[ ! -d $_bakDir ] && mkdir -p

- iOS第三方开源库的吐槽和备忘

dcj3sjt126com

ios

转自

ibireme的博客 做iOS开发总会接触到一些第三方库,这里整理一下,做一些吐槽。 目前比较活跃的社区仍旧是Github,除此以外也有一些不错的库散落在Google Code、SourceForge等地方。由于Github社区太过主流,这里主要介绍一下Github里面流行的iOS库。 首先整理了一份

Github上排名靠

- html wlwmanifest.xml

eoems

htmlxml

所谓优化wp_head()就是把从wp_head中移除不需要元素,同时也可以加快速度。

步骤:

加入到function.php

remove_action('wp_head', 'wp_generator');

//wp-generator移除wordpress的版本号,本身blog的版本号没什么意义,但是如果让恶意玩家看到,可能会用官网公布的漏洞攻击blog

remov

- 浅谈Java定时器发展

hacksin

java并发timer定时器

java在jdk1.3中推出了定时器类Timer,而后在jdk1.5后由Dou Lea从新开发出了支持多线程的ScheduleThreadPoolExecutor,从后者的表现来看,可以考虑完全替代Timer了。

Timer与ScheduleThreadPoolExecutor对比:

1.

Timer始于jdk1.3,其原理是利用一个TimerTask数组当作队列

- 移动端页面侧边导航滑入效果

ini

jqueryWebhtml5cssjavascirpt

效果体验:http://hovertree.com/texiao/mobile/2.htm可以使用移动设备浏览器查看效果。效果使用到jquery-2.1.4.min.js,该版本的jQuery库是用于支持HTML5的浏览器上,不再兼容IE8以前的浏览器,现在移动端浏览器一般都支持HTML5,所以使用该jQuery没问题。HTML文件代码:

<!DOCTYPE html>

<h

- AspectJ+Javasist记录日志

kane_xie

aspectjjavasist

在项目中碰到这样一个需求,对一个服务类的每一个方法,在方法开始和结束的时候分别记录一条日志,内容包括方法名,参数名+参数值以及方法执行的时间。

@Override

public String get(String key) {

// long start = System.currentTimeMillis();

// System.out.println("Be

- redis学习笔记

MJC410621

redisNoSQL

1)nosql数据库主要由以下特点:非关系型的、分布式的、开源的、水平可扩展的。

1,处理超大量的数据

2,运行在便宜的PC服务器集群上,

3,击碎了性能瓶颈。

1)对数据高并发读写。

2)对海量数据的高效率存储和访问。

3)对数据的高扩展性和高可用性。

redis支持的类型:

Sring 类型

set name lijie

get name lijie

set na

- 使用redis实现分布式锁

qifeifei

在多节点的系统中,如何实现分布式锁机制,其中用redis来实现是很好的方法之一,我们先来看一下jedis包中,有个类名BinaryJedis,它有个方法如下:

public Long setnx(final byte[] key, final byte[] value) {

checkIsInMulti();

client.setnx(key, value);

ret

- BI并非万能,中层业务管理报表要另辟蹊径

张老师的菜

大数据BI商业智能信息化

BI是商业智能的缩写,是可以帮助企业做出明智的业务经营决策的工具,其数据来源于各个业务系统,如ERP、CRM、SCM、进销存、HER、OA等。

BI系统不同于传统的管理信息系统,他号称是一个整体应用的解决方案,是融入管理思想的强大系统:有着系统整体的设计思想,支持对所有

- 安装rvm后出现rvm not a function 或者ruby -v后提示没安装ruby的问题

wudixiaotie

function

1.在~/.bashrc最后加入

[[ -s "$HOME/.rvm/scripts/rvm" ]] && source "$HOME/.rvm/scripts/rvm"

2.重新启动terminal输入:

rvm use ruby-2.2.1 --default

把当前安装的ruby版本设为默