Xilinx VIVADO 中 DDR3(AXI4)的使用(1)创建 IP 核

1、前言

DDR3 SDRAM 简称 DDR3,是当今较为常见的一种储存器,在计算机及嵌入式产品中得到广泛应用, 特别是应用在涉及到大量数据交互的场合,比如电脑的内存条。DDR3的时序相当复杂,对DDR3 的读写操作大都借助 IP 核来完成。

MIG(Memory Interface Generators) IP 核是 Xilinx 公司针对 DDR 存储器开发的 IP,里面集成存储器控制模块,实现 DDR 读写操作的 控制流程。在默认情况下,MIG IP 核对外分出两组接口(即 Naive 接口)。一是用户接口,就是用户(FPGA)同 MIG 交互的接口,用户只有充分掌握了这些接口才能操作 MIG。二是 DDR 物理芯片接口,负责产生具体的操作时序,并直接操作芯片管脚。

本次使用的工程环境为 Xilinx VIVADO 2018.3,使用 MIG IP 核的 AXI4 接口。

2、AXI 协议通道简介

协议的制定是要建立在总线构成之上的,AXI 总线协议包括 AXI4,AXI4-Lite,AXI4-Stream 三类,均分为为主(master)、从(slave)两端,他们之间一般需要通过一个 AXI Interconnect 相连接,其作用是提供将一个或多个 AXI 主设备连接到一个或多个 AXI 从设备的一种交换机制。主设备和从设备需要按照约定好的数据传输方式来发送和接收数据。AXI 协议就是描述了主设备和从设备之间的数据传输方式。在该协议中,主设备和从设备之间通过握手信号建立连接。

AXI 协议将读地址通道,读数据通道,写地址通道,写数据通道,写响应通道分开,各自通道都有自己的握手协议。每个通道互不干扰却又彼此依赖。这是 AXI 高效的原因之一。五个通道都有各自的 VALID/READY 握手信号对。每个通道握手信号对的名称如下图所示,更多 AXI 通道释义详情请参考官方文档。

AXI4 总线的通道:

(1)读地址通道(AR channel):包含 ARVALID,ARADDR,ARREADY 信号;

(2)读数据通道(R channel):包含 RVALID, RDATA,RREADY,RRESP 信号;

(3)写地址通道(AW channel):包含 AWVALID,AWADDR,AWREADY 信号;

(4)写数据通道(W channel):包含 WVALID,WDATA,WSTRB, WREADY 信号;

(5)写应答通道(B channel):包含 BVALID,BRESP,BREADY 信号;

(6)系统通道:包含:ACLK,ARESETN 信号。

3、MIG IP 核建立步骤

VIVADO 工程的创建及 IP 核的调用方法,此处直接跳过。

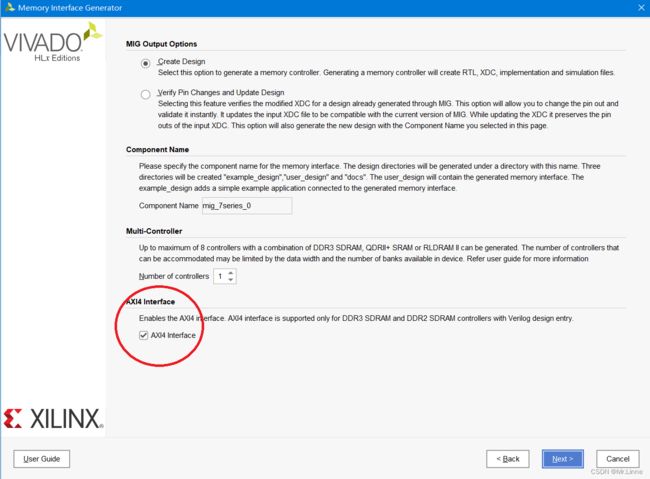

(1)IP 命名与 AXI4 接口选择

打开 IP 核配置界面,首先设置 IP 核名称,此处默认名称为 mig_7series_0,并勾选最下方的 AXI4 Interface,如下图红圈所示。

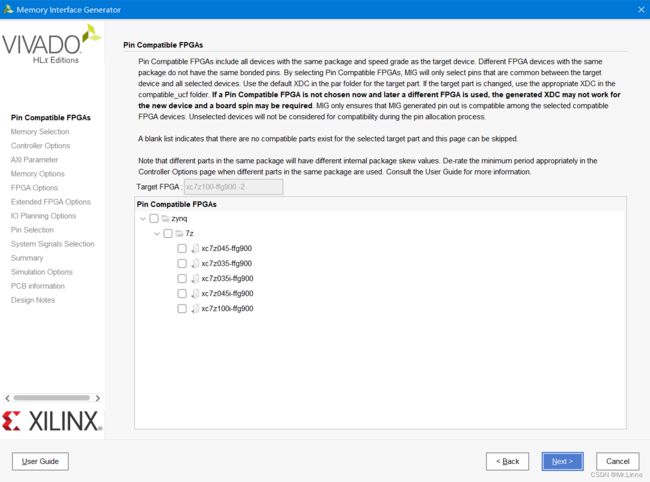

下一页配置该 IP 核兼容的 FPGA 芯片型号,此处无需关心,点击 Next。

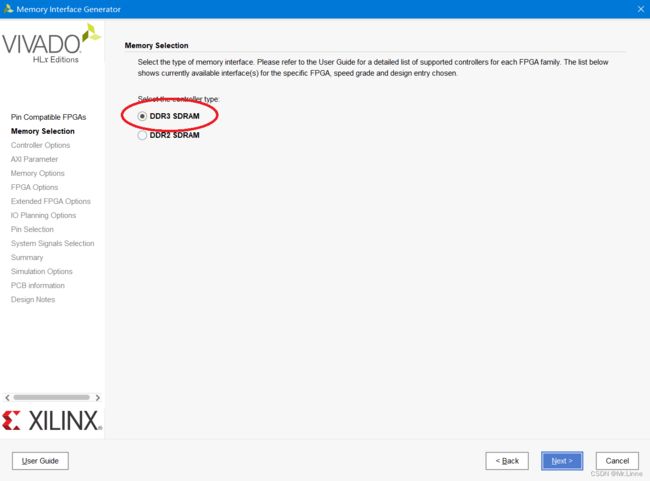

选择 DDR3 SDRAM 模式,也就是该芯片支持的DDR类型,点击 Next。

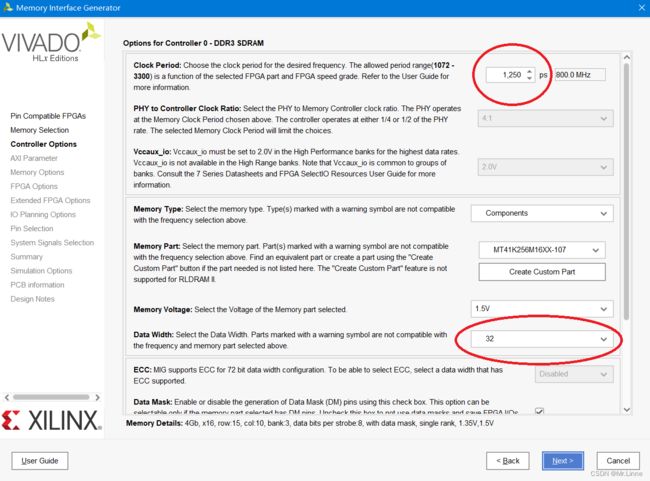

(2)时钟设置

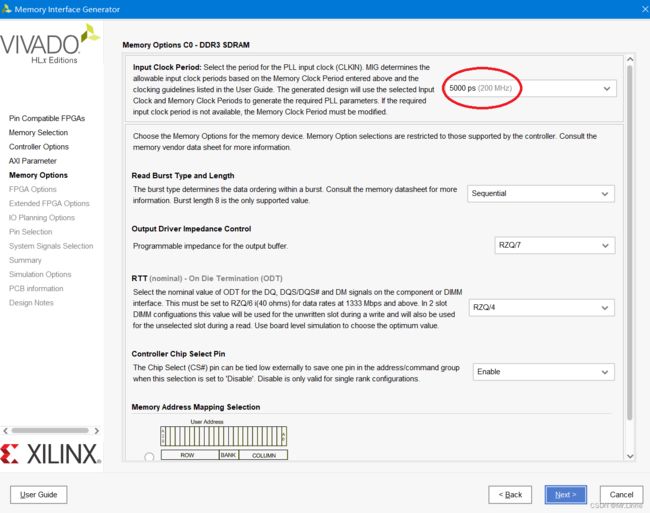

Clock Period 为 DDR3 芯片工作的时钟,这里我们选择 800MHz。控制 DDR 的数据流分为 2:1 或 4:1 两种模式,我们使用 4:1 模式,则 DDR3 的用户读写时钟为 800 ÷ 4 = 200 MHz。

(3)DDR3 芯片型号设置

选择响应的DDR芯片的型号,也可以进行定制,此处我们选择的是 MT41K256XX-107。

(4)读写位宽设置

选择 DDR 的数据位宽,这里我们选择 32位,那么用户实际操作的读写数据为空即为 32 × 8 = 256 比特。

(5)使用数据掩码

Data Mask 处打勾,但实际应用中很少用到掩码功能。

其余的不太重要,就是控制器内部的一些策略问题,详细的可以查看技术手册,点击 Next。

进入下一页时,顶部的 Data Width 已经自动显示为 256;然后将 Narrow Burst Support 选择置 1,表示支持突发传输数据,如图中红圈所示。其余配置均默认,点击 Next。

(6)系统(参考)时钟配置

用户提供给DDR的系统时钟,用来生成前面400MHz的时钟,这里选择200MHz,因为可以与后面的参考时钟共用一个时钟。

(7)SDRAM 连续模式

SDRAM 有两种模式:连续模式(Sequential)与中断模式(Interleaved),一般选择连续模式。

(8)DDR 寻址模式

即最下方的 Memory Address Mapping Selection,选择用户地址与 DDR3 的实际地址的映射方式,我们选择常用的 BANK-ROW-COLUMN 映射模式。

其余配置均默认,点击 Next。

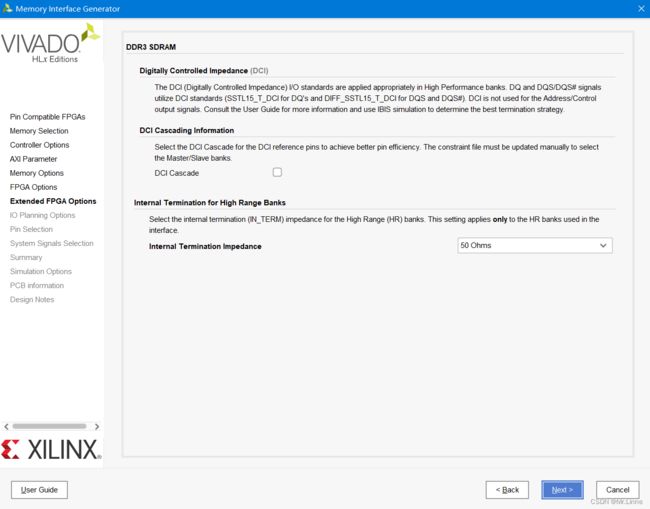

(9)设置时钟类型

生成时钟的类型,这里面 No Buffer 代表是FPGA内部产生的时钟,其余两个是外部时钟引脚直接连接的选项,分别对应着单端与差分时钟信号。这里的 System Clock 和 Reference Clock 我们都使用 No Buffer 模式。其余配置默认即可,点击 Next。

下一页保持默认,点击 Next。

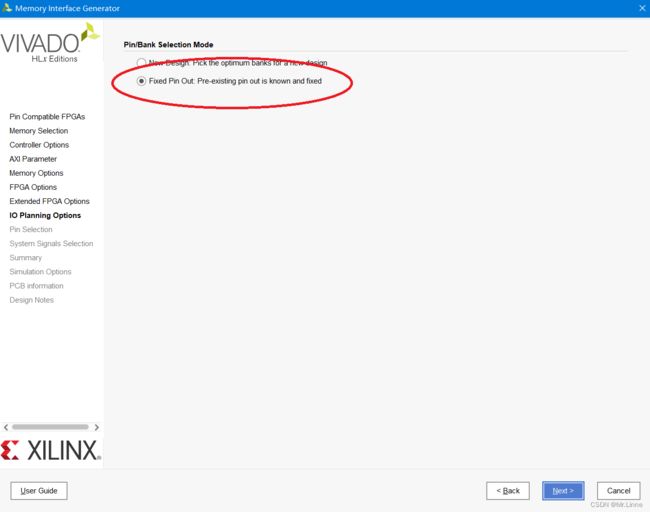

(10)配置引脚

准备根据自己的 FPGA 芯片引脚绑定 DDR3 引脚,如下选择 Fixed Pin Out Pre-existing pin out is known and fixed。

找到对应开发板的DDR引脚文件,一般FPGA开发板都有相配套的 ucf 或 xdc 文件,点击验证一下文件的有效性。点击 Next。

此后是 System signal selection 页面,直接点击 Next。

然后是 Summary 页面打印的 IP 核信息,直接点击 Next。

然后是 Simulation Options 页面,选择接受(Accept)协议,点击 Next。

最后一路 Next,生成 MIG IP 核即可。到此为止,我们建立了一个完整新的 MIG IP,并且知道了 MIG IP 核调用过程中每个选项所代表的意义。