11.1~11.2数电实验一些点+11.4~11.5报错复盘

方框写在前面是说这个数有多大,写在后面是说这类数有多少

前面的用于计数,每位无实际意义;后面每位都代表一个同类型的,即数组,每位有实际意义

使用四位格雷码作为深度为8的FIFO的读写指针

将格雷码转换成四位二进制数,使用二进制数低三位作为访问RAM的地址

声明两个初级信号

如果能写,就接着写,让waddr_bin+1

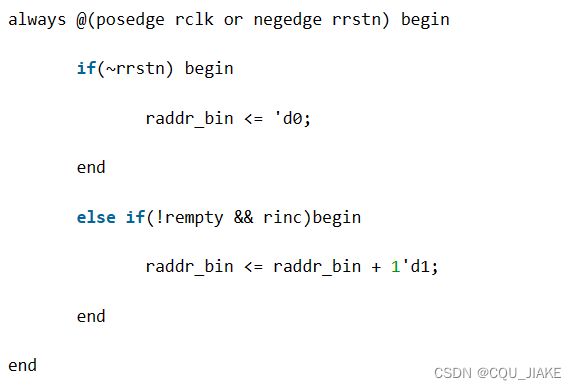

如果能读,就接着读,让raddr_bin+1

声明格雷码信号与读写指针

获取格雷码,即让原码与原码向左移位一位后的码的异或,按位与

格雷码是循环编码,其循环的长度与本身格雷码的长度有关,自身长度越长,循环周期越长

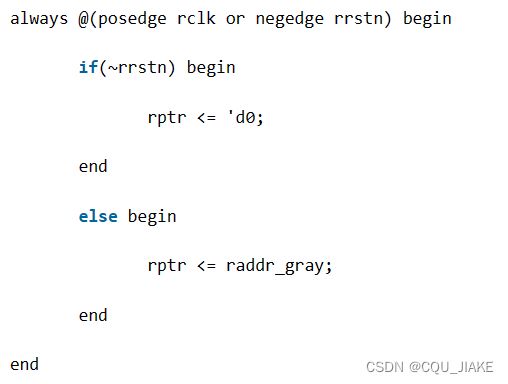

得到真正的读写指针

开始一拍时,rptr_buff为0,rptr_syn为0;第二拍,rptr_buff为rptr(1),rptr_syn为0;第三拍,前者为rptr(2),后者为rptr(1).

当写指针比读指针多循环RAM一周时,此时读写指针的最高位和此高位都相反,其余位相同,FIFO为满

FIFO的组成部分主要为三块,存储模块,指针计数器,判断逻辑

存储模块主要用于数据的暂时存储,深度可配置

指针计数器主要用于计算当前的存储模块读写指针的位置

判断逻辑主要是为了比较读写指针,判断当前FIFO的状态

存储模块的RAM逻辑就是管存储,用reg模拟即可,主要就是给读写指针,然后依据读写指针对所存储的数据进行更改与获取

让读写地址的位宽增加一位最高位作为奇偶标记,便于空满的判断

满的时候

一开始电路复位后,FIFO为空,持续以每次一个字的速度将数据写入FIFO,写指针将不断增加,当达到地址范围的最大值时,写指针又回到0.将数据写入FIFO时,写使能信号有效。始终周期结束时,写指针调整为下一个值

写指针和读指针以环形方式移动,写指针在前,读指针追随

只有当队列为空或者满时,写入和读出的指针才可能相同

要确保不会发生两种情形,一是给满的队列写入数据,即所有位置都有有效数据,没有多余数据;二是从空的队列中读取数据。

故当FIFO为满时,禁止继续写入数据;为空时,禁止继续读取数据

同步FIFO中,写入和读出操作可以同时进行,也可以发生在不同的时刻

报错复盘

顶层文件无reg

在顶层模块里,也就是说不涉及里面信号具体变化方式的文件,只是把各部分串联,联系起来的顶层文件里,也即没有always的模块里,就不需要定义reg型,线型就行

我将uart_done(出问题的信号)的变量类型设为reg了,也就是我是reg uart_done这个信号的,这样做是错误的,哪怕你在接收模块确实定义的是reg类型,但是在顶层模块的时候,它可以视为是一条单纯的线而已,所以应该用wire,

ambiguous clock in event control

第二种情况就是赋值冲突,同一个always里允许两个if并行,但是两个if里的内容不能有交集

操作?

操作复位时,必须要保持读使能开关打开,不然复位后依然显示的上一个数