rv1126-rv1109-sfc-分区表获取流程分析

[ 0.000000] Kernel command line: user_debug=31 storagemedia=mtd androidboot.storagemedia=mtd androidboot.mode=normal earlycon=uart8250,mmio32,0xff570000 console=ttyFIQ0 root=/dev/mtdblock3 rootfstype=cramfs snd_aloop.index=7 mtdparts=spi-nand0:0x100000@0x200000(vnvm),0x800000@0x300000(uboot),0x800000@0xb00000(boot),0x7800000@0x1300000(rootfs),0x100000@0x8b00000(lbcmd),0x100000@0x8c00000(lbflash),0x100000@0x8d00000(lbflash2),0x100000@0x8e00000(lbcfg),0x100000@0x8f00000(lbcfg2),0x500000@0x9000000(backup),0x3c00000@0x9500000(ro),0x1e00000@0xd100000(rw),0x100000@0xef00000(misc),0xf60000@0xf000000(factory)

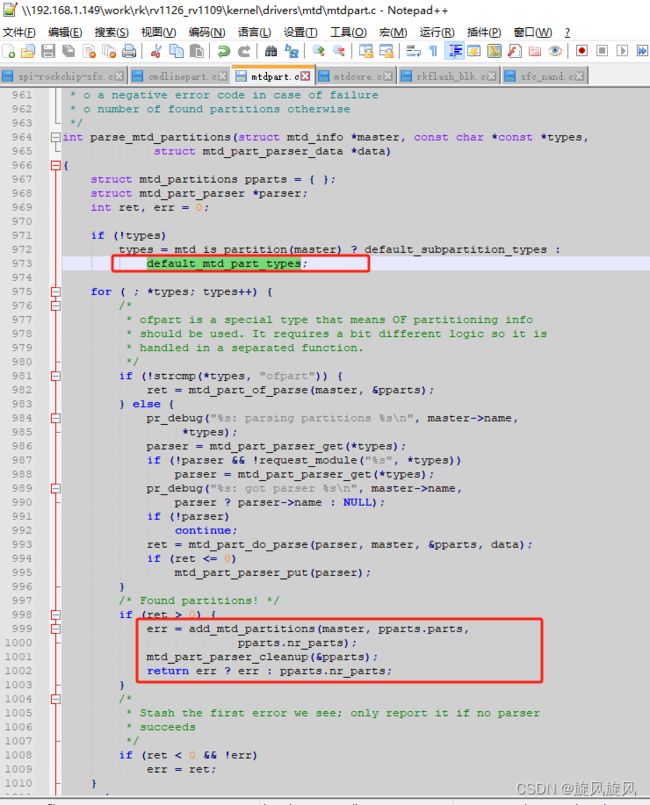

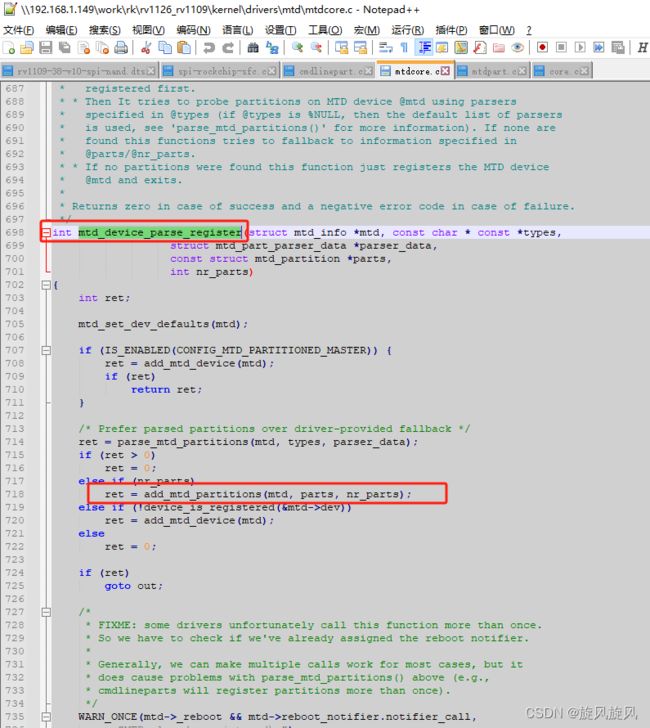

[ 0.000000] Dentry cache hash table entries: 131072 (order: 7, 524288 bytes)然后我们根据 mtdparts=spi-nand0:xxx分析

.name = "cmdlinepart"

===========================================================================

关闭了rkflash后,移植了自己的SFC(spi驱动)

遇到问题,一直卡死进不去系统;

查问题是:VFS: Cannot open root device "mtdblock3" or unknown-block(0,0): error -6

是块设备节点没有生成,一路追查未果;最后发现是name不对;

吧mtd_info的name修改之后就匹配上了;正常开机

原来:mtd->name = "spi-nand: spi-nand0";

修改后:mtd->name = "spi-nand0";

然后就可以开机了。

下面是sfc源码:

// SPDX-License-Identifier: GPL-2.0-only

/*

* Rockchip Serial Flash Controller Driver

*

* Copyright (c) 2017-2021, Rockchip Inc.

* Author: Shawn Lin

* Chris Morgan

* Jon Lin

*/

#include

#include

#include

#include

#include

#include

#include

#include

#include

#include

#include

#include

/* System control */

#define SFC_CTRL 0x0

#define SFC_CTRL_PHASE_SEL_NEGETIVE BIT(1)

#define SFC_CTRL_CMD_BITS_SHIFT 8

#define SFC_CTRL_ADDR_BITS_SHIFT 10

#define SFC_CTRL_DATA_BITS_SHIFT 12

/* Interrupt mask */

#define SFC_IMR 0x4

#define SFC_IMR_RX_FULL BIT(0)

#define SFC_IMR_RX_UFLOW BIT(1)

#define SFC_IMR_TX_OFLOW BIT(2)

#define SFC_IMR_TX_EMPTY BIT(3)

#define SFC_IMR_TRAN_FINISH BIT(4)

#define SFC_IMR_BUS_ERR BIT(5)

#define SFC_IMR_NSPI_ERR BIT(6)

#define SFC_IMR_DMA BIT(7)

/* Interrupt clear */

#define SFC_ICLR 0x8

#define SFC_ICLR_RX_FULL BIT(0)

#define SFC_ICLR_RX_UFLOW BIT(1)

#define SFC_ICLR_TX_OFLOW BIT(2)

#define SFC_ICLR_TX_EMPTY BIT(3)

#define SFC_ICLR_TRAN_FINISH BIT(4)

#define SFC_ICLR_BUS_ERR BIT(5)

#define SFC_ICLR_NSPI_ERR BIT(6)

#define SFC_ICLR_DMA BIT(7)

/* FIFO threshold level */

#define SFC_FTLR 0xc

#define SFC_FTLR_TX_SHIFT 0

#define SFC_FTLR_TX_MASK 0x1f

#define SFC_FTLR_RX_SHIFT 8

#define SFC_FTLR_RX_MASK 0x1f

/* Reset FSM and FIFO */

#define SFC_RCVR 0x10

#define SFC_RCVR_RESET BIT(0)

/* Enhanced mode */

#define SFC_AX 0x14

/* Address Bit number */

#define SFC_ABIT 0x18

/* Interrupt status */

#define SFC_ISR 0x1c

#define SFC_ISR_RX_FULL_SHIFT BIT(0)

#define SFC_ISR_RX_UFLOW_SHIFT BIT(1)

#define SFC_ISR_TX_OFLOW_SHIFT BIT(2)

#define SFC_ISR_TX_EMPTY_SHIFT BIT(3)

#define SFC_ISR_TX_FINISH_SHIFT BIT(4)

#define SFC_ISR_BUS_ERR_SHIFT BIT(5)

#define SFC_ISR_NSPI_ERR_SHIFT BIT(6)

#define SFC_ISR_DMA_SHIFT BIT(7)

/* FIFO status */

#define SFC_FSR 0x20

#define SFC_FSR_TX_IS_FULL BIT(0)

#define SFC_FSR_TX_IS_EMPTY BIT(1)

#define SFC_FSR_RX_IS_EMPTY BIT(2)

#define SFC_FSR_RX_IS_FULL BIT(3)

#define SFC_FSR_TXLV_MASK GENMASK(12, 8)

#define SFC_FSR_TXLV_SHIFT 8

#define SFC_FSR_RXLV_MASK GENMASK(20, 16)

#define SFC_FSR_RXLV_SHIFT 16

/* FSM status */

#define SFC_SR 0x24

#define SFC_SR_IS_IDLE 0x0

#define SFC_SR_IS_BUSY 0x1

/* Raw interrupt status */

#define SFC_RISR 0x28

#define SFC_RISR_RX_FULL BIT(0)

#define SFC_RISR_RX_UNDERFLOW BIT(1)

#define SFC_RISR_TX_OVERFLOW BIT(2)

#define SFC_RISR_TX_EMPTY BIT(3)

#define SFC_RISR_TRAN_FINISH BIT(4)

#define SFC_RISR_BUS_ERR BIT(5)

#define SFC_RISR_NSPI_ERR BIT(6)

#define SFC_RISR_DMA BIT(7)

/* Version */

#define SFC_VER 0x2C

#define SFC_VER_3 0x3

#define SFC_VER_4 0x4

#define SFC_VER_5 0x5

/* Delay line controller resiter */

#define SFC_DLL_CTRL0 0x3C

#define SFC_DLL_CTRL0_SCLK_SMP_DLL BIT(15)

#define SFC_DLL_CTRL0_DLL_MAX_VER4 0xFFU

#define SFC_DLL_CTRL0_DLL_MAX_VER5 0x1FFU

/* Master trigger */

#define SFC_DMA_TRIGGER 0x80

#define SFC_DMA_TRIGGER_START 1

/* Src or Dst addr for master */

#define SFC_DMA_ADDR 0x84

/* Length control register extension 32GB */

#define SFC_LEN_CTRL 0x88

#define SFC_LEN_CTRL_TRB_SEL 1

#define SFC_LEN_EXT 0x8C

/* Command */

#define SFC_CMD 0x100

#define SFC_CMD_IDX_SHIFT 0

#define SFC_CMD_DUMMY_SHIFT 8

#define SFC_CMD_DIR_SHIFT 12

#define SFC_CMD_DIR_RD 0

#define SFC_CMD_DIR_WR 1

#define SFC_CMD_ADDR_SHIFT 14

#define SFC_CMD_ADDR_0BITS 0

#define SFC_CMD_ADDR_24BITS 1

#define SFC_CMD_ADDR_32BITS 2

#define SFC_CMD_ADDR_XBITS 3

#define SFC_CMD_TRAN_BYTES_SHIFT 16

#define SFC_CMD_CS_SHIFT 30

/* Address */

#define SFC_ADDR 0x104

/* Data */

#define SFC_DATA 0x108

/* The controller and documentation reports that it supports up to 4 CS

* devices (0-3), however I have only been able to test a single CS (CS 0)

* due to the configuration of my device.

*/

#define SFC_MAX_CHIPSELECT_NUM 4

/* The SFC can transfer max 16KB - 1 at one time

* we set it to 15.5KB here for alignment.

*/

#define SFC_MAX_IOSIZE_VER3 (512 * 31)

/* DMA is only enabled for large data transmission */

#define SFC_DMA_TRANS_THRETHOLD (0x40)

/* Maximum clock values from datasheet suggest keeping clock value under

* 150MHz. No minimum or average value is suggested.

*/

#define SFC_MAX_SPEED (150 * 1000 * 1000)

struct rockchip_sfc {

struct device *dev;

void __iomem *regbase;

struct clk *hclk;

struct clk *clk;

u32 frequency;

/* virtual mapped addr for dma_buffer */

void *buffer;

dma_addr_t dma_buffer;

struct completion cp;

bool use_dma;

u32 max_iosize;

u16 version;

};

static int rockchip_sfc_reset(struct rockchip_sfc *sfc)

{

int err;

u32 status;

writel_relaxed(SFC_RCVR_RESET, sfc->regbase + SFC_RCVR);

err = readl_poll_timeout(sfc->regbase + SFC_RCVR, status,

!(status & SFC_RCVR_RESET), 20,

jiffies_to_usecs(HZ));

if (err)

dev_err(sfc->dev, "SFC reset never finished\n");

/* Still need to clear the masked interrupt from RISR */

writel_relaxed(0xFFFFFFFF, sfc->regbase + SFC_ICLR);

dev_dbg(sfc->dev, "reset\n");

return err;

}

static u16 rockchip_sfc_get_version(struct rockchip_sfc *sfc)

{

return (u16)(readl(sfc->regbase + SFC_VER) & 0xffff);

}

static u32 rockchip_sfc_get_max_iosize(struct rockchip_sfc *sfc)

{

return SFC_MAX_IOSIZE_VER3;

}

static void rockchip_sfc_irq_unmask(struct rockchip_sfc *sfc, u32 mask)

{

u32 reg;

/* Enable transfer complete interrupt */

reg = readl(sfc->regbase + SFC_IMR);

reg &= ~mask;

writel(reg, sfc->regbase + SFC_IMR);

}

static void rockchip_sfc_irq_mask(struct rockchip_sfc *sfc, u32 mask)

{

u32 reg;

/* Disable transfer finish interrupt */

reg = readl(sfc->regbase + SFC_IMR);

reg |= mask;

writel(reg, sfc->regbase + SFC_IMR);

}

static int rockchip_sfc_init(struct rockchip_sfc *sfc)

{

writel(0, sfc->regbase + SFC_CTRL);

writel(0xFFFFFFFF, sfc->regbase + SFC_ICLR);

rockchip_sfc_irq_mask(sfc, 0xFFFFFFFF);

if (rockchip_sfc_get_version(sfc) >= SFC_VER_4)

writel(SFC_LEN_CTRL_TRB_SEL, sfc->regbase + SFC_LEN_CTRL);

return 0;

}

static int rockchip_sfc_wait_txfifo_ready(struct rockchip_sfc *sfc, u32 timeout_us)

{

int ret = 0;

u32 status;

ret = readl_poll_timeout(sfc->regbase + SFC_FSR, status,

status & SFC_FSR_TXLV_MASK, 0,

timeout_us);

if (ret) {

dev_dbg(sfc->dev, "sfc wait tx fifo timeout\n");

return -ETIMEDOUT;

}

return (status & SFC_FSR_TXLV_MASK) >> SFC_FSR_TXLV_SHIFT;

}

static int rockchip_sfc_wait_rxfifo_ready(struct rockchip_sfc *sfc, u32 timeout_us)

{

int ret = 0;

u32 status;

ret = readl_poll_timeout(sfc->regbase + SFC_FSR, status,

status & SFC_FSR_RXLV_MASK, 0,

timeout_us);

if (ret) {

dev_dbg(sfc->dev, "sfc wait rx fifo timeout\n");

return -ETIMEDOUT;

}

return (status & SFC_FSR_RXLV_MASK) >> SFC_FSR_RXLV_SHIFT;

}

static void rockchip_sfc_adjust_op_work(struct spi_mem_op *op)

{

if (unlikely(op->dummy.nbytes && !op->addr.nbytes)) {

/*

* SFC not support output DUMMY cycles right after CMD cycles, so

* treat it as ADDR cycles.

*/

op->addr.nbytes = op->dummy.nbytes;

op->addr.buswidth = op->dummy.buswidth;

op->addr.val = 0xFFFFFFFFF;

op->dummy.nbytes = 0;

}

}

static int rockchip_sfc_xfer_setup(struct rockchip_sfc *sfc,

struct spi_mem *mem,

const struct spi_mem_op *op,

u32 len)

{

u32 ctrl = 0, cmd = 0;

/* set CMD */

cmd = op->cmd.opcode;

ctrl |= ((op->cmd.buswidth >> 1) << SFC_CTRL_CMD_BITS_SHIFT);

/* set ADDR */

if (op->addr.nbytes) {

if (op->addr.nbytes == 4) {

cmd |= SFC_CMD_ADDR_32BITS << SFC_CMD_ADDR_SHIFT;

} else if (op->addr.nbytes == 3) {

cmd |= SFC_CMD_ADDR_24BITS << SFC_CMD_ADDR_SHIFT;

} else {

cmd |= SFC_CMD_ADDR_XBITS << SFC_CMD_ADDR_SHIFT;

writel(op->addr.nbytes * 8 - 1, sfc->regbase + SFC_ABIT);

}

ctrl |= ((op->addr.buswidth >> 1) << SFC_CTRL_ADDR_BITS_SHIFT);

}

/* set DUMMY */

if (op->dummy.nbytes) {

if (op->dummy.buswidth == 4)

cmd |= op->dummy.nbytes * 2 << SFC_CMD_DUMMY_SHIFT;

else if (op->dummy.buswidth == 2)

cmd |= op->dummy.nbytes * 4 << SFC_CMD_DUMMY_SHIFT;

else

cmd |= op->dummy.nbytes * 8 << SFC_CMD_DUMMY_SHIFT;

}

/* set DATA */

if (sfc->version >= SFC_VER_4) /* Clear it if no data to transfer */

writel(len, sfc->regbase + SFC_LEN_EXT);

else

cmd |= len << SFC_CMD_TRAN_BYTES_SHIFT;

if (len) {

if (op->data.dir == SPI_MEM_DATA_OUT)

cmd |= SFC_CMD_DIR_WR << SFC_CMD_DIR_SHIFT;

ctrl |= ((op->data.buswidth >> 1) << SFC_CTRL_DATA_BITS_SHIFT);

}

if (!len && op->addr.nbytes)

cmd |= SFC_CMD_DIR_WR << SFC_CMD_DIR_SHIFT;

/* set the Controller */

ctrl |= SFC_CTRL_PHASE_SEL_NEGETIVE;

cmd |= spi_get_chipselect(mem->spi, 0) << SFC_CMD_CS_SHIFT;

dev_dbg(sfc->dev, "sfc addr.nbytes=%x(x%d) dummy.nbytes=%x(x%d)\n",

op->addr.nbytes, op->addr.buswidth,

op->dummy.nbytes, op->dummy.buswidth);

dev_dbg(sfc->dev, "sfc ctrl=%x cmd=%x addr=%llx len=%x\n",

ctrl, cmd, op->addr.val, len);

writel(ctrl, sfc->regbase + SFC_CTRL);

writel(cmd, sfc->regbase + SFC_CMD);

if (op->addr.nbytes)

writel(op->addr.val, sfc->regbase + SFC_ADDR);

return 0;

}

static int rockchip_sfc_write_fifo(struct rockchip_sfc *sfc, const u8 *buf, int len)

{

u8 bytes = len & 0x3;

u32 dwords;

int tx_level;

u32 write_words;

u32 tmp = 0;

dwords = len >> 2;

while (dwords) {

tx_level = rockchip_sfc_wait_txfifo_ready(sfc, 1000);

if (tx_level < 0)

return tx_level;

write_words = min_t(u32, tx_level, dwords);

iowrite32_rep(sfc->regbase + SFC_DATA, buf, write_words);

buf += write_words << 2;

dwords -= write_words;

}

/* write the rest non word aligned bytes */

if (bytes) {

tx_level = rockchip_sfc_wait_txfifo_ready(sfc, 1000);

if (tx_level < 0)

return tx_level;

memcpy(&tmp, buf, bytes);

writel(tmp, sfc->regbase + SFC_DATA);

}

return len;

}

static int rockchip_sfc_read_fifo(struct rockchip_sfc *sfc, u8 *buf, int len)

{

u8 bytes = len & 0x3;

u32 dwords;

u8 read_words;

int rx_level;

int tmp;

/* word aligned access only */

dwords = len >> 2;

while (dwords) {

rx_level = rockchip_sfc_wait_rxfifo_ready(sfc, 1000);

if (rx_level < 0)

return rx_level;

read_words = min_t(u32, rx_level, dwords);

ioread32_rep(sfc->regbase + SFC_DATA, buf, read_words);

buf += read_words << 2;

dwords -= read_words;

}

/* read the rest non word aligned bytes */

if (bytes) {

rx_level = rockchip_sfc_wait_rxfifo_ready(sfc, 1000);

if (rx_level < 0)

return rx_level;

tmp = readl(sfc->regbase + SFC_DATA);

memcpy(buf, &tmp, bytes);

}

return len;

}

static int rockchip_sfc_fifo_transfer_dma(struct rockchip_sfc *sfc, dma_addr_t dma_buf, size_t len)

{

writel(0xFFFFFFFF, sfc->regbase + SFC_ICLR);

writel((u32)dma_buf, sfc->regbase + SFC_DMA_ADDR);

writel(SFC_DMA_TRIGGER_START, sfc->regbase + SFC_DMA_TRIGGER);

return len;

}

static int rockchip_sfc_xfer_data_poll(struct rockchip_sfc *sfc,

const struct spi_mem_op *op, u32 len)

{

dev_dbg(sfc->dev, "sfc xfer_poll len=%x\n", len);

if (op->data.dir == SPI_MEM_DATA_OUT)

return rockchip_sfc_write_fifo(sfc, op->data.buf.out, len);

else

return rockchip_sfc_read_fifo(sfc, op->data.buf.in, len);

}

static int rockchip_sfc_xfer_data_dma(struct rockchip_sfc *sfc,

const struct spi_mem_op *op, u32 len)

{

int ret;

dev_dbg(sfc->dev, "sfc xfer_dma len=%x\n", len);

if (op->data.dir == SPI_MEM_DATA_OUT)

memcpy(sfc->buffer, op->data.buf.out, len);

ret = rockchip_sfc_fifo_transfer_dma(sfc, sfc->dma_buffer, len);

if (!wait_for_completion_timeout(&sfc->cp, msecs_to_jiffies(2000))) {

dev_err(sfc->dev, "DMA wait for transfer finish timeout\n");

ret = -ETIMEDOUT;

}

rockchip_sfc_irq_mask(sfc, SFC_IMR_DMA);

if (op->data.dir == SPI_MEM_DATA_IN)

memcpy(op->data.buf.in, sfc->buffer, len);

return ret;

}

static int rockchip_sfc_xfer_done(struct rockchip_sfc *sfc, u32 timeout_us)

{

int ret = 0;

u32 status;

ret = readl_poll_timeout(sfc->regbase + SFC_SR, status,

!(status & SFC_SR_IS_BUSY),

20, timeout_us);

if (ret) {

dev_err(sfc->dev, "wait sfc idle timeout\n");

rockchip_sfc_reset(sfc);

ret = -EIO;

}

return ret;

}

static int rockchip_sfc_exec_mem_op(struct spi_mem *mem, const struct spi_mem_op *op)

{

struct rockchip_sfc *sfc = spi_controller_get_devdata(mem->spi->controller);

u32 len = op->data.nbytes;

int ret;

if (unlikely(mem->spi->max_speed_hz != sfc->frequency)) {

ret = clk_set_rate(sfc->clk, mem->spi->max_speed_hz);

if (ret)

return ret;

sfc->frequency = mem->spi->max_speed_hz;

dev_dbg(sfc->dev, "set_freq=%dHz real_freq=%ldHz\n",

sfc->frequency, clk_get_rate(sfc->clk));

}

rockchip_sfc_adjust_op_work((struct spi_mem_op *)op);

rockchip_sfc_xfer_setup(sfc, mem, op, len);

if (len) {

if (likely(sfc->use_dma) && len >= SFC_DMA_TRANS_THRETHOLD) {

init_completion(&sfc->cp);

rockchip_sfc_irq_unmask(sfc, SFC_IMR_DMA);

ret = rockchip_sfc_xfer_data_dma(sfc, op, len);

} else {

ret = rockchip_sfc_xfer_data_poll(sfc, op, len);

}

if (ret != len) {

dev_err(sfc->dev, "xfer data failed ret %d dir %d\n", ret, op->data.dir);

return -EIO;

}

}

return rockchip_sfc_xfer_done(sfc, 100000);

}

static int rockchip_sfc_adjust_op_size(struct spi_mem *mem, struct spi_mem_op *op)

{

struct rockchip_sfc *sfc = spi_controller_get_devdata(mem->spi->controller);

op->data.nbytes = min(op->data.nbytes, sfc->max_iosize);

return 0;

}

static const struct spi_controller_mem_ops rockchip_sfc_mem_ops = {

.exec_op = rockchip_sfc_exec_mem_op,

.adjust_op_size = rockchip_sfc_adjust_op_size,

};

static irqreturn_t rockchip_sfc_irq_handler(int irq, void *dev_id)

{

struct rockchip_sfc *sfc = dev_id;

u32 reg;

reg = readl(sfc->regbase + SFC_RISR);

/* Clear interrupt */

writel_relaxed(reg, sfc->regbase + SFC_ICLR);

if (reg & SFC_RISR_DMA) {

complete(&sfc->cp);

return IRQ_HANDLED;

}

return IRQ_NONE;

}

static int rockchip_sfc_probe(struct platform_device *pdev)

{

struct device *dev = &pdev->dev;

struct spi_controller *host;

struct rockchip_sfc *sfc;

int ret;

#if 1

host = spi_alloc_master(&pdev->dev, sizeof(*sfc));

#else

host = devm_spi_alloc_host(&pdev->dev, sizeof(*sfc));

#endif

if (!host)

return -ENOMEM;

host->flags = SPI_CONTROLLER_HALF_DUPLEX;

host->mem_ops = &rockchip_sfc_mem_ops;

host->dev.of_node = pdev->dev.of_node;

host->mode_bits = SPI_TX_QUAD | SPI_TX_DUAL | SPI_RX_QUAD | SPI_RX_DUAL;

host->max_speed_hz = SFC_MAX_SPEED;

host->num_chipselect = SFC_MAX_CHIPSELECT_NUM;

sfc = spi_controller_get_devdata(host);

sfc->dev = dev;

sfc->regbase = devm_platform_ioremap_resource(pdev, 0);

if (IS_ERR(sfc->regbase))

return PTR_ERR(sfc->regbase);

sfc->clk = devm_clk_get(&pdev->dev, "clk_sfc");

if (IS_ERR(sfc->clk)) {

dev_err(&pdev->dev, "Failed to get sfc interface clk\n");

return PTR_ERR(sfc->clk);

}

sfc->hclk = devm_clk_get(&pdev->dev, "hclk_sfc");

if (IS_ERR(sfc->hclk)) {

dev_err(&pdev->dev, "Failed to get sfc ahb clk\n");

return PTR_ERR(sfc->hclk);

}

sfc->use_dma = !of_property_read_bool(sfc->dev->of_node,

"rockchip,sfc-no-dma");

if (sfc->use_dma) {

ret = dma_set_mask_and_coherent(dev, DMA_BIT_MASK(32));

if (ret) {

dev_warn(dev, "Unable to set dma mask\n");

return ret;

}

sfc->buffer = dmam_alloc_coherent(dev, SFC_MAX_IOSIZE_VER3,

&sfc->dma_buffer,

GFP_KERNEL);

if (!sfc->buffer)

return -ENOMEM;

}

ret = clk_prepare_enable(sfc->hclk);

if (ret) {

dev_err(&pdev->dev, "Failed to enable ahb clk\n");

goto err_hclk;

}

ret = clk_prepare_enable(sfc->clk);

if (ret) {

dev_err(&pdev->dev, "Failed to enable interface clk\n");

goto err_clk;

}

/* Find the irq */

ret = platform_get_irq(pdev, 0);

if (ret < 0)

goto err_irq;

ret = devm_request_irq(dev, ret, rockchip_sfc_irq_handler,

0, pdev->name, sfc);

if (ret) {

dev_err(dev, "Failed to request irq\n");

goto err_irq;

}

ret = rockchip_sfc_init(sfc);

if (ret)

goto err_irq;

sfc->max_iosize = rockchip_sfc_get_max_iosize(sfc);

sfc->version = rockchip_sfc_get_version(sfc);

ret = spi_register_controller(host);

if (ret)

goto err_irq;

return 0;

err_irq:

clk_disable_unprepare(sfc->clk);

err_clk:

clk_disable_unprepare(sfc->hclk);

err_hclk:

return ret;

}

#if 1

static int rockchip_sfc_remove(struct platform_device *pdev)

#else

static void rockchip_sfc_remove(struct platform_device *pdev)

#endif

{

struct spi_controller *host = platform_get_drvdata(pdev);

struct rockchip_sfc *sfc = platform_get_drvdata(pdev);

spi_unregister_controller(host);

clk_disable_unprepare(sfc->clk);

clk_disable_unprepare(sfc->hclk);

#if 1

return 0;

#endif

}

static const struct of_device_id rockchip_sfc_dt_ids[] = {

{ .compatible = "rockchip,sfc"},

{ /* sentinel */ }

};

MODULE_DEVICE_TABLE(of, rockchip_sfc_dt_ids);

static struct platform_driver rockchip_sfc_driver = {

.driver = {

.name = "rockchip-sfc",

.of_match_table = rockchip_sfc_dt_ids,

},

.probe = rockchip_sfc_probe,

#if 1

.remove = rockchip_sfc_remove,

#else

.remove_new = rockchip_sfc_remove,

#endif

};

module_platform_driver(rockchip_sfc_driver);

MODULE_LICENSE("GPL v2");

MODULE_DESCRIPTION("Rockchip Serial Flash Controller Driver");

MODULE_AUTHOR("Shawn Lin ");

MODULE_AUTHOR("Chris Morgan ");

MODULE_AUTHOR("Jon Lin ");

整个补丁:

sdk@ubuntu:~/work/rk/rv1126_rv1109$ git diff kernel/

diff --git a/kernel/arch/arm/boot/dts/rv1109-38-v10-spi-nand.dts b/kernel/arch/arm/boot/dts/rv1109-38-v10-spi-nand.dts

index b45b79e49..89679ca66 100755

--- a/kernel/arch/arm/boot/dts/rv1109-38-v10-spi-nand.dts

+++ b/kernel/arch/arm/boot/dts/rv1109-38-v10-spi-nand.dts

@@ -12,7 +12,8 @@

compatible = "rockchip,rv1109-38-v10-spi-nand", "rockchip,rv1109";

chosen {

- bootargs = "earlycon=uart8250,mmio32,0xff570000 console=ttyFIQ0 ubi.mtd=3 ubi.block=0,rootfs root=/dev/mtdblock3 rootfstype=cramfs snd_aloop.index=7";

+// bootargs = "earlycon=uart8250,mmio32,0xff570000 console=ttyFIQ0 ubi.mtd=3 ubi.block=0,rootfs root=/dev/mtdblock3 rootfstype=cramfs snd_aloop.index=7";

+ bootargs = "earlycon=uart8250,mmio32,0xff570000 console=ttyFIQ0 root=/dev/mtdblock3 rootfstype=cramfs snd_aloop.index=7";

};

/delete-node/ vdd-npu;

@@ -315,6 +316,23 @@

&sfc {

status = "okay";

+ u-boot,dm-spl;

+ /delete-property/ pinctrl-names;

+ /delete-property/ pinctrl-0;

+ /delete-property/ assigned-clocks;

+ /delete-property/ assigned-clock-rates;

+

+ #address-cells = <1>;

+ #size-cells = <0>;

+ spi_nand0: flash@0 {

+ u-boot,dm-spl;

+ compatible = "spi-nand";

+ reg = <0>;

+ spi-tx-bus-width = <1>;

+ spi-rx-bus-width = <4>;

+ spi-max-frequency = <96000000>;

+ status = "okay";

+ };

};

&u2phy_host {

diff --git a/kernel/arch/arm/configs/rv1126_defconfig b/kernel/arch/arm/configs/rv1126_defconfig

index 80acf93f0..e49d7c981 100755

--- a/kernel/arch/arm/configs/rv1126_defconfig

+++ b/kernel/arch/arm/configs/rv1126_defconfig

@@ -331,10 +331,10 @@ CONFIG_ROCKCHIP_OTP=y

CONFIG_TEE=y

CONFIG_OPTEE=y

CONFIG_RK_FLASH=y

-CONFIG_RK_SFC_NAND=y

-CONFIG_RK_SFC_NAND_MTD=y

-CONFIG_RK_SFC_NOR=y

-CONFIG_RK_SFC_NOR_MTD=y

+CONFIG_RK_SFC_NAND=n

+CONFIG_RK_SFC_NAND_MTD=n

+CONFIG_RK_SFC_NOR=n

+CONFIG_RK_SFC_NOR_MTD=n

CONFIG_EXT4_FS=y

# CONFIG_DNOTIFY is not set

CONFIG_OVERLAY_FS=y

@@ -415,3 +415,13 @@ CONFIG_IP_ROUTE_MULTIPATH=y

CONFIG_IP_ROUTE_VERBOSE=y

CONFIG_CRAMFS=y

CONFIG_MTD_BLOCK=y

+CONFIG_YAFFS_FS=y

+CONFIG_YAFFS_YAFFS1=y

+CONFIG_YAFFS_YAFFS2=y

+CONFIG_YAFFS_AUTO_YAFFS2=y

+CONFIG_YAFFS_XATTR=y

+CONFIG_MTD_NAND=y

+CONFIG_MTD_SPI_NAND=y

+CONFIG_SPI_NAND_XTX=y

+CONFIG_MTD_NAND_ROCKCHIP_V6=y

+CONFIG_SPI_ROCKCHIP_SFC=y

diff --git a/kernel/drivers/mtd/nand/spi/Makefile b/kernel/drivers/mtd/nand/spi/Makefile

old mode 100644

new mode 100755

index b74e074b3..e5ea6bc5c

--- a/kernel/drivers/mtd/nand/spi/Makefile

+++ b/kernel/drivers/mtd/nand/spi/Makefile

@@ -1,3 +1,3 @@

# SPDX-License-Identifier: GPL-2.0

-spinand-objs := core.o macronix.o micron.o winbond.o

+spinand-objs := core.o macronix.o micron.o winbond.o xtx.o

obj-$(CONFIG_MTD_SPI_NAND) += spinand.o

diff --git a/kernel/drivers/mtd/nand/spi/core.c b/kernel/drivers/mtd/nand/spi/core.c

old mode 100644

new mode 100755

index 48b3ab26b..465de4a67

--- a/kernel/drivers/mtd/nand/spi/core.c

+++ b/kernel/drivers/mtd/nand/spi/core.c

@@ -765,6 +765,7 @@ static const struct spinand_manufacturer *spinand_manufacturers[] = {

¯onix_spinand_manufacturer,

µn_spinand_manufacturer,

&winbond_spinand_manufacturer,

+ &xtx_spinand_manufacturer,

};

static int spinand_manufacturer_detect(struct spinand_device *spinand)

@@ -1088,11 +1089,13 @@ static int spinand_probe(struct spi_mem *mem)

mutex_init(&spinand->lock);

mtd = spinand_to_mtd(spinand);

mtd->dev.parent = &mem->spi->dev;

-

+pr_err("%s:spinand_probe mtd_device_register\n", mtd->name);

+mtd->name = "spi-nand0";

+pr_err("%s:spinand_probe mtd_device_register\n", mtd->name);

ret = spinand_init(spinand);

if (ret)

return ret;

-

+// pr_err("%s:spinand_probe mtd_device_register\n", mtd->name);

ret = mtd_device_register(mtd, NULL, 0);

if (ret)

goto err_spinand_cleanup;

diff --git a/kernel/drivers/spi/Kconfig b/kernel/drivers/spi/Kconfig

old mode 100644

new mode 100755

index 671d07834..9048f78ab

--- a/kernel/drivers/spi/Kconfig

+++ b/kernel/drivers/spi/Kconfig

@@ -508,6 +508,17 @@ config SPI_ROCKCHIP

The main usecase of this controller is to use spi flash as boot

device.

+config SPI_ROCKCHIP_SFC

+ tristate "Rockchip SPI controller sfc driver"

+ help

+ This selects a driver for Rockchip SPI SFC controller.

+

+ If you say yes to this option, support will be included for

+ RK3066, RK3188 and RK3288 families of SPI controller.

+ Rockchip SPI controller support DMA transport and PIO mode.

+ The main usecase of this controller is to use spi flash as boot

+ device.

+

config SPI_RB4XX

tristate "Mikrotik RB4XX SPI master"

depends on SPI_MASTER && ATH79

diff --git a/kernel/drivers/spi/Makefile b/kernel/drivers/spi/Makefile

old mode 100644

new mode 100755

index a90d55970..b832da728

--- a/kernel/drivers/spi/Makefile

+++ b/kernel/drivers/spi/Makefile

@@ -76,6 +76,7 @@ obj-$(CONFIG_SPI_PXA2XX) += spi-pxa2xx-platform.o

obj-$(CONFIG_SPI_PXA2XX_PCI) += spi-pxa2xx-pci.o

obj-$(CONFIG_SPI_QUP) += spi-qup.o

obj-$(CONFIG_SPI_ROCKCHIP) += spi-rockchip.o

+obj-$(CONFIG_SPI_ROCKCHIP_SFC) += spi-rockchip-sfc.o

obj-$(CONFIG_SPI_RB4XX) += spi-rb4xx.o

obj-$(CONFIG_SPI_RSPI) += spi-rspi.o

obj-$(CONFIG_SPI_S3C24XX) += spi-s3c24xx-hw.o

diff --git a/kernel/fs/Kconfig b/kernel/fs/Kconfig

old mode 100644

new mode 100755

index b8d003f02..f250c6675

--- a/kernel/fs/Kconfig

+++ b/kernel/fs/Kconfig

@@ -244,6 +244,7 @@ source "fs/befs/Kconfig"

source "fs/bfs/Kconfig"

source "fs/efs/Kconfig"

source "fs/jffs2/Kconfig"

+source "fs/yaffs2/Kconfig"

# UBIFS File system configuration

source "fs/ubifs/Kconfig"

source "fs/cramfs/Kconfig"

diff --git a/kernel/fs/Makefile b/kernel/fs/Makefile

old mode 100644

new mode 100755

index 5030ac905..09bfb6c30

--- a/kernel/fs/Makefile

+++ b/kernel/fs/Makefile

@@ -100,6 +100,7 @@ obj-$(CONFIG_NTFS_FS) += ntfs/

obj-$(CONFIG_UFS_FS) += ufs/

obj-$(CONFIG_EFS_FS) += efs/

obj-$(CONFIG_JFFS2_FS) += jffs2/

+obj-$(CONFIG_YAFFS_FS) += yaffs2/

obj-$(CONFIG_UBIFS_FS) += ubifs/

obj-$(CONFIG_AFFS_FS) += affs/

obj-$(CONFIG_ROMFS_FS) += romfs/

diff --git a/kernel/include/linux/mtd/mtd.h b/kernel/include/linux/mtd/mtd.h

old mode 100644

new mode 100755

index 035d641e8..19c749eba

--- a/kernel/include/linux/mtd/mtd.h

+++ b/kernel/include/linux/mtd/mtd.h

@@ -40,9 +40,18 @@ struct mtd_info;

* or was not specific to any particular block.

*/

struct erase_info {

- uint64_t addr;

- uint64_t len;

- uint64_t fail_addr;

+ struct mtd_info *mtd;

+ uint64_t addr;

+ uint64_t len;

+ uint64_t fail_addr;

+ u_long time;

+ u_long retries;

+ unsigned dev;

+ unsigned cell;

+ void (*callback) (struct erase_info *self);

+ u_long priv;

+ u_char state;

+ struct erase_info *next;

};

struct mtd_erase_region_info {

diff --git a/kernel/include/linux/mtd/spinand.h b/kernel/include/linux/mtd/spinand.h

old mode 100644

new mode 100755

index 088ff96c3..fefc16169

--- a/kernel/include/linux/mtd/spinand.h

+++ b/kernel/include/linux/mtd/spinand.h

@@ -197,7 +197,7 @@ struct spinand_manufacturer {

extern const struct spinand_manufacturer macronix_spinand_manufacturer;

extern const struct spinand_manufacturer micron_spinand_manufacturer;

extern const struct spinand_manufacturer winbond_spinand_manufacturer;

-

+extern const struct spinand_manufacturer xtx_spinand_manufacturer;

/**

* struct spinand_op_variants - SPI NAND operation variants

* @ops: the list of variants for a given operation

diff --git a/kernel/include/linux/spi/spi.h b/kernel/include/linux/spi/spi.h

old mode 100644

new mode 100755

index 6be77fa5a..171921a2d

--- a/kernel/include/linux/spi/spi.h

+++ b/kernel/include/linux/spi/spi.h

@@ -215,6 +215,11 @@ static inline void *spi_get_drvdata(struct spi_device *spi)

return dev_get_drvdata(&spi->dev);

}

+static inline u8 spi_get_chipselect(const struct spi_device *spi, u8 idx) {

+ return spi->chip_select;

+}

+

+

struct spi_message;

struct spi_transfer;