ICC Student Guide Unit0&Unit1

Unit 0 Introduction & Overview

Goal:目标

Use IC Compiler to efficiently perform nonhierarchical chip-level design planning, placement, clock tree synthesis and routing on designs with moderate timing and congestion challenges

Target Audience:面向人群

ASIC, back-end or layout designers who will be using IC Compiler for physical design

Prerequisite Knowledge: 需要的前置知识

■A Unix text editor, for example: emacs, vi, pine

■ Basic physical design, layout or standard cell

Place&Route concepts and terms, including:

• Standard cells and libraries

• Floorplanning, placement and routing fundamentals

• Clock skew

• Causes and effects of congestion, setup and hold timing

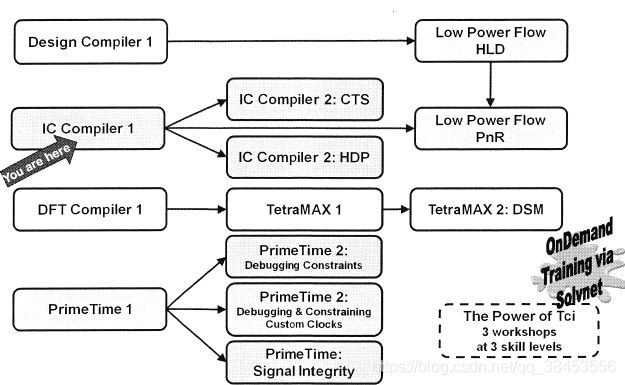

Curriculum Flow:

有用的链接:training.synopsys.com

solvnet.synopsys.com/training

ICC Flow:

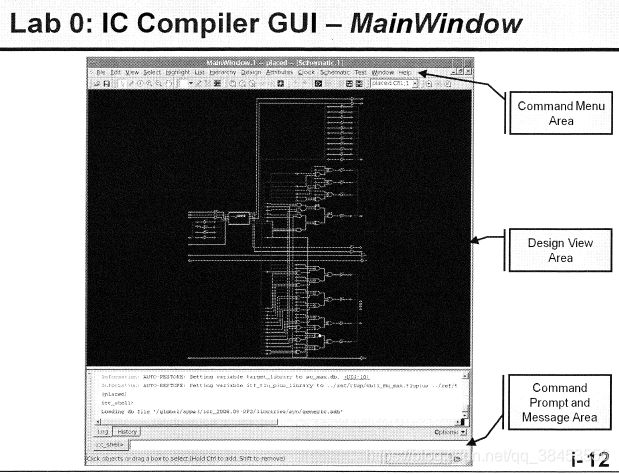

ICC GUI:

自行完成Lab 0A,熟悉ICC的使用方法以及简单命令,Lab 0B是选做,会介绍拓展用法。

Unit 1 Data Setup

学完这个单元以后你应该学会:

■ Perform data setup to create an initial design cell which is ready for design planning:

• Load necessary synthesis data: logical libraries,

constraints, netlist

加载必要的综合文件

• Load necessary physical design data: physical

libraries, technology file, RC parasitic model files

加载必要的物理文件

• Create a Milkyway design library and initial design cell

创建新的mw设计库和新的设计单元

• Apply timing and optimization controls

• Perform checks on libraries, RC parasitic models, constraints and timing

■ Execute a basic flow which includes loading a

floorplan and performing placement, CTS and

routing

实现基本的操作流程,包括加载floorplan并完成布局、CTS以及布线

注意:教程当中包含很多的脚本和流程图,但是不代表它们是标准/通用/推荐的流程,只是用来更好地展示材料。实际应用场合下要根据需要制定脚本和命令的使用顺序。

并且也不存在所谓的“万能脚本“。

电路的物理实现,在逻辑层面需要读入前端处理完成的.db,.sdc,.v文件;物理库层面需要.mw,.tf,TLU文件,这些文件不会被直接读入ICC的内存,而是会作为配置文件储存在design library中。

[.db文件]:

也被成为logical library,为基本单元或者hard macro提供时序和功能信息,同时定义最大扇出电容等design rule,通常与DC中使用的库是相同的,会用target_library/link_library来设置该文件。

注意:.db文件由制造厂商提供

[.sdc,.v文件]:

在前端变成与综合的过程中得到。

[.mw]:

此格式的physical reference library,包含标准单元、maro、pad cell的物理信息,如下图:

以及包含这些单元在布局时所需要的信息,例如宽度、需要的最小间隔,对绕线的要求等,如下图:

用命令create_mw_lib -mw_reference_library来设置该文件。

注:标准单元的高度一般是相同的(并且无法转向),但是也有一些单元会占据多个单位的高度。

mw格式的physical library:

mw格式的physical reference library,其本质是一个包含了多种view的目录,每个view所呈现的信息不同。

FRAM:抽象视图

CEL:完整的layout视图,包含使用层、大小、布局布线等所有信息,在流片时就从这个view抽取stream或者GDSII数据文件

LM(可选):逻辑模型视图

目录结构如下图:

注:虽然.mw文件当中包含逻辑库,但是ICC仍然需要单独指定target_library/link_library到.db文件上,如果.db文件就在mw当中,那么search_path应当指向mw中的LM视图所在的目录。

1.Specify the Logical Libraries

在.synopsys_dc.setup中输入以下命令,指定接下来要生成的ICC文件的逻辑库:

lappend search_path [glob ./libs/*/LM]

set_app_var target_library "sc_max.db"

set_app_var link_library \

" * sc_max.db io_max.db macros_max.db"

set_min_library sc_max. db -min_version sc_min. db

set_min_library io_max.db -min_version io_min.db

set_min_library macros_max. db -min_version macros_min. db

set app var symbol_library "sc.sdb io.sdb macros. sdb"

[link library]:

link library用来解析(resolve)网络列表中的所有实例化组件。如果ICC为网表中实例化的每个叶单元找到了相应的library cell(在任何指定的link_library文件中),或者为网表中的每个子设计在ICC内存中找到了相应的设计(也就是*),网表就会被解析,这种“解析”发生在link步骤中。

[target library]:

target library通常只指定具有基本逻辑门的库(标准单元,而不是IO pad或macro)。在逻辑优化期间,当单元大小和逻辑关系变化时,IC编译器以该库为目标(target)。link library和target libray通常与DC综合所用的库相同。

[其它命令]:

set_min_library命令用于定义“fast comer”库,该库将与其对应的“slow corner”库一起使用。在默认的“best-case worst-case”模式下,“max”库(target/link library)用于setup time分析,而"min"库(set_min_library)用于hold time分析。

search_path变量是缩短文件路径的方便方法。指定文件名后,ICC会在指定的搜索路径目录列表中查找该文件。

symbol library仅在GUI中提供查看原理图时使用的图标。

注意:最后一个启动的才是实际使用的配置

2. Create a “Container”: The Design Library

创建一个design lib(设计库)并制定该设计库的tech file和reference lib(也就是mw库)

create_mw_lib design_lib_orca -open\ #design lib的名字

-technology ./libs/abc_6m.tf\ #制定tech file

-mw_reference_library\ #制定mw库

"./libs/sc .libs/macros ./libs/io"

[design lib]

也是基于Milkyway的数据库结构,由用户创建,最终将包含布局、CTS、布线等所需的所有相关输入数据,以及physical"design cell"或版图。

数据设置的第一步是创建design lib,这需要为库提供一个用户定义的名称,并指定tech file以及physical ref lib(标准单元、macro和IOpad cell)。tech file实际上是被加载或读取到design lib中,但ref lib是被设计库创建的指针“引用”。

注:tech file和ref lib的路径必须是绝对路径,不能够使用search_path变量,如果路径或者名字变更,则使用下列命令更新。

set_mw_lib_reference \

-mw_reference_library

mw结构的design lib如下所示:

可以理解为create_mw_lib是创建了一个表格,每指定一个变量或者ref lib,就相当于是在表格里面填一项内容。

3a. Read the Netlist and Create a Design CEL

用以下命令读入网表并创建CEL view:

read_verilog ./netlist/orca.v

current_design ORCA

uniquify

save_mw_cel -as ORCA

read_verilog:

ICC也可以用read_ddc读入ddc文件,或者读入多个文件。

current_design:

读入的文件可能含有多个分模块,因此需要该命令来确定用户现在操作哪一部分

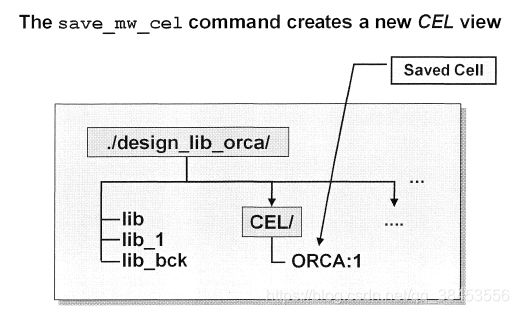

save_mw_cel:

用于创建初始的mw design cell(视图名称CEL)。在设计规划和布局之前,CEL视图由黄色矩形组成,这些矩形表示所有网表单元(标准单元、macro单元和IO pad),它们都在原点处相互叠置。在设计规划、布局、CTS、布线等步骤后设计单元物理信息会产生巨大的改变。

该命令还将用CEL保存逻辑(db)库和TLU+模型信息。但是默认情况下,一旦CEL关闭后重新打开,ICC不会唤醒此信息。

uniquify:

使每个模块独立开来,从而在后续步骤中每个模块都能根据自身情况单独优化。

3b.Shortcut: Import the Netlist

也可以用以下命令快速导入设计:

import_designs ./netlist/orca.v

-format verilog \

-top ORCA

默认情况下该设计会以顶层模块的名字存储到CEL view下面,如果想要重命名,可以启用-cel

[.tf文件]

■ The technology file is unique to each technology

每个工艺的.tf文件都有一定的差异

■ Contains metal layer technology parameters:

文件包含金属层的参数,包括每一层的名字、物理电学性能、设计规则、单位、在版图界面中呈现的颜色等等。

• Number and name designations for each layer/via

• Physical and electrical characteristics of each layer/via

• Design rules for each layer/Via (Minimum wire widths

and wire-to-wire spacing, etc.)

• Units and precision for electrical units

• Colors and patterns of layers for display

.tf文件的内容如下:

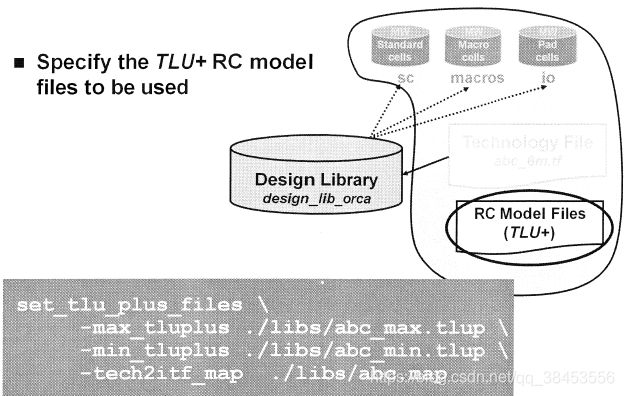

4. Specify TLU+ Parasitic RC Model Files

用以下命令指定设置RC寄生参数的TLU+文件:

set_tlu_plus_files \

-max_tluplus ./libs/abc_max.tlup \

-min_tluplus ./libs/abc_min.tlup \

-tech2itf_map ./libs/abc.map

注:search_path适用于该命令,因此如果文件处在search_path下,可以省略前面的路径。

延时的计算方法

ICC会计算所有单元和网络的延时,为此需要每个路径的寄生参数。延迟取决于输入转换时间,驱动强度(也就是输入电阻),线电容以及端电容。.db文件中已经包含延迟和其影响因素之间的对应表,TLU+文件的作用就在于表上的定位,如下图:

有些开发商只提供ITF文件(Interconnect Technology Format),需要使用StarRC来将ITF文件转化为TLU+

5.Check the Libraries/Verify Logical Libraries Are Loaded

用以下命令检查1-4步里面设置的库有没有被正确导入:

set_check_library_options -all

check_library

check_tlu_plus_files

list_libs

首先检查库之间是否匹配,例如:

• Between logic (link_library) and physical libraries:

♦ Missing cells

♦ Missing or mismatched pins

• Within physical libraries:

♦ Missing CEL (layout) or FRAM (abstract) view cells

♦ Duplicate cell name in multiple reference libraries

然后用list_libs检查所有的逻辑库都已经被加载,该命令应当在设计都被link以后执行。

6. Define Logical Power/Ground Connections

用以下命令定义P/G网络的名字并在P/G pin和P/G net之间建立逻辑关系,同时在tie-high/low输入和P/G net之间建立逻辑关系。

derive_pg_connection -power_net PWR -power_pin VDD \

-ground_net GND -ground_pin VSS

derive_pg_connection -power_net PWR -ground_net GND \

-tie

check_mv_design -power_nets

- During data setup, before any initial physical routing of power/ground nets, e.g. before

create_pad_rings, commit_fp_rail, preroute_instances or

preroute_standard_cells - Before inserting filler cells with metal, or before running verify_lvs: Good practice to apply

after routing. - Before writing out the final Verilog netlist

以上只针对单电源供电的部分,多电源供电的约束和命令更加复杂,需要参考其它的教程。

7. Apply and Check Timing Constraints

用以下命令检查时序约束:

read_sdc ./cons/orca.sdc

check_timing

report_timing_requirements

report_disable_timing

report_case_analysis

如果导入的是verilog文件就需要额外读入.sdc文件,如果导入的是.ddc文件则可以跳过.sdc文件的读入,无论是否需要额外读入,最好都用check_timing检查保证时序约束是完整的。

report_timing_requirements:

检查设计是否包含任何错误或多周期路径,或任何异步最小或最大延迟约束。

report_disable_timing:

报告当前设计中禁用的时序弧,包含一个或多个禁用计时弧的路径将不会被优化。

report_case_analysis:

报告通过约束set_case_analysis设置为常量逻辑1或0的端口或pin。

8.Ensure Proper Modeling of Clock Tree

用以下命令保证SDC约束对所有时钟的skew、latency和transition进行建模:

report_clock -skew

report_clock

关于uncertainty,delay,transition的定义不再赘述,可以参考静态时序分析部分的描述。

propagated clock会强制ICC计算通过时钟网络的【实际】传播延迟,以找到实际的skew、latency和transition。这在CTS完成之后很有用。

9. Apply Timing and Optimization Controls

ICC中有大量的命令可以设置电路的时序约束和优化,例如:

set_app_var timing_enable_nvultipl©_clocks_per_reg true

set_fix_rtiultiple_port_nets -all -buffer_constants

group_path -name INPUTS -from [all_inputs]

这些命令应当在最开始通过tcl脚本导入,然后再进行design planning,placement,CTS和routing。

具体的约束可以通过GUI界面、man命令等查看,然后根据需要添加。

注:每启动一次ICC就要重新导入一次该脚本。

10.Perform a ‘Timing Sanity Check’

在布局之前保证设计在第9步没有设置多余的约束,约束应该和设计相匹配。

•检查不现实或不正确的约束

•检查大型零互连(zero-interconnect)时序违规

具体的命令如下所示:

set_zero_interconnect_delay_mode true

report_constraint -all

report_timing

set_zero_interconnect_delay_mode false

这个部分用于检查较严重的时序违例,例如延迟和时钟周期达到了同一个量级,此时这个时序违例无法由ICC优化解决,需要返回上一级修改。

11. Remove Unwanted “Ideal Net/Networks”

本来这些sdc约束是用来防止DC等综合软件在特殊信号路径(高扇出的信号例如set/reset,enable,select等)上生长buffer树,现在需要移除这些约束来允许ICC设置buffer。

remove_ideal_network [get_ports "Enable Select Reset"]

Save the Design

每个关键步骤后都用以下命令保存设计:

save_my_cel -as ORCA_data_setup

保存后的文件结构如下图所示:

保存文件后,当前打开的文件仍然是ORCA,和保存的ORCA_data_setup不是同一文件。

注:在删除更改CEL文件时不要使用rm/cp命令,会使.mw下的库设置产生混乱,要改用rename_mw_cel,remove_mw_cel这些ICC专用的命令。

但是用cp/rm来操作整个.mw文件是可行的。

退出重启ICC后,导入已存在的mw文件用如下命令:

icc_shell -gui

open_mw_lib design_lib_orca

open_mw_cel ORCA_setup

source tim_opt_ctrl.tcl #不要忘记如果继续使用第9步的约束,需要重新载入脚本。

参考脚本

[.synopsys_dc.setup]

对应第1步

lappend search_path [glob ./libs/*/LM]

set_app_var target_library "sc_max.db"

set_app_var link_library \

" * sc_max.db io_max.db macros_max.db"

set_min_library sc_max.db -min_version sc_min.db

set_min_library io_max.db -min_version io_min.db

set_min_library macros_max.db -min_version macros_min.db

set_app_var symbol_library "sc.sdb io.sdb macros.sdb"

[tim_opt_ctrl.tcl]

对应第9步

set_app_var timing_enable_multiple_clocks_per_reg true

set_app_var case_analysis_with_logic_constants true

set_fix_multiple_port_nets -all -buffer_constants

set_auto_disable_drc_nets -constant false

set_dont_use

set_prefer —min

set_app_var physopt_delete_unloaded_cells false

set_ideal_network [all_fanout -flat -clock_tree]

set_cost_priority {max_transition max_delay}

set_app_var enable_recovery_removal_arcs true

set_max_area 0

set_app_var physopt_power_critical_range

set_app_var physopt_area critical range