计算机组成原理习题-2

前言

本文通过记录几道题目,回顾和总结I/O数据传输等计算机组成原理相关知识。内容涵盖闪速存储器、总线传输过程、CPU响应中断、存储保护等问题的解析,以及关于Cache、指令格式、微程序等的计算机系统设计案例,答案来自网络搜集和ChatGPT,可能不完全正确

一、回答下列问题

1.何为"总线仲裁"?他有几种方式?集中式总线仲裁方式有哪些?各有哪些特点?

总线仲裁(Bus Arbitration)是指多个设备同时请求使用总线进行数据传输时,需要通过某种机制来协调、决定哪个设备可以优先访问总线进行数据传输。

总线仲裁的方式有两种:集中式和分布式。

集中式总线仲裁方式是指有一个专门的仲裁器或者控制器来负责协调总线的访问权限。常见的集中式总线仲裁方式有以下几种:

集中式仲裁使用优先级编码:每个设备被分配一个唯一的优先级编码,仲裁器按照设备的优先级确定总线的访问顺序。设备的优先级可以是固定的,也可以根据设备的特定要求进行设置。

集中式仲裁使用轮询方式:仲裁器按照事先确定的轮询顺序循环地询问每个设备是否需要访问总线。每个设备在轮到它的时候可以请求总线进行数据传输。

集中式仲裁使用请求-确认方式:每个设备通过发送请求信号来请求总线进行数据传输,仲裁器接收到请求信号后发送确认信号给获得访问权的设备,同时阻止其他设备访问总线。获得访问权的设备可以进行数据传输,其他设备则需要等待下一轮的请求。

每种集中式总线仲裁方式都有各自的特点和适用场景。优先级编码适用于设备间有一定的优先级关系,并且优先级需要固定或者可变的情况。轮询方式适用于所有设备的优先级相同,并且希望每个设备都有机会访问总线的情况。请求-确认方式在一定程度上可以提高总线的利用率,但会增加仲裁器的复杂性。

2.cache技术的基本思想和出发点是什么?Cache系统由哪几个主要部分组成?

Cache是一种高速缓冲存储器,是为了解决CUP和主存之间速度不匹配问题而采用的一项重要技术。Cache技术的出发点就是用SRAM和DRAM构成一个组合的存储系统,使它兼有SRAM和DRAM的优点。采用这样的技术,在主存和高速CPU之间设置一个小容量的高速存储器(通常为32KB的SRAM),其中存放的CPU常用的指令和数据,于是,CPU对存储器的访问主要体现在对SRAM的存取,因此可以不必加等待状态而保持高速操作。

一个cache系统包含3个方面的内容:

3.中断控制方式和DMA方式有什么异同之处?

DMA速度快。响应快、优先级高、处理快、无须现场保护和现场的恢复。但是应用范围没有程序中断控制方式广。

4.简述变址寻址,基址寻址的原理,区别和二者不同之处。

变址寻址和基址寻址是两种常见的寻址方式,它们的原理、区别和不同之处如下:

变址寻址的原理: 变址寻址是通过将一个基地址与一个偏移量相加来定位内存中的数据或指令。偏移量可以是一个常数,也可以是存储在寄存器中的值。通过将基地址与偏移量相加,可以得到需要访问的内存地址。

基址寻址的原理: 基址寻址是通过将一个基地址直接与指令中的地址字段相加来定位内存中的数据或指令。基址通常是事先确定的,在程序执行过程中不会修改。指令中的地址字段包含与基址相加得到的偏移量。

区别:

原理不同:变址寻址是将基地址与偏移量相加,而基址寻址是将基地址与指令中的地址字段相加。

灵活性不同:变址寻址更加灵活,可以使用常数或寄存器中的值作为偏移量;而基址寻址只能使用指令中的地址字段作为偏移量。

修改性不同:变址寻址中的偏移量可以根据需要进行修改;而基址寻址中的基址是固定的,在程序执行过程中不会修改。

二者不同之处:

变址寻址可灵活地改变偏移量,适用于需要根据条件或循环来访问不同地址的情况。而基址寻址适用于代码或数据存放在连续内存区域中的情况。

变址寻址通常用于数组或结构体的访问,可以通过指针或索引来定位数据。而基址寻址通常用于子程序或函数的调用,可以通过指令中的地址字段直接定位函数的入口地址。

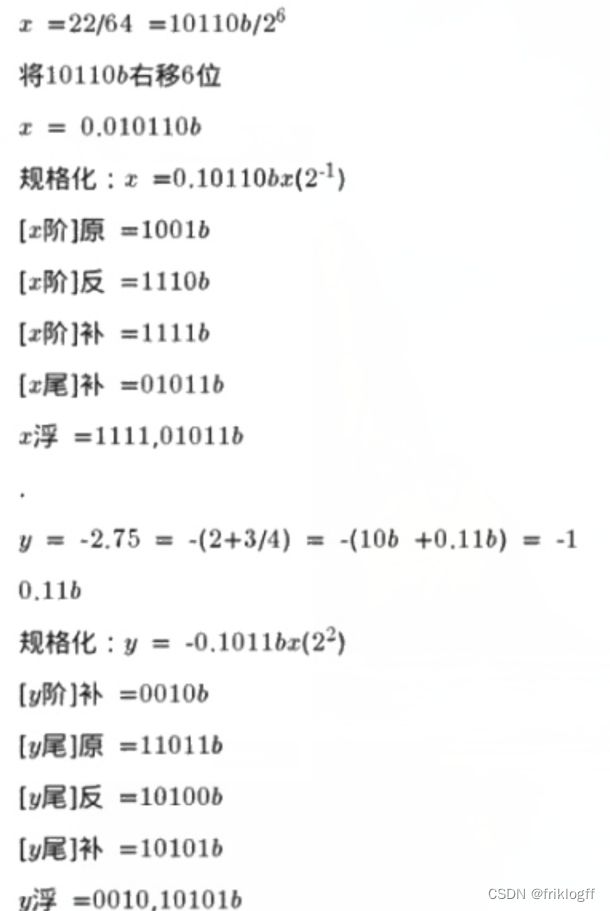

二、设浮点数的格式为∶阶码4位,包含一位符号位,尾数5位,包含一位符号位,阶码和尾数均用补码表示,则

1、若r=22/64,y=-2.75,求z和g的规格化浮点数表示形式(所给z,g均为10进制)

2、( z+y)浮(要求用补码计算)问题

答案

三、一片EDRAM的存储容量为2M×4位,其中sel为片选信号,RA为行选通信号,CAS为列选通信号,Ref为刷新信号。A0-A10为地址输入信号。请设计一个2M×32位的存储器,其存储容量是多少?画出组成模块图。

答

要设计一个2M×32位的存储器,可以使用8片2M×4位的EDRAM芯片来实现。每个EDRAM芯片可以存储4位数据,需要将32位数据拆分为8个4位的部分,分别存储在8片EDRAM芯片中。

存储器的存储容量计算为:

存储容量 = 芯片数 × 每片芯片容量 = 8片 × 2M×4位 = 8 × 2M 字(1字 = 4字节,1M = 1024K)

存储容量 = 8 × 2M × 4字节 = 8 × 2 × 1024K × 4字节 = 16,384K × 4字节 = 65,536KB

存储容量为65,536KB,即64MB。

组成模块图如下所示:

+------+ +---+

A0 ---| | | |

A1 ---| | | |

... | EDRAM| Sel | |

A10---| |------| |

| | RA | | +--------------+

Data---| | CAS | |---| |

... | |------| | | |

Data---| | | | | Memory |

Data---| | Ref | | | |

Data---| | | | | |

+------+ +---+ +--------------+

在组成模块图中,共有8片EDRAM芯片,每片芯片有4位数据存储。地址信号A0到A10用于选择存储器中的行和列,Sel信号用于片选,RA信号用于行选通,CAS信号用于列选通,Ref信号用于刷新。Data是输入/输出的32位数据。存储器是由8片EDRAM芯片组成的32位存储器。每次写入/读取数据时,需要将32位数据拆分成8个4位的部分,分别写入/读取到每片EDRAM芯片中。

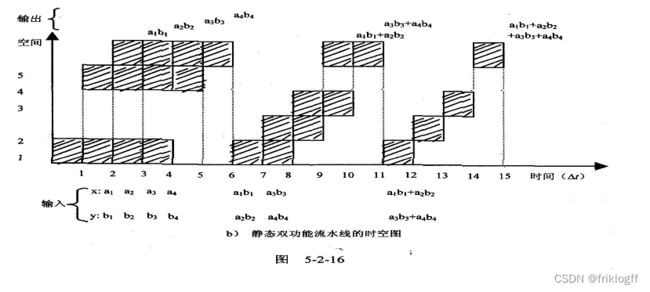

四、如果采用如图所示的双输入端的加一乘双功能静态流水线,其每个功能段的经过时间均为一个节拍Δt,在加法是按1->2->3->5连接,乘法时按1->4->5连接。流水线的输出可以直接通到其输入端或存入缓冲器不计期间的传输延迟,操作数可继续提供。 对向量),),流水线完成点积,求完成该计算所需要的最少节拍数是多少?并画出此时的流水线时空图,并计算出流水线的吞吐量,加速比和效率。

答案

解:首先,应选择适合于静态流水线工作的算法。对于本题,应先连续计算a1b1、a2b2、a3b3和a4b4共4次乘法,然后功能切换,按((a1b1 a2b2) (a3b3 a4b4))经3次加法来求得最后的结果。按此算法可画出流水线工作时的时空图。

由图可见,总共在15个△t的时间内流出7个结果,所以在这段时间里,流水线的实际吞吐率TP为7/15△t。

若不用流水线,由于一次求积需3△t,产生上述结果就需要43△t 34△t=24△t。因此,加速比为S=24△t/(15△t)=1.6。

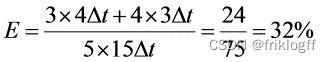

该流水线的效率可用阴影区面积和全部5个段的总时空图面积之比求得,即

总结

通过对上述问题的解析,加深了对计算机组成原理相关知识的理解,包括总线仲裁方式、Cache系统组成、中断控制与DMA、寻址方式、浮点数表示与运算、存储器设计、流水线计算等方面的知识。这为今后进一步学习计算机系统结构、体系结构、高级语言与系统接口等课程奠定了基础。希望本文能对读者有所裨益。