Quartus II:VHDL组合逻辑-时序逻辑练习

目录

- 一、在QuartusII 中用原理图输入法设计 4 位加法器

-

- 1.在之前的实验基础上设计4位全加器

- 2.仿真波形图

- 3.引脚绑定

- 4.硬件测试

- 二、应用QuartusII 完成基本组合电路设计

-

- (一)2选1多路选择器

-

- 1.新建VHDL 文件

- 2.仿真波形图

- (二)多路选择器

-

- 1.新建VHDL 文件

- 2.仿真波形图

- (三)引脚锁定以及硬件下载测试

-

- 1.2选1多路选择器

- 2.多路选择器

- 三、应用QuartusII 完成基本时序电路的设计

-

- (一)触发器设计

-

- 1.新建VHDL文件

- 2.仿真波形图

- (二)锁存器设计

-

- 1.新建VHDL文件

- 2.仿真波形图

- (三)引脚绑定以及硬件下载测试

-

- 1.触发器

-

- (1)引脚绑定

- (2)硬件测试

- 2.锁存器

-

- (1)引脚绑定

- (2)硬件测试

- 四、总结

- 参考资料

一、在QuartusII 中用原理图输入法设计 4 位加法器

(1) 实验目的:熟悉利用QuartusⅡ的原理图输入方法设计简单组合电路,掌握层 次化设计的方法,在实验一(1位加法器)的基础上,通过一个4位全加器的设 计,掌握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。

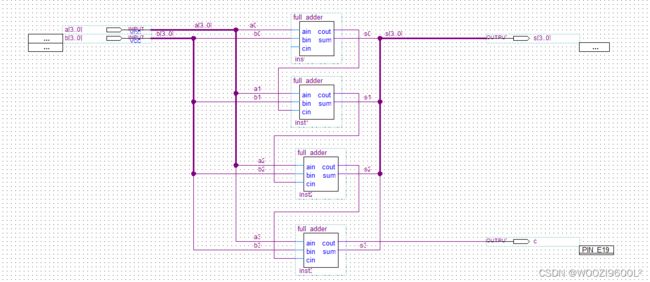

(2) 实验原理:一个4位全加器可以由4个1位全加器构成,加法器间的进位可以 串行方式实现,即将低位加法器的进位输出cout与相临的高位加法器的最低 进位输入信号cin相接(串行进位加法器)。

(3) 实验内容:建立一个更高层次的原理图设计,利用实验一获得的1位全加器 构成4位全加器,见图2.1。注意总线连接方式必须对连线命名,方法是单击 要命名的连线,出现光标后直接输入连线的名字,如总线a[3…0],或单线a0。 并完成编译、综合、适配、仿真和硬件测试。

1.在之前的实验基础上设计4位全加器

S=A+B+C1,

C1=‘1’(‘0001’)

S>15时进位C为1

实验一:Quartus II :1位全加器设计

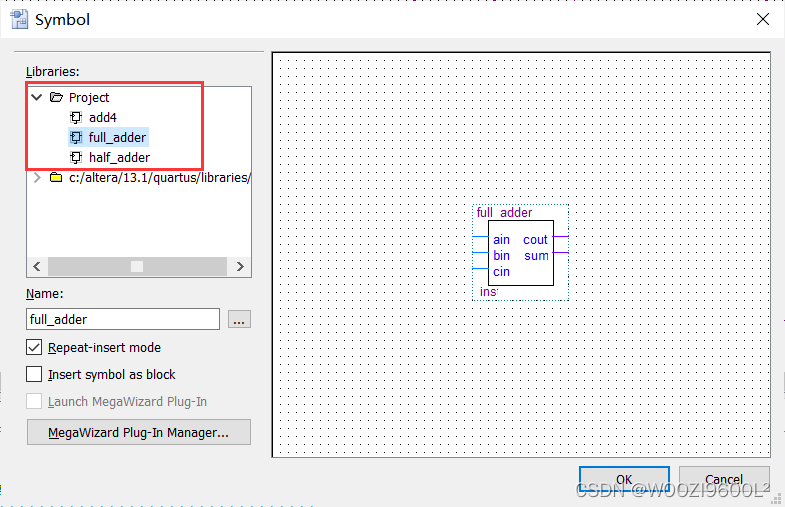

打开之前的项目,新建一个原理图文件,之前封装的1位全加器可以直接使用:

如果没有就代表没封装,点击之前的原理图文件,左上角选择file->Create/update->create symbol files for current file,保存.bsf文件即可。

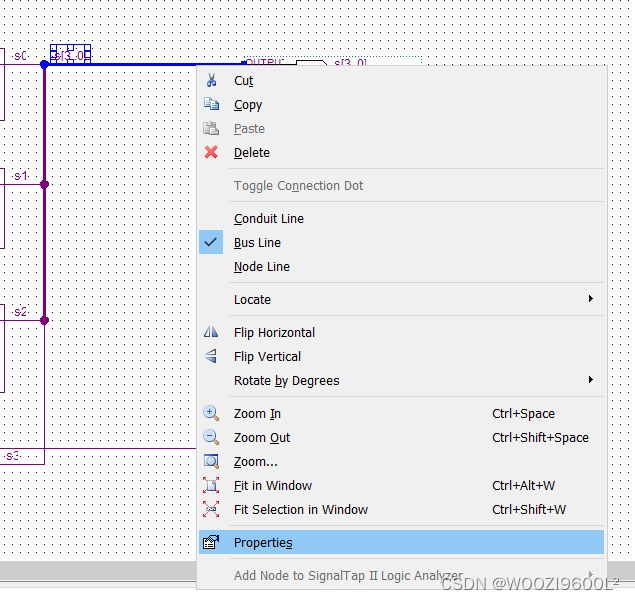

其中粗的是总线(Bus line),细的是单线(Node line),右键要命名的线,选择properties进行命名。

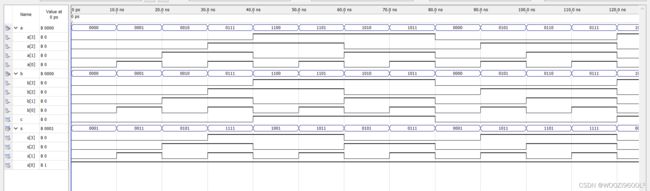

2.仿真波形图

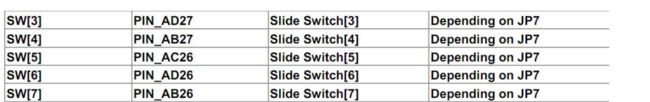

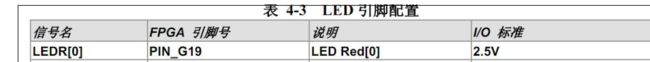

3.引脚绑定

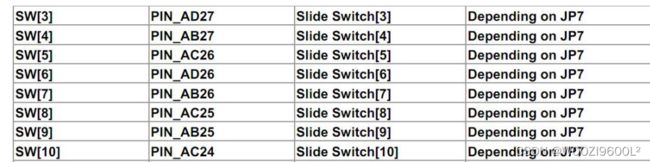

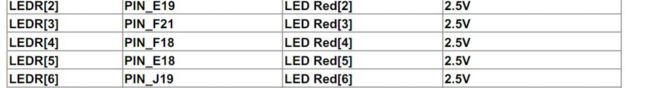

开发板上的18个拨码开关选其中8个,SW3,SW4…SW10分别接a[3…0]、b[3…0](开关向上拨和向下拨分别显示输入是高还是低电平);LED2,LED3,LED4,LED5,LED6分别接c和s[3…0],灯亮表示输出为“1”,灯灭表示输出为“0”。

硬件设计好后,还需要查引脚图(引脚图见附录)进行引脚绑定。

从 附 录 “ 表 4-1 拨 动 开 关 引 脚 配 置 ” 中 找 到 输 入 的 三 个 开 关

SW3,SW4,SW5…SW10,再找到对应的“FPGA引脚号”。如图:

选定了引脚之后原理图文件一定要再编译一次,才能真正把引脚绑定上。引脚绑定好并编译过的文件如图:

4.硬件测试

把开发板接上电源,USB 接口接电脑。打开电源开关(注意不用下载时请一定关闭开关,以免烧坏板子)。点击软件工具栏上的按钮

![]()

则出现下载界面。第一次下载需安装硬件。即在下载界面中点击按钮“hardware setup…”,然后在弹出的对话框中选择“USB blaster”,再点击“ok”,则硬件被安装上。

二、应用QuartusII 完成基本组合电路设计

(1) 实验目的:熟悉QuartusⅡ的VHDL文本设计流程全过程,学习简单组合电路 的设计、多层次电路设计、仿真和硬件测试。

(2) 实验内容1:首先利用QuartusⅡ完成2选1多路选择器(例3-1)的文本编辑输 入(mux21a.vhd)和仿真测试等步骤,给出图3.2所示的仿真波形。最后在实验系统 上进行硬件测试,验证本项设计的功能。(参见附录二)

(3) 实验内容2:将此多路选择器看成是一个元件mux21a,利用元件例化语句描 述图3.1(注意,不是使用图形输入法,是使用文本输入法输入。),并将此文 件放在同一目录中。对此顶层文件进行编译、综合、仿真。并对其仿真波形作出 分析说明。

(4) 实验内容3:引脚锁定以及硬件下载测试。自行进行硬件测试设计(如通过使 扬声器输出不同音调等)。

(一)2选1多路选择器

1.新建VHDL 文件

代码:

ENTITY mux21a IS

PORT ( a, b, s: IN BIT;

y : OUT BIT );

END ENTITY mux21a;

ARCHITECTURE one OF mux21a IS

BEGIN

y <= a WHEN S='0' ELSE b ;

END ARCHITECTURE one;

2.仿真波形图

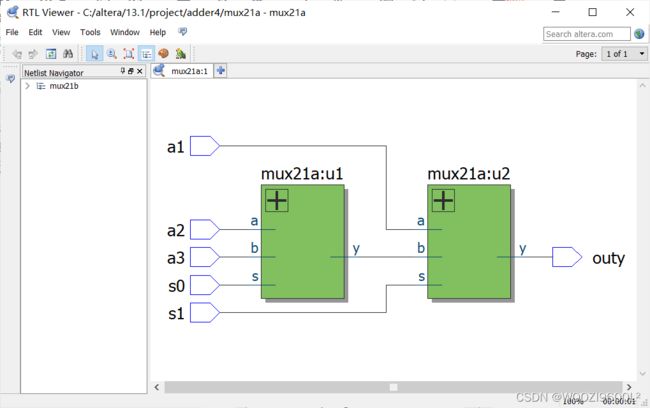

(二)多路选择器

1.新建VHDL 文件

代码:

entity mux21b is

port (a1,a2,a3,s0,s1:in bit;outy:out bit);

end entity mux21b;

architecture bhv of mux21b is

component mux21a

port (a,b,s:in bit;y:out bit);

end component;

signal tmp: bit;

begin

u1:mux21a port map(a=>a2,b=>a3,s=>s0,y=>tmp);

u2:mux21a port map(a=>a1,b=>tmp,s=>s1,y=>outy);

end architecture bhv;

2.仿真波形图

按照前面的2选1的方法,先在a2,a3中按s0的取值变化选出一个数(假设为b0),再从a1和b0中按s1的取值变化选出最后的数,输出为outy.

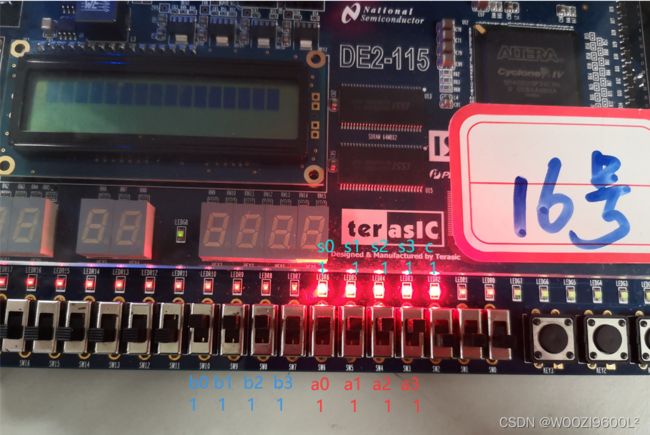

(三)引脚锁定以及硬件下载测试

1.2选1多路选择器

s=0,y取a值,y=a=0

s=1,y取b值,y=b=1

2.多路选择器

观测图:

s0=0,b0=a2=0;s1=0,outy=a1=0;

s0=0,b=0=a2=0;s1=0,outy=a1=1;

s0=1,b0=a3=1;s1=1,outy=a1=1

三、应用QuartusII 完成基本时序电路的设计

(1) 实验目的:熟悉QuartusⅡ的VHDL 文本设计过程,学习简单时序电路的 设计、仿真和测试。

(2) 实验内容1:根据附录二的步骤和要求,设计触发器(使用例4-1),给出程序 设计、软件编译、仿真分析、硬件测试及详细实验过程。

(3) 实验内容2:设计锁存器(使用例4-2),同样给出程序设计、软件编译、仿真 分析、硬件测试及详细实验过程。

(一)触发器设计

1.新建VHDL文件

代码编写:

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY DFF1 IS

PORT (CLK : IN STD_LOGIC ;

D : IN STD_LOGIC ;

Q : OUT STD_LOGIC );

END DFF1;

ARCHITECTURE bhv OF DFF1 IS

SIGNAL Q1 : STD_LOGIC ; --类似于在芯片内部定义一个数据的暂存节 点

BEGIN

PROCESS (CLK,Q1)

BEGIN

IF CLK'EVENT AND CLK = '1'

THEN Q1 <= D ;

END IF;

END PROCESS ;

Q <= Q1 ; --将内部的暂存数据向端口输出(双横线--是注释符号)

END bhv;

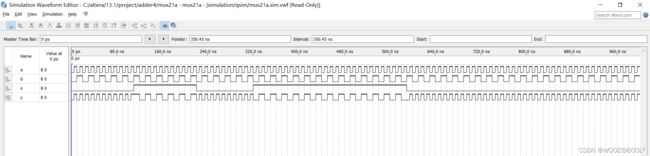

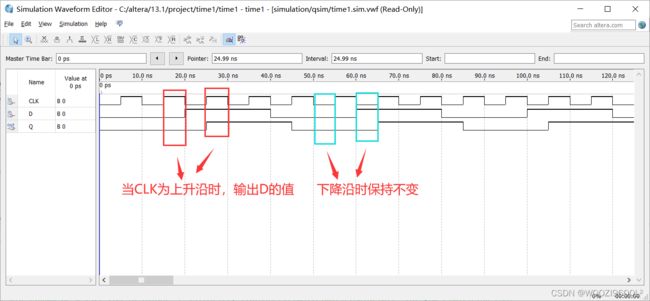

2.仿真波形图

输入一组波形,当且仅当CLK为上升沿的时候,Q输出D的值;否则,Q保持原值不变。

仿真图:

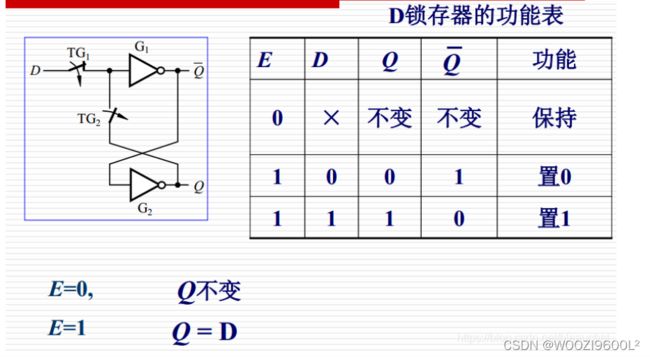

(二)锁存器设计

1.新建VHDL文件

代码编写:

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY DFF4 IS

PORT(CLK,D:IN STD_LOGIC;

Q:OUT STD_LOGIC);

END;

ARCHITECTURE bhv OF DFF4 IS

SIGNAL Q1:STD_LOGIC;

BEGIN

PROCESS(CLK,D) BEGIN

IF CLK='1'

THEN Q<=D;

END IF;

END PROCESS;

END;

2.仿真波形图

(三)引脚绑定以及硬件下载测试

1.触发器

(1)引脚绑定

(2)硬件测试

2.锁存器

(1)引脚绑定

(2)硬件测试

四、总结

4位全加器:在完成了1位全加器的设计后就比较容易了,只要将1位全加器封装好,直接使用4个1位全加器串行连接就比较容易了。

选择器:掌握VHDL语言的基本语法,知道选择器的逻辑后就比较好写代码了

触发器和锁存器:明确相关逻辑后进行代码编写,不会有太大的问题。

总的来说还是花费了不少的时间来完成这次的实验,由于部分器件的引脚过多,会有点儿记不清对应的位置,在验证时会有些混乱。

参考资料

锁存器、触发器和寄存器

https://max.book118.com/html/2021/0126/8117113143003042.shtm