ARM Cortex-A8体系结构

ARM Cortex-A8体系结构

- 一、ARM体系简介

-

-

- 1.1 ARM体系结构及其及其对应的内核

- 1.2、ARM处理器的主要产品

- 1.3、ARM开发工具

-

- 二、Cortex-A8处理器架构

- 三、Cortex-A8处理器的工作模式和工作状态

一、ARM体系简介

1.1 ARM体系结构及其及其对应的内核

| 体系结构 | ARM的内核版本 |

|---|---|

| v1 | ARM1 |

| v2 | ARM2 |

| v2 | ARM2aS、ARM3 |

| v3 | ARM6、ARM600、ARM7、ARM700、ARM710 |

| v4 | StrongARM、ARM8、ARM810 |

| v4 | ARM7TDMI、ARM720T、ARM740T、ARM9TDMI、ARM940T |

| v5 | ARM9E-S、ARM10TDMI、ARM1020E |

| v6 | ARM11、ARM1156T2-S、ARM1156T2F-S、ARM1176JZF-S、ARM11JZF-S |

| v7 | ARM Cortex-M、ARM Cortex-R、ARM Cortex-A |

| v8 | Cortex-A53/57、Cortex-A72 |

1.v4版本增加T变种,引入Thumb状态,处理器工作在该状态下时,指令集为新增的16位Thumb指令集

2.v6版本引入Jazelle技术,提高了Java性能,降低了Java应用程序对内存的空间占用;通过SIMD(单指令多数据流)技术,提高了音/视频处理能力。

3.v7版本

v7版本架构是在v6版本的基础上诞生的,对于早期的ARM处理器软件提供了较好的兼容性。它的主要特点有:

(1)采用了在Thumb代码压缩技术上发展的Thumb-2技术,比纯32位代码减少了31%的内存占用,减小了系统开销,能够提供比基于Thumb技术的解决方案高出38%的性能;

(2)首次采用NEON信号处理扩展集,它是一个结合64位和128位的SIMD指令集,对H.264和MP3等媒体解码提供加速,将DSP和媒体处理能力提高了近4倍,并支持改良的浮点运算;

(3)支持改良的运行环境,迎合不断增加的JIT(Just lnTime)和DAC(Dynamic Adaptive Compilation)技术的使用。

该架构定义了三大系列:

Cortex-A系列:面向基于虚拟内存的操作系统和用户应用,主要用于运行各种嵌入式操作系统(Linux、WindowsCE、Android、Symbian等)的消费娱乐和无线产品;(手机、多媒体等使用)

Cortex-M系列:主要面向微控制器领域,用于对成本和功耗敏感的终端设备,如智能仪器仪表、汽车和工业控制系统、家用电器、传感器、医疗器械等;

Cortex-R系列:该系列主要用于具有严格的实时响应限制的深层嵌入式实时系统。(硬实时,在军事上使用较多)

4.v8版本

2011年11月,ARM公司发布了新一代处理器架构ARMv8的部分技术细节,这是ARM公司的首款支持64位指令集的处理器架构,将被首先用于对扩展虚拟地址和64位数据处理技术有更高要求的产品领域,如企业应用、高档消费电子产品。目前的ARMv7架构的主要特性都将在ARMv8架构中得以保留或进一步拓展,如TrustZone技术、虚拟化技术及NEONadvanced SIMD技术等。ARMv8架构将64位架构支持引入ARM架构中,其中包括:

(1)64位通用寄存器、SP(堆栈指针)和PC(程序计数

器);

(2)64位数据处理和扩展的虚拟寻址;

(3)两种主要执行状态:AArch64(64位执行状态)和

AArch32(32位执行状态);

两种执行状态支持三个主要指令集:

A32(或ARM) :32位固定长度指令集,通过不同架构变体增强部分32位架构执行环境,现在称为AArch32;

T32 (Thumb):以16位固定长度指令集的形式引入的,随后在引入Thumb-2技术时增强为16位和32位混合长度指令集,部分32位架构执行环境现在称为AArch32。

A64:提供与ARM和Thumb指令集类似功能的32位固定长度指令集,随ARMv8一起引入,它是一种AArch64指令集。

1.2、ARM处理器的主要产品

1.2.1 ARM7系列

ARM7系列中的ARM7TDMI是应用最广泛的。

ARM7TDMI中的T代表Thumb架构扩展,提供两个独立的指令集,D代表内核具有Debug扩展结构,M代表EmbeddedICE逻辑,l代表增强乘法器,支持64位结果。

ARM7TDMI属于ARMv4体系结构,采用冯诺依曼结构(指令和数据在存储中统一存放,采用同一套总线分时传输),3级流水处理,平均0.9DMIPs/Mhz性能。

ARM7TDMI 没有MMU(Memory Management Unit)(不不支持分页)和Cache,所以仅支持那些不需要MMU和Cahce的小型实时操作系统,如VxWorks、uC/OS-Il和uLinux等RTOS。

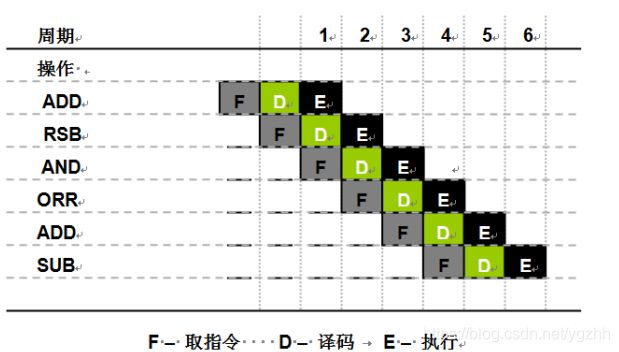

1.2.1.1 三级指令流水

理想三级流水线:

实际三级流水线:

流水线中出现的三个相关:

1、数据相关:是指令在流水bai线中du重叠执行时,当后继指令需要用到zhi前面的指令产生的结果dao时发生的。

2、控制相关:是当流水线遇到转移指令引起的。统计表明,转移指令约占总指令的四分之一左右,比起数据相关,它会使流水线丧失更多的功能。

3.结构相关:多条指令进入流水线后在同一机器周期内争用同一功能部件所发生的冲突。

使用五级指令流水的优点:

1.并行性更好

2.周期:机器周期可以设置地更短、时钟周期也更短、主频更高

1.2.2 ARM Cortex-A8系列

最快的处理器提供超过2000 DMIPS的性能(2.0DMIPS/MHzs使用每秒千万条指令数除以主频)

运行于1GHz频率(90nm or 65nm制造工艺)

功耗小于300mW

1.3、ARM开发工具

最常见的有MDK-ARM、RVDS、ARM DS5

1.MDK-ARM

RealView Microcontroller Development Kit(MDK)支持基于包括ARM7,ARM9,Cortex-M3微控制处理器等在内的众多处理器,MDK主要是为终端客户提供价格低廉,功能强大的开发工具。集成了 RealView 编译工具,Keil uVision开发环境。(物联网方面的嵌入式系统的开发和M系列多使用此开发环境)

2.RVDS

RVDS (RealView Development Suite)是ARM公司推出的专为SOC,FPGA以及ASIC用户开发复杂嵌入式应用程序或者和操作系统平台组件接口而设计的开发工具,被业界称为最好的ARM开发工具。RVDS支持器件设计,支持多核调试,支持基于所有ARM和Cortex系列CPU的程序开发。RVDS还可以和第三方软件进行很好的连接。

RVDS包含有四个模块:

( 1)IDE:RVDS中集成了Eclipse lDE,用于代码的编辑和管理。支持语句高亮和多颜色显示,以工程的方式管理代,支持第三方Eclipse功能插件。

(2)RVCT:RVCT是业界最优秀的编译器,支持全系列的ARM和XSCALE架构,支持汇编语言、C语言和C++语言。RVDS的编译器根据最新的ARM架构进行特别的优化,针对每个ARM架构都提供最好的代码执行性能,最优的代码密度。可以根据需要选择调试信息级别,以及不同的代码优化方向和优化级别。

(3)RVD:是RVDS中的调试软件,功能强大,支持Flash烧写和多核调试,支持多种调试手段,快速错误定位。

(4)RVISS:是指令集仿真器,支持外部设备虚拟,可以使软件开发和硬件开发同步进行,同时可以分析代码性能,加快软件开发速度。

3.ARMDS5

ARMDS5,也叫ARMDS-5,是一款支持开发所有ARM内核芯片的集成开发环境,也是一套针对ARM支持的linux和android平台的全面的端到端软件开发工具套件。ARMDS5提供具有跟踪、系统范围性能分析器、实时系统模拟器和编译器的应用程序和内核空间调试器。这些功能包含在定制的、功能强大且用户友好的基于Eclipse的IDE中。借助于该工具套件,可以很轻松地为ARM支持的系统开发和优化基于Linux的系统,缩短开发和测试周期,并且可帮助工程师创建资源利用效率高的软件。

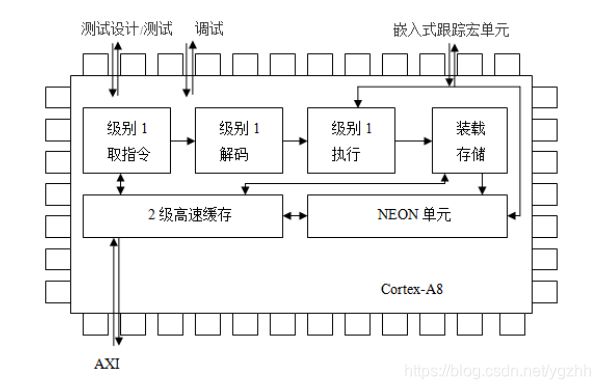

二、Cortex-A8处理器架构

Cortex-A8处理器是第一款基于ARMv7构架的的应用处理器,使用了能够带来更高性能、更低功耗和更高代码密度的humb-2技术,新增了130条指令。新增的功能使用户在进行终端服务时无需在ARM和Thumb模式间进行切换,同时可访问整套处理器寄存器。产生的代码保持Thumb指令的传统代码密度,却可以实现32位ARM代码的性能。

ARM处理器中首次采用面向音频、视频和3D图形的NEON媒体和信号处理技术。这是一个64/128位混合SIMD架构。通过使用NEON技术执行典型的多媒体功能,Cortex-A8处理器可在275MHz以30帧/秒的速度解码MPEG-4 VGA视频(包括去环状块、解块过滤和YUV至RGB的变换)并以350MHz解码H.264视频。

Cortex-A8还采用了Jazelle-RCTJava加速技术,可以支持Java程序的预编译与实时编译,对实时(JIT)和动态调整编译(DAC)提供最优化,将即时(JIT)字节码应用程序的内存占用削减到原先的三分之一。代码变少可增强性能并降低功率。

Cortex-A8中采用的TrustZone技术可确保消费类产品(如运行开放式操作系统的移动电话、个人数字助理和机顶盒)中的数据隐私和DRM得到保护。

1.指令读取单元(Instruction Fetch)

指令读取单元的主要构成如下图所示,指令读取单元对指令流进行预测,从L1指令缓存中取出指令放到译码流水线中。在此过程中使用到了TLB(Translation Lookaside Buffers,转换旁路缓冲器)。

2、指令译码(解码)单元(Instruction Decode)

指令译码单元对所有的ARM、Thumb-2指令进行译码排序,包括调试控制协处理器CP14的指令、系统控制协处理器CP15的指令。指令译码单元处理指令的顺序是:异常、调试事件、复位初始化、存储器内嵌自测CMI3IST、等待中断、其它事件。

3.指令执行单元(Instruction Execute)

指令执行单元包括两个对称的ALU(算术逻辑单元)流水线(ALU0和ALU1),它们都可以处理大多数算术指令。ALU0始终执行一对旧的发射指令。Cortex-A8处理器还配备乘法器和加载存储流水线,但这些都不对两条ALU流水线执行额外指令,可将它们视为“独立”流水线。使用它们必需同时使用两条ALU流水线中的一个,乘法器流水线只能与ALU1流水线中的指令结合使用,而加载存储流水线只能与任一ALU中的指令结合使用。

指令执行单元的功能:

- 执行所有整数ALU运算和乘法运算,并修改标志位;

- 根据要求产生用于存取的虚拟地址以及基本回写值;

- 将要存放的数据格式化,并将数据和标志向前发送;

- 处理分支及其它指令流变化,并评估指令条件码。

4.数据存取单元(Load/Store)

数据存取单元包括全部的L1数据缓存部分和整数存取流

水线,流水线可在每个周期接收一次数据存或取,可以

是在流水线0或流水线1上。

数据存取单元由以下几个部分组成:

- L1数据缓存;

- 数据TLB;

- 整数存储缓存;

- NEON存储缓存;

- 取整数数据对齐、格式化单元;

- 存整数数据对齐、格式化单元。

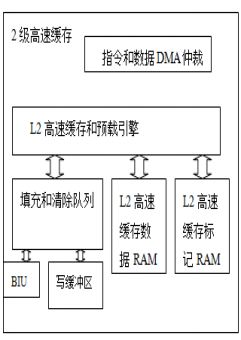

5.L2缓存单元(L2 Cache)

Cortex-A8处理器的L2缓存单元大小可配置为从64k到2M,包括L2 Cache和缓冲接口单元BU。

L1数据缓存的内容与L2缓存不兼容,L1指令缓存的内容是L2缓存的子集,当指令预取单元和数据存取单元在L1 Cache中未命中时,L2 Cache将为它们提供服务。L2缓存与L1缓存之间采用低延迟、高带宽专用接口,这将L1缓存行填充的延迟时间降至最低,并且与主系统总线不会产生流量冲突。

6.NEON媒体处理引擎

ARM NEON技术是适用于ARM Cortex-A系列处理器的一种SIMD(Single Instruction,Multiple Data,单指令、多数据)扩展结构。

Cortex-A8处理器的NEON媒体处理引擎包括一个10段流水线以及高级SIMD多媒体指令集。

NEON媒体处理引擎主要由以下几个部分组成:

- NEON指令队列;

- NEON数据队列;

- NEON译码逻辑的两个流水线;

- 三条用于SIMD整数指令的执行流水线;

- 两条用于SIMD的单精度浮点流水线;

- 一条加载存储/交换流水线;

- 一个非流水线向量浮点单元(VFPLite),执行VFPv3数据处理指令。

7.ETM单元(嵌入式跟踪宏单元)

ETM单元是一个非侵入跟踪宏单元,对嵌入式处理器内核提供了实时跟踪能力。它向一个跟踪端口输出处理器执行的信息。在系统调试和系统性能分析时,可以对指令和数据进行跟踪,并能对跟踪信息进行过滤和压缩。

ETM单元直接连接到ARM处理器内核,通过一个称为ATB(高级跟踪总线)的外部接口与处理器外部连接。

8.外部接口

Cortex-A8有丰富的外部接口。主要有:

AMBA AXI总线接口:一种面向高性能、高带宽、低延迟的片内总线。AXI总线接口是可配置的64位或128位AMBA高速总线接口,用于执行L2 Cache的填充和L1Cache指令及数据的访问。

AMBA APB接口:Cortex-A8处理器通过一个APB接口来访问ETM、CTI和调试寄存器。APB接口与CoreSight调试体系结构(ARM多处理器跟踪调试体系)兼容。

AMBA ATB接口:Cortex-A8处理器通过一个ATB接口输出调试信息。ATB接口兼容CoreSight调试体系结构。

DFT(Design For Test)接口:DFT接口为生产时使用MBIST(内存内置自测试)和ATPG(自动测试模式生成)进行内核测试提供支持。

三、Cortex-A8处理器的工作模式和工作状态

1.工作模式

| 处理器模式 | 模式标识符 | 备注 |

|---|---|---|

| 用户模式(User) | usr | 正常程序执行模式 |

| 系统模式(System) | sys | 使用和用户模式相同的寄存器组,用于特权级操作系统任务 |

| 管理模式(Supervisor) | svc | 系统复位或软件中断时进入该模式,是供操作系统使用的一种保护模式 |

| 外部中断模式(IRQ) | irq | 低优先级中断发生时进入该模式,常用语普通的外部中断处理 |

| 快速中断处理(FIQ) | fiq | 高优先级中断发生时进入该模式,用于高速数据传输和通道处理 |

| 数据访问终止模式(Abort) | abt | 当存取异常时进入该模式,用于虚拟存储和数据保护 |

| 未定义指令终止模式(Undefied) | und | 当执行未定义指令时静如该模式,用于支持硬件协处理器的软件仿真 |

| 安全监控模式(Monitor) | mon | 可在安全模式和非安全模式下转换 |

除用户模式外,其他七种工作模式统称为非用户模式(特权模式)。

2.处理器状态

Cortex-A8处理器是32位处理器,可执行32位ARM指令集指令,同时兼容16位 Thumb-2指令集指令和数据类型。有3种工作状态,这些状态由**程序状态寄存器(CPSR)**的T位和J位控制与切换。

ARM状态:执行32位的字对齐的ARM指令集指令,T位和J位为0;

Thumb状态:执行16位或32位半字对齐的Thumb-2指令集指令,T位为1,J位为0;

ThumbEE状态:执行为动态产生目标而设计的16位或32位半字对齐的Thumb-2指令集的变体,T位和J位为1,也称为Jazelle RCT技术。

ARM指令必须在ARM状态下执行;Thumb指令也必须在Thumb状态下执行;

ARM处理器可以在两种状态下切换,只要遵循ATPCS调用规则,ARM子程序和Thumb子程序之间可以相互调用。

ARM状态和Thumb状态之间的切换并不影响处理器工作模式和寄存器组的内容。处理器复位后开始执行代码时,处于ARM状态。

处理器状态之间的切换:

(1)ARM状态和Thumb状态之间切换

执行BX和BLX指令时,将通用寄存器的中所存储的目标地址值复制到程序寄存器PC,该目标地址值的最低一位为1则切换到Thumb状态。如果处理器在Thumb状态时发生异常(异常处理必须在ARM状态下),当异常处理返回时自动切换到Thumb状态。

执行BX和BLX指令时,将通用寄存器的中所存储的目标地址值复制到程序寄存器PC,该目标地址值的最低一位为0则切换到ARM状态。

处理器进行异常处理时,把PC的值放入异常模式链接寄存器中,从异常向量地址开始执行程序,系统自动进入ARM状态。

(2)Thumb状态和ThumbEE状态之间切换

使用ENTERX指令和LEAVEX指令。