【原创】DE2 实验练习解答—lab 3:锁存器、触发器和寄存器(digital Logic)(DE2)(quartus II)

本练习的目的是研究锁存器、触发器和寄存器。

Part I RS锁存器

Altera的FPGA含有可供用户使用的触发器电路。在Part IV演示如何使用它。这里探讨如何不使用专用触发器来创建存储单元。

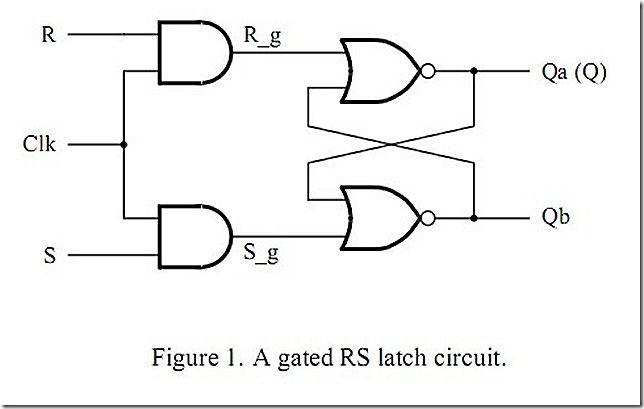

图1描述了门控锁存器电路。可用门级电路或表达式来描述。

part1.v //rs锁存器门级描述

2 module rs_ff(q,r,s,clk);

3 input clk,r,s;

4 output q;

5

6 wire r_g,s_g,qa,qb /* synthesis keep */ ;

7

8 and (r_g,r,clk);

9 and (s_g,s,clk);

10 nor (qa,r_g,qb);

11 nor (qb,s_g,qa);

12

13 assign q = qa;

14

15 endmodule

16

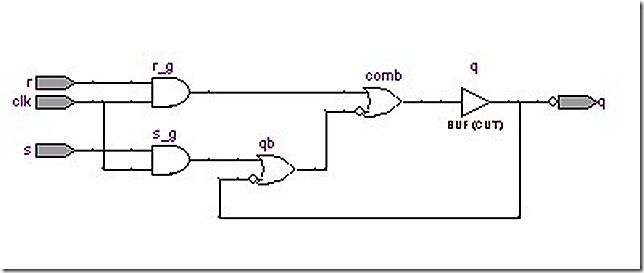

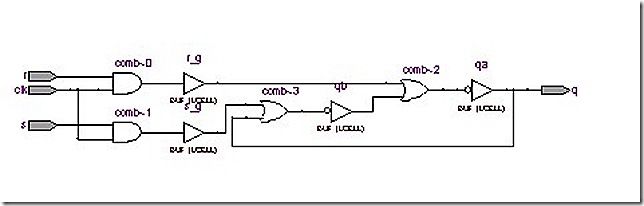

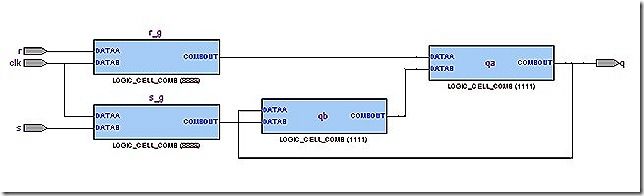

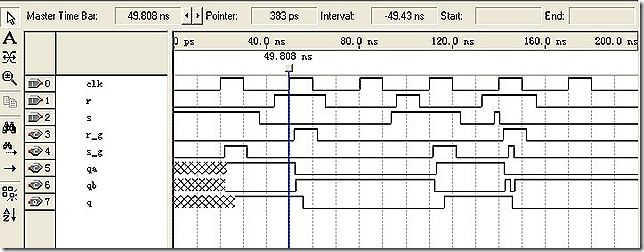

其中/*synthesis keep*/是编译指令,用来指定每个信号用一个单独的逻辑单元实现。RTL Viewer查看结果如下:

图2 未加编译指令的RTL图

图3 图2的内部结构

图5 图4的内部结构

图4 加上编译指令的RTL图

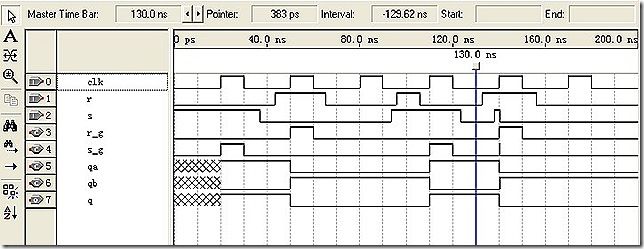

图6 RS锁存器功能仿真结果

图7 RS锁存器时序仿真结果

Part II 门控D锁存器

如图8所示:

图8 门控D锁存器

- 新建一个工程。为门控D锁存器创建类似Part I中的代码,分析。

part2.v 门控锁存器

2 module top_level(SW,LEDR0);

3 input [ 1 : 0 ]SW; // clk & d

4 output LEDR0; // q

5

6 gated_d_latch(LEDR0,SW[ 0 ],SW[ 1 ]);

7

8 endmodule

9

10

2 module gated_d_latch(q,d,clk);

3 input d,clk;

4 output q;

5

6 wire r,s_g,r_g,qa,qb /* synthesis keep */ ;

7

8 nand (s_g,d,clk);

9 nand (r_g,r,clk);

10 not (r,d);

11 nand (qa,s_g,qb);

12 nand (qb,r_g,qa);

13

14 assign q = qa;

15

16 endmodule

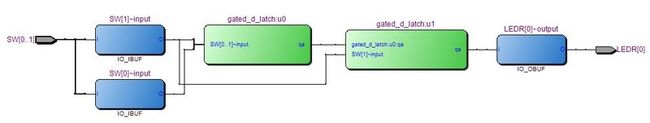

逻辑单元映射结果:

图9 Technology Map Viewer结果

仿真:

图10 功能仿真结果

图11 时序仿真结果

2. 另建一个工程,新建一个顶层文件,定义相应的输入/出引脚,使用D锁存器,在DE2上验证。

指定引脚:

| SW0 | d |

| SW1 | clk |

| LEDR0 | q |

小结:锁存器是电平敏感型电路,D锁存器的优点在于不可能出现S=R=1这个麻烦状态。

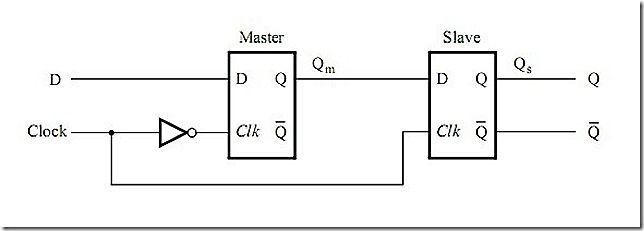

Part III 主从D触发器

图12 主从D触发器

part3.v 主从D触发器

2 module ms_dff(SW,LEDR0); // Qm);

3 input [ 1 : 0 ]SW;

4 output LEDR0;

5 // output Qm;

6

7 wire qm,qs;

8

9 gated_d_latch um(qm,SW[ 0 ],SW[ 1 ]);

10 gated_d_latch us(qs,qm, ~ SW[ 1 ]);

11

12 assign LEDR0 = qs;

13 // assign Qm=qm;

14

15 endmodule

仿真:

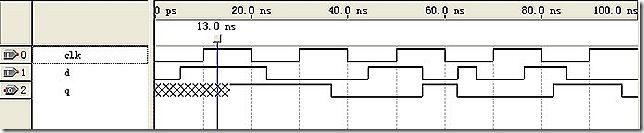

图13 主从D触发器功能仿真结果

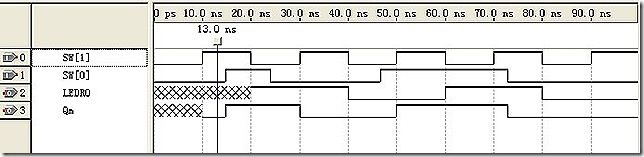

Part IV 三种存储单元

电平敏感存储元件与跳变沿触发的存储元件之间的比较。

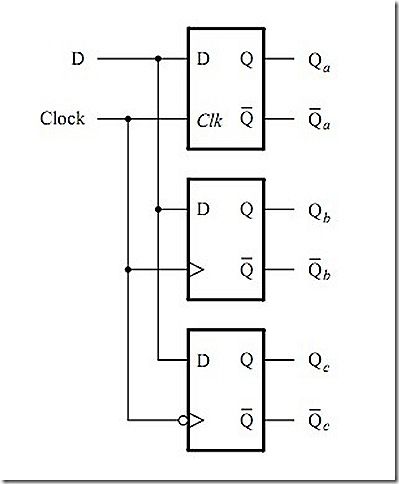

图14 三种存储元件

part4.v 代码

2 module su_3(d,clk,qa,qb,qc);

3 input d,clk;

4 output qa,qb,qc;

5

6 d_latch ul(d,clk,qa);

7 dff_p udp(d,clk,qb);

8 dff_n udn(d,clk,qc);

9

10 endmodule

11

12 // dff_p

13 module dff_p(d,clk,q);

14 input d,clk;

15 output q;

16

17 wire qm,qs;

18

19 d_latch um(d, ~ clk,qm);

20 d_latch us(qm,clk,qs);

21

22 assign q = qs;

23

24 endmodule

25

26 // dff_n

27 module dff_n(d,clk,q);

28 input d,clk;

29 output q;

30

31 wire qm,qs;

32

33 d_latch um(d,clk,qm);

34 d_latch us(qm, ~ clk,qs);

35

36 assign q = qs;

37

38 endmodule

39

40 // D latch

41 module d_latch(d,clk,q);

42 input d,clk;

43 output reg q;

44

45 always @(d,clk)

46 if (clk)

47 q = d;

48

49 endmodule

50

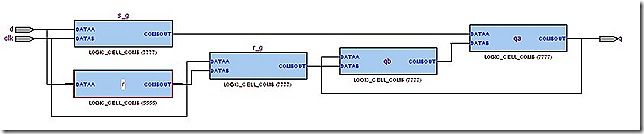

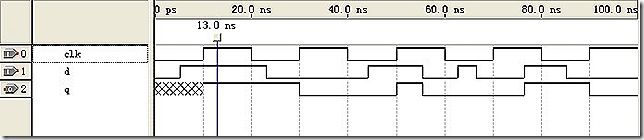

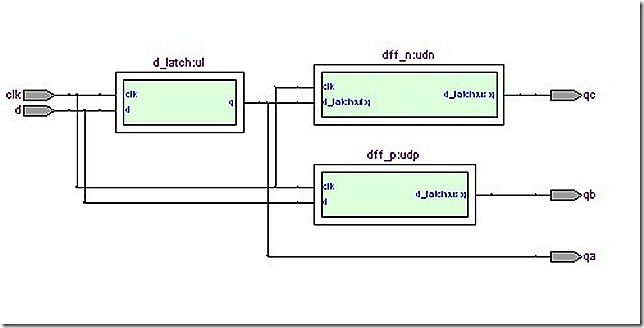

图15 在fpga内实现的电路

图16 功能仿真结果

Part V D触发器的应用

在DE2上显示两个16位的16进制数A和B,A在HEX7-4上显示,B在HEX3-0上显示。用SW15-0输入A,然后输入B,即要求数A存储在电路中。指定KEY1为clock,KEY0为Reset。

part5.v 代码:

2 module dff_R(d,clk,rst_n,q);

3 input d,clk,rst_n;

4 output reg q;

5

6 always @( negedge rst_n, posedge clk)

7 if ( ! rst_n)

8 q <= 0 ;

9 else

10 q <= d;

11

12 endmodule

13

14 // top-level file

15 module part5(SW,KEY,HEX7,HEX6,HEX5,HEX4,HEX3,HEX2,

16 HEX1,HEX0);

17 input [ 15 : 0 ]SW;

18 input [ 1 : 0 ]KEY;

19 output [ 6 : 0 ] HEX7,HEX6,HEX5,HEX4,HEX3,HEX2,

20 HEX1,HEX0;

21

22 wire [ 15 : 0 ]q;

23

24 dff_R u0(SW[ 0 ],KEY[ 1 ],KEY[ 0 ],q[ 0 ]);

25 dff_R u1(SW[ 1 ],KEY[ 1 ],KEY[ 0 ],q[ 1 ]);

26 dff_R u2(SW[ 2 ],KEY[ 1 ],KEY[ 0 ],q[ 2 ]);

27 dff_R u3(SW[ 3 ],KEY[ 1 ],KEY[ 0 ],q[ 3 ]);

28 dff_R u4(SW[ 4 ],KEY[ 1 ],KEY[ 0 ],q[ 4 ]);

29 dff_R u5(SW[ 5 ],KEY[ 1 ],KEY[ 0 ],q[ 5 ]);

30 dff_R u6(SW[ 6 ],KEY[ 1 ],KEY[ 0 ],q[ 6 ]);

31 dff_R u7(SW[ 7 ],KEY[ 1 ],KEY[ 0 ],q[ 7 ]);

32 dff_R u8(SW[ 8 ],KEY[ 1 ],KEY[ 0 ],q[ 8 ]);

33 dff_R u9(SW[ 9 ],KEY[ 1 ],KEY[ 0 ],q[ 9 ]);

34 dff_R u10(SW[ 10 ],KEY[ 1 ],KEY[ 0 ],q[ 10 ]);

35 dff_R u11(SW[ 11 ],KEY[ 1 ],KEY[ 0 ],q[ 11 ]);

36 dff_R u12(SW[ 12 ],KEY[ 1 ],KEY[ 0 ],q[ 12 ]);

37 dff_R u13(SW[ 13 ],KEY[ 1 ],KEY[ 0 ],q[ 13 ]);

38 dff_R u14(SW[ 14 ],KEY[ 1 ],KEY[ 0 ],q[ 14 ]);

39 dff_R u15(SW[ 15 ],KEY[ 1 ],KEY[ 0 ],q[ 15 ]);

40

41 // number B

42 seg7_lut uh0(q[ 3 : 0 ],HEX0);

43 seg7_lut uh1(q[ 7 : 4 ],HEX1);

44 seg7_lut uh2(q[ 11 : 8 ],HEX2);

45 seg7_lut uh3(q[ 15 : 12 ],HEX3);

46 // number A

47 seg7_lut uh4(q[ 3 : 0 ],HEX4);

48 seg7_lut uh5(q[ 7 : 4 ],HEX5);

49 seg7_lut uh6(q[ 11 : 8 ],HEX6);

50 seg7_lut uh7(q[ 15 : 12 ],HEX7);

51

52 endmodule

Conclusion

本实验是目前为止(altera DE2 数字逻辑)最容易的一个,所花时间较少即可完成。主要从门级到类似C语言的行为描述来构建存储单元。区分电平敏感和边沿触发。

Reference

1. Altera 数字逻辑设计实验练习3 (DE2光盘)

2. 《数字逻辑基础与verilog设计》 ch7. Stephen Brown …

ps: 这个实验要么是Stephen本人设计的,要么设计者看了他的这本书。完全一样。:)