【翻译】Nios design contest 2007-001

3等奖

使用数字分析的自动音频均衡器

Institution: Hanyang University

Participants: Sung-Wook Kim, Eun-Chan Kim, Bum-Su Jeong

Instructor: Professor Jae-Myoung Jeong

设计简介

我们的项目是一个使用数字信号分析的自动音频均衡器,可使低端的扬声器发出高端扩音的音质。消费者可据期望的音质复制扬声器的特性并将这些特性应用于低端的扬声器。本项目结构和应用简单,使用户用廉价的扬声器就可以享受较好的音质。

本项目设备经济,不需要升级现有系统就可用于高端的监视设备实现流畅响应。

功能描述

均衡器有3个主要功能:

l 测量和保存扬声器系统的响应。

l 分析和比较当前扬声器系统保存的扬声器响应,处理输入信号,调节当前扬声器系统的响应以模仿那些选定的扬声器系统。

l 测量和应用系统响应并评估性能。

要达到这些功能,我们将设计分成4个部分实现:

l 使用MegaCore库的功能实现FFT/IFFT块德输入信号。

l 通过连接每个范围系数的Nios II处理器的寄存器配置FFT/IFFT硬件均衡器。

l 使用SOPC Builder实现一个SDRAM控制器,flash控制器,用户逻辑FIFO缓存和音频译码接口。移植uClinux作为使用Nios II的系统。

l 具有GUI的PC监视软件,显示保存的扬声器的响应和测量响应。响应可下载到DE1板FPGA器件里。DE1板和PC之间用RS-232接口通信。

因为很多程序员熟悉Linux环境,所以我们选择uClinux系统,有助于缩短开发周期,而且现存很多可用的开发资源。另外,uClinux显著的减少所需的底层编码,比如非超载CPU中断处理。

性能参数

均衡器将一个已测量的独立扬声器的响应应用于当前扬声器系统,然后,再次测量当前扬声器系统的响应。系统将数字化显示期望的响应和改善的响应之间的相关性。使用基于PC的GUI,用户可以监视这两个响应有多接近。

架构设计

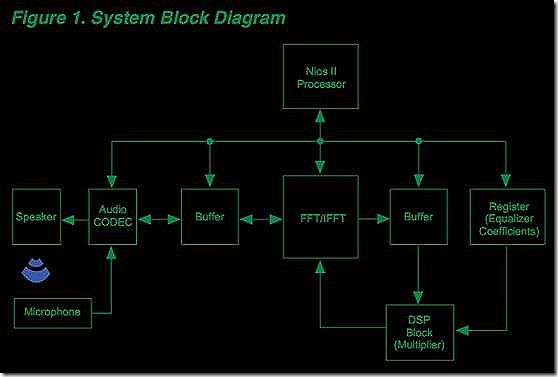

因为指定使用DE1开发板,系统的核心功能可用一个简略结构描述。图1是系统的方框图。数字信号处理器模块(DSP)执行大部分信号处理。Nios II处理器实现控制和监视模块。通过Nios II处理器使用硬件加速编译器(C2H)或用户自定义指令可以扩展功能。

我们插入一个数字信号分析仪(DSA)来测量扬声器的响应。麦克风不特定,因此,一旦频率特性符合,其他响应特性就不关键。

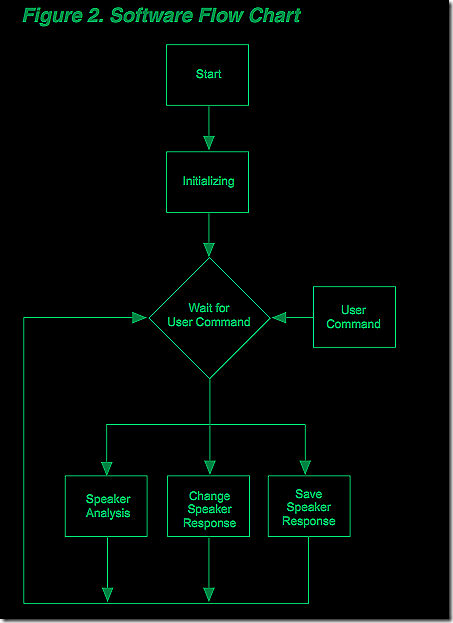

按照用户指令,系统执行3个主要功能:

l 扬声器分析—系统测量当前连接到系统的扬声器的响应。测量后,结果图形化显示便于用户决定是否保存。

l 保存扬声器响应—系统可将测量结构保存在flash里;稍后,系统可基于这个信息修改扬声器的响应。

l 调节扬声器响应—如果用户选择当前连接在系统的扬声器和期望的扬声器的响应,系统可通过DSP改变当前扬声器的响应。

当前市面上的均衡器功能类似,但用户必须手动调节每个变量。将来,我们肯会添加一个输入变量运算的特性到PC(就像商用均衡器那样)。这个特性使得用户不需要商用系统就可使用Winnap或Windows Media Player。

设计描述

硬件设计最难的部分是每步系统操作的调试和验证。我们仅在系统的其他部分验证后添加了一个未验证的块。通过仿真验证IP特性。这样处理有助于在调试时避免重复检查已存在的部分,提高效率。

幸运的是,Altera的Quartus II,SOPC Builder和Nios II集成开发套件允许使用已验证的IP和设计,大大减少调试负荷。比如:

l 因为使用未修改的FFT-IFFT块,只需执行一个简单的数据格式检查和时序仿真。

l 用SOPC Builder实现Nios II处理器,内存控制器,FIFO接口和音频CODEC接口。这些都是SOPC Builder的基本特性;因此,使用Nios II IDE很容易设计和测试固件。为加快设计进程,测试程序可在社区获得,比如Nios II 论坛。

l JotSpot WIKI(nioswiki)提供了uCLinux移植的详细解释。我们只需按照指令在SOPC Builder里实现所有的IP块。

l 使用基于Windows的程序设计PC监视程序。开发完监视程序后,很容易使用MATLAB和其他数据处理工具仿真监视信号。然后,下载编译的代码到DE1,验证。

设计特性

我们的设计有以下特性:

l 创造性—使用DSP,设计使低端的扬声器产生高端扬声器的效果。

l 廉价—除了音频CODEC和麦克风之外,所有的功能都可在一片Altera FPGA里实现,减少物料清单(BOM)。当然,系统性能未受廉价麦克风的影响,远远降低整个系统的成本。

l 方便快捷开发—Nios II处理器和用户自定义逻辑(缓存,FFT/IFFT块,寄存器,音频译码)直接连到Avalon总线,由其控制。因此,我们不需要使用通用I/O(GPIO)控制。将来,我们不需要使用单独的DSP块,而用用户自定义的指令通过Nios II处理器替代。

总结

DE1上的Cyclone FPGA足以实现一个16-bit,44.1-KHz采样率的2048采样的FFT/IFFT,Nios II 处理器和其他IP功能。但是,我们的设计只是测量和处理扬声器的响应,忽略相位延迟和其他失真,限制了系统的性能。将来,改善信号处理将提供更好的性能。

我们通常在DE2上实现项目,主要是快速原型,因为Altera的FPGA解决方案提供了可靠的工具和IP块,使得我们可以快速实现系统。另外,网络社区提供了快速、高质的回馈。希望Altera继续支持和鼓励这些社区。

Reference

Auto Audio Equalizer Using Digital Signal Analysis