Xilinx FPGA I/O电平标准简介

目录

- 一、LVTTL(LowVoltage Transistor-Transistor Logic)

- 二、LVCMOS(LowVoltage Complementary Metal Oxide Semiconductor)

- 三、PCI(PeripheralComponent Interconnect)

- 四、GTL(GunningTransceiver Logic)

- 五、LVDS(Low-Voltage Differential Signaling ,低电压差分信号)

-

- 1、名词解释

- 2、技术标准

- 3、技术原理

-

- 3.1、物理层技术

- 3.2、LVDS收发器

- 六、SSTL(Stub Series Terminated Logic)

- 七、HSTL(High Speed Transceiver Logic)

- 另附:

-

- 1、IOB内部可例化的原语

- 2、IOB内可用IO电平标准

- 3、DDR相关

一、LVTTL(LowVoltage Transistor-Transistor Logic)

LVTTL电平标准即低电压三极管-三极管逻辑电平标准是EIA/JESDSA的一种通用的3.3V电平标准,该标准的输入输出供电电压(VCCO)为3.3V,不需要参考电压(VREF)和终端电压(VTT)。LVTTL电平标准终端连接示意图如下所示,包括单向的和双向的终端链接方式。

LVTTL电平标准的具体参数如下表所示

注:VIH是输入高电平,VIL是输入低电平,VOH是输出高电平,VOL是输出低电平

- 内部电压Xilinx简称VCC,Altera简称VCCINT;IO电压Xilinx简称VCCO,而Altera简称VCCIO

- FPGA的IOB被划分为若干个组(bank),每个bank的接口标准由其接口电压VCCO决定,一个bank只能有一种VCCO,但不同bank的VCCO可以不同

二、LVCMOS(LowVoltage Complementary Metal Oxide Semiconductor)

LVCMOS电平标准即低压互补金属氧化物半导体电平标准是JEDEC(JESD8-5)的一种通用电平标准,该标准在V5系列FPGA中包括LVCMOS12、LVCMOS15、LVCMOS18、LVCMOS25和LVCMOS33。LVCMOS电平标准终端连接示意图如下所示,包括单向的和双向的终端链接方式。

常用的LVCMOS电平标准为LVCMOS33和LVCMOS25。

LVCMOS33电平标准的具体参数如下表所示

LVCMOS25电平标准的具体参数如下表所示

三、PCI(PeripheralComponent Interconnect)

PCI电平标准即外设器件互联电平标准,该标准支持33MHz和66MHz的总线应用,包括PCI-X、PCI-33、PCI-66等各类电平标准,该标准的输入输出供电电压(VCCO)为3.3V,不需要参考电压(VREF)和终端电压(VTT)。

PCI33_3和PCI66_3电平标准的具体参数如下表所示

PCI-X直流电平标准的具体参数如下表所示

四、GTL(GunningTransceiver Logic)

GTL电平标准即冈宁收发器逻辑电平标准,是Xerox发明的一种高速总线电平标准,该标准需要差分放大输入buffer和漏极开路(高阻)输出buffer。GTL为类似CMOS的一种结构,输入为比较器结构,比较器一端接参考电平,另一端接输入信号。1.2V电源供电。

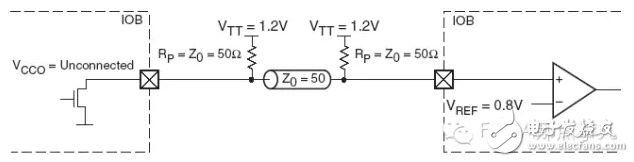

不连接VCCO的电路连接方式如下图所示

GTL标准不需要VCCO,但GTL_DCI标准需要连接1.2V的VCCO。其电路连接方式如下图所示

GTL电平标准的具体参数如下表所示

五、LVDS(Low-Voltage Differential Signaling ,低电压差分信号)

1、名词解释

LVDS(Low-Voltage Differential Signaling ,低电压差分信号)是美国国家半导体(National Semiconductor, NS,现TI)于1994年提出的一种信号传输模式的电平标准,它采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等优点,已经被广泛应用于串行高速数据通讯场合当,如高速背板、电缆和板到板数据传输与时钟分配,以及单个PCB内的通信链路。

2、技术标准

LVDS技术规范有两个标准,即TIA(电讯工业联盟)/EIA(电子工业联盟)的ANSI/TIA/EIA-644标准(LVDS接口也因此称为RS-644接口)与IEEE 1596.3标准。

3、技术原理

通常一个简单的点到点(point to point )LVDS的电路结构如下图所示:

其基本优势是结构简单,功耗低,速度快,抗干扰能力强,能够传输5-10m。

3.1、物理层技术

LVDS电平标准采用一对(两根)差分信号线传输数据。

通过驱动3.5mA的稳定电流电源,可在100Ω終端时,以350mV这样非常低振幅的差动信号来高速传送数据。其数据传输速度在规格内限定最大为655Mbit/秒。但这并不是极限值。通过各半导体厂商独有的加工,可以完成3Gbit/秒左右的高速传输速度。

LVDS的差动信号波形的具体示例请见图2。

将两根差动信号–正电极信号(A+)和负电极信号(B−),以1.2V的共同电压(Voc)为中心,使2个信号间以350mV的电位差摆动。然后,用探针测定示波器的差动,会得到图2这样的信号波形。这就是两个信号的振幅差((A+)−(B−))。以差动探针测定,就能得到振幅差的计算结果。但是这样的信号波形并不是物理存在的。

3.2、LVDS收发器

LVDS的发送器与接收器的基本结构如下图所示。它使用两根线(即差分信号线)来传输一个信号,并且使用恒流源(Current Source)驱动,即电流驱动型(而TTL、CMOS之类电平标准为电压驱动型)。

从LVDS结构原理可以看出,一对差分信号线只能够进行一个方向的数据传输,即单工通信(也称为点对点传输,point-to-point),但是我们常见的USB接口也只是使用一对差分信号线,为什么却可以双向传输呢?原因很简单,它是使用两对驱动器与接收器组合而成的,如下图所示:

这是一种半双工(half duplex)的配置结构,也就是说,在任意时刻差分信号线仍然只能是往一个方向传输数据,但可以分时进行双向数据传输,当驱动器1向接收器1发送数据时,驱动器2与接收器2相当于无效的,反之亦然。

六、SSTL(Stub Series Terminated Logic)

SSTL,即Stub Series Termination Logic, 短截线串联终端逻辑,和普通SDRAM的接口相比,DDR SDRAM接口电路的设计提出了更高的要求,其接口电路设计复杂度大幅度增加。为了解决DDR SDRAM接口电路的不足所带来的系统瓶颈问题,SSTL接口电路设计技术应运而生,SSTL规定了开关特点和特殊的端接方案,它可获得高达200MHz的工作频率。

SSTL分为SSTL_3(3.3V)、SSTL_2(2.5V)、SSTL_18(1.8V)、SSTL_15(1.5V)(对应的VREF=VTT分别为1.5V、1.25V、0.9V、0.75V),对应不同的供电电压,SSTL是传输线终端匹配的,因此SSTL具有输出阻抗和匹配方法的要求,这使其在高速信号传输时降低了EMI,改善了建立时间。SSTL的输入是一个差分比较电路,一端为输入,另一端为参考电压VREF,信号逻辑状态参考电平位VREF,而不再是GND,VREF为VDD的一半。DDR使用的就是SSTL电平标准。

SSTL与LVTTL驱动器没有太多的不同,但是输入缓冲却非常不同。SSTL输入是差分对,因此输入级提供较好的电压增益以及较稳定的阈值电压,这使得对小的输入电压摆幅具有比较高的可靠性。

SSTL对于不同类型的驱动器有不同的参数。SSTL_3和SSTL_2定义了2类驱动器,以区别不同的终端匹配方案。SSTL_18没有明确的类型定义,但是,取决于终端环境,驱动器必须能够在输入缓冲处产生相应的电压摆幅。

另:

DIFF_SSTL:全称 Difference Stub Series Terminated,是带有差分功能的 SSTL。

Logic,差分短截线串联端接逻辑,是带有差分功能的SSTL。 DDR3 的管脚使用的是 SSTL 或者 DIFF_SSTL。

七、HSTL(High Speed Transceiver Logic)

HSTL,即High Speed Transceiver Logic 高速收发逻辑,其最主要用于高速存储器读写,传统的慢速存储器阻碍了高速处理器的运算操作,此标准所要求的I/O结构是差分放大输入(一个输入内部关联成一个用户提供的输入参考电压,此电压用于单端输入)和使用Vcco的输出,VREF为VDD的一半。

在中频区域(100~180MHz),可供选择的单端信号IO结构有:HSTL、GTL/GTL+、SSTL、LVTTL。在180MHz以上,HSTL是唯一可用的单端IO接口。利用HSTL的速度,快速I/O接口明显地提高了整个系统的性能。HSTL是高速存储器应用的I/O接口选择,同时也很完美地提供了驱动多个内存模块地址总线的能力。QDR使用的就是HSTL电平标准。

JEDEC定义了四种驱动模式:Class I~IV,其区别仅在于输出电流的不同:

• Class I:IOH≥8mA,IOL≥-8mA;并行终端负载

• Class II:IOH≥16mA,IOL≥-16mA;串行终端负载

• Class III:IOH≥8mA,IOL≥-24mA;并行终端负载

• Class IV:IOH≥8mA,IOL≥-48mA;并行终端负载

另附:

VCCO:端口电压,电平标准,同一个VCCO下可兼容不同的IO标准。

VREF:参考电压,给部分输入标准提供参考电压。

每个BANK只能有一个VCCO,同一个VCCO下的标准可以不同。不同BANK可支持不同的VCCO。这就是电平兼容,电平兼容如下:

内部电压Xilinx简称VCC,Altera简称VCCINT;IO电压Xilinx简称VCCO,而Altera简称VCCIO。

除了TTL、COMS接口电平之外,LVDS、HSTL、GTL/GTL+、SSTL等新的电平标准逐渐被很多电子产品采用, 比如:

- 液晶屏驱动接口一般都是LVDS接口

- 数字I/O一般是LVTTL电平

- SDRAM、DDR电平一般是HSTL、SSTL的

在这样的混合电平环境里面,如果用传统的电平转换器件实现接口会导致电路复杂性提高。利用FPGA支持多电平共存的特性,可以大大简化设计方案,降低设计风险

SSTL细分的话有:SSTL3、SSTL2、SSTL18、SSTL15分别表示3.3V、2.5V、1.8V 和1.5V电平标准

其中SSTL3用于SDRAM,SSTL2用于DDR,SSTL18用于DDR2,SSTL15用于DDR3

SSTL还会分等级,常用的是等级I和等级II,比如 SSTL18_II

1、IOB内部可例化的原语

IOB内部有多种输入输出缓冲资源(buffer resource),他们可以原语的形式调用,在Spartan-6系列里:

单端IO标准的原语如下5个:

| 原语 | 功能 |

|---|---|

| IBUF | 输入缓冲 |

| IBUFG | 时钟输入缓冲 |

| OBUF | 输出缓冲 |

| OBUFT | 输出三态缓冲 |

| IOBUF | 输入输出缓冲 |

同时有7个差分IO标准的原语:

| 原语 | 功能 |

|---|---|

| IBUFDS | 输入缓冲 |

| IBUFGDS | 时钟输入缓冲 |

| IBUFDS_DIFF_OUT | 取反输出缓冲 |

| IBUFGDS_DIFF_OUT | 时钟取反输出缓冲 |

| OBUFDS | 输出缓冲 |

| OBUFTDS | 三态输出缓冲 |

| IOBUFDS | 输入输出IO缓冲 |

2、IOB内可用IO电平标准

每一种IO接口标准均有其特有的电压、电流、输入输出缓冲和端接匹配技术要求,IOB支持多种电平标准,用户可以自由灵活地为自己的设计选择合适的IO电平标准,Spartan-6系列支持的IO电平标准如下:

| 标准 | 解释 | 用途及厂商 | 输入缓冲 | 输出缓冲 |

|---|---|---|---|---|

| 单端IO电平标准 | - | - | - | - |

| LVTTL | Low Voltage TTL | General purpose 3.3V | LVTTL | Push-Pull |

| LVCMOS | Low Voltage CMOS | General purpose | CMOS | Push-Pull |

| PCI | Peripheral Component Interconnect | PCI bus | LVTTL | Push-Pull |

| I2C | Inter Integrated Circuit | NXP | CMOS | Open drain |

| SMBUS | System Management Bus | Intel | CMOS | Open drain |

| SDIO | Secure Digital InputOutput | SD Card Assoc,Memory Card | CMOS | Push-Pull |

| Mobile DDR | Low Power DDR | CMOS | Push-Pull | |

| HSTL | High-Speed Transceiver Logic | Hitachi SRAM; IBM;three of four classessupported | Vref based | Push-Pull |

| HSTL18 | High-Speed Transceiver Logic | Hitachi SRAM; IBM;three of four classes supported | Vref based | |

| SSTL3 | Stub Series Terminated Logic for 3.3V | SDRAM bus; Hitachi and IBM; two classes | Vref based | Push-Pull |

| SSTL2 | SSTL for 2.5V | DDR SDRAM | Vref based | Push-Pull |

| SSTL18 | SSTL for 1.8V | DDR2 SDRAM | Vref based | Push-Pull |

| SSTL15 | SSTL for 1.5V | DDR3 SDRAM | Vref based | Push-Pull |

| 差分IO电平标准 | - | - | - | - |

| LVDS25;LVDS33 | Low Voltage Differential Signaling | High-speed interface, backplane, video; National, TI | Differential Pair | Differential Pair |

| BLVDS | Bus LVDS | Bidirectional,multipoint LVDS | Differential Pair | Pseudo Differential Pair |

| DISPLAY PORT | Auxiliary channel interface for DISPLAY PORT | Flat panel displays | Differential Pair | Pseudo Differential Pair |

| LVPECL | Low Voltage Positive ECL | High-speed clocks | Differential Pair | N/A |

| MINI_LVDS | mini-LVDS | Flat panel displays | Differential Pair | Differential Pair |

| RSDS | Reduced Swing Differential Signaling | Flat panel displays | Differential Pair | Differential Pair |

| TMDS | Transition Minimized Differential Signaling | Silicon Image;DVI/HDMI | Differential Pair | Differential Pair |

| PPDS | Point-to-Point Differential Signaling | LCDs | Differential Pair | Differential Pair |

| Differential Mobile DDR | Differential LPDDR for CK/CK# | Differential Pair | Pseudo Differential Pair | |

| DIFF_HSTL_I;DIFF_HSTL_III;DIFF_HSTL_IV;DIFF_HSTL_I_18;DIFF_HSTL_III_18;DIFF_HSTL_IV_18 | Pseudo Differential HSTL | SRAM | Differential Pair | Pseudo Differential Pair |

| DIFF_SSTL3_I;DIFF_SSTL3_II;DIFF_SSTL2_I;DIFF_SSTL2_II;DIFF_SSTL18_I;DIFF_SSTL18_II;DIFF_SSTL15_II | Pseudo Differential SSTL | DDR, DDR2,DDR3 SDRAM | Differential Pair | Pseudo Differential Pair |

3、DDR相关

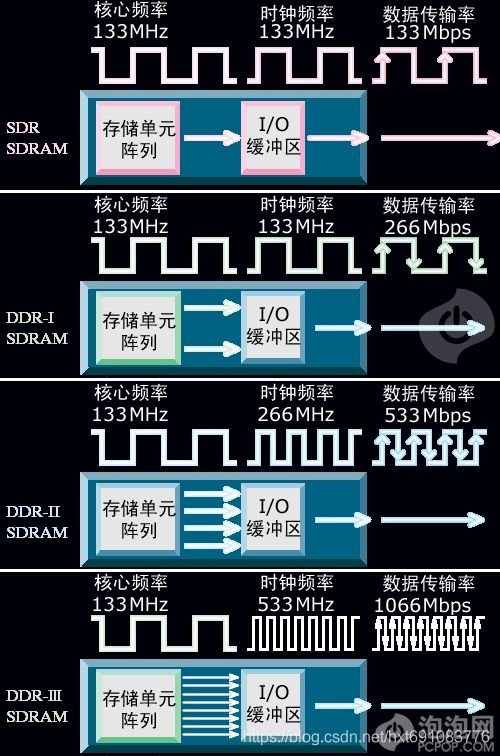

SDRAM从发展到现在已经经历了四代,分别是:第一代SDR SDRAM,第二代DDR SDRAM,第三代DDR2 SDRAM,第四代DDR3 SDRAM,现在已经发展到DDR5 SDRAM。

- DDR SDRAM是Double Data Rate Synchronous Dynamic Random Access Memory(双数据率同步动态随机存储器)的简称,是由VIA等公司为了与RDRAM相抗衡而提出的内存标准,为第二代SDRAM标准。其常见标准有DDR 266、DDR 333和DDR 400。其对于SDRAM,主要它允许在时钟脉冲的上升沿和下降沿传输数据,这样不需要提高时钟的频率就能实现双倍的SDRAM速度,例如DDR266内存与PC133 SDRAM内存相比,工作频率同样是133MHz,但在内存带宽上前者比后者高一倍。这种做法相当于把单车道更换为双车道,内存的数据传输性能自然可以翻倍。

- DDR2(Double Data Rate 2)SDRAM是由JEDEC(电子设备工程联合委员会)开发的第三代SDRAM内存技术标准,1.8v工作电压,240线接口,提供了相较于DDR SDRAM更高的运行效能与更低的电压,同样采用在时钟的上升/下降延同时进行数据传输的基本方式,但拥有两倍于上一代DDR内存预读取能力(即4bit数据读预取能力),其常见的频率规范有DDR2 400\533\667\800\1066\1333等,总线频率553MHz的DDR2内存只需133MHz的工作频率

- DDR3 SDRAM相比起DDR2具备更低的工作电压(1.5v),240线接口,支持8bit预读,只需133MHz的工作频率便可实现1066MHz的总线频率。其频率从800MHz起跳,常见频率有DDR3 800\1066\1333\1600\1866\2133等。DDR3是当前流行的内存标准,Intel酷睿i系列(如LGA1156处理器平台)、AMD AM3主板及处理器的平台都是其“支持者”。

- DDR4与DDR3一样是8位预取,为什么频率增加了一倍呢?因为DDR4采用了与GDDR5(显存)类似的方式,即Bank Group。(数据预取的增加变得更为困难)至于怎么会使速度翻倍,查阅资料,但没看懂,跟内部的结构有关。另外,具有更可靠的传输规范,数据可靠性进一步提升;工作电压降为1.2V,更节能。

相关定义:

核心频率:为内存Cell阵列(即内部电容)的刷新频率

时钟频率:I/O Buffer(输入/输出缓冲)的传输频率(I/O频率或工作频率)

等效频率:指数据传送的频率(即数据频率)

关系:工作频率=核心频率×n/2;等效频率=工作频率×2(此处的2即DDR在上升下降沿都读写的原因);

从1~5DDR的核心频率没有多大的进步,频率一直在133MHz-200MHz之间徘徊,这是因为电容的刷新频率受制于制造工艺而很难取得突破(颗粒物理上原因)。但是内存的频率却一直在成倍增加,这因为采用了预取的技术。(一直没找到资料说明核心频率就是DDR外接CLK引脚的频率)

参考:

http://m.elecfans.com/article/1309878.html

https://www.doczhi.com/p-862400.html

https://blog.csdn.net/ys2333/article/details/106868355

https://www.cnblogs.com/lifan3a/articles/5217897.html

https://blog.csdn.net/qq_35569806/article/details/87920804

https://www.amobbs.com/thread-5743161-1-1.html

https://blog.csdn.net/u012489236/article/details/107730731