连接器信号完整性仿真教程 七

本将介绍微带线及差分微带线仿真。做连接器信号完整性仿真时,有时后没法将激励端口直接设置到连接器端子上,这就需画出连接器PCB PAD,将激励端口设置在PAD的端面上,或者用引线连接PAD,将引线引出到适当的位置,再在引线端设置激励端口。通常把SMT PAD及引出线当作微带线来处理。在连接器信号完整性仿真教程六中,已经讲过什么是微带线。在做连接器信号完整性仿真时,这个微带线不是随便画画就可以的,必须做到阻抗匹配。如果你的连接器设计目标特性阻抗是50欧姆,那么用于设置端口的微带线也应是50欧;如果你的连接器设计目标差分阻抗是85欧姆,那么用于设置端口的差分微带线特性阻抗也应该是85欧姆。如何知道自己画的微带线特性阻抗是否是自己需要的呢,一是用计算工具计算,第二就是仿真。常用的计算工具计算结果并不十分准确。最好的办法是先用计算工具计算个大概,然后再进行仿真,将微带线调整到阻抗完美匹配。下面介绍常用微带阻抗计算工具及微带线及微带差分线仿真操作。

一 微带阻抗计算工具

首先介绍一款在线计算工具。可能是职业关系,我比较喜欢访问EDA365电子论坛网站,也比较喜欢EDA365电子论坛网站上EDA工具箱中的微带阻抗及差分微带阻抗计算工具,常用它做阻抗粗略计算。其微带阻抗计算的界面如下:

其差分微带阻抗计算工具的界面如下:

最常用的微带线阻抗计算离线工具为Txline,其绿色版很小,1MB多点,如下:

是免安装的,解压后就三个文件,如下:

双击txline.exe即可运行,可以将xline.exe快捷键发送到桌面,方便使用。

Txline的运行界面如下:

从其界面内容可以看出其功能是相当强大的。

二 微带线仿真

除仿真夹具中会用到微带线,其实 高频连接器信号完整性测试PCB中,连接器锡脚与SMA接头连接的走线绝大部分也是微带线,这个高频测试板,是很贵的,如果画出来的板不做仿真,做出来才发现阻抗不匹配,那就麻烦了。因此,了解与掌握微带线仿真十分必要。从ED365的微带阻抗计算工具可以看出微带线阻抗与微带线的长度无关,与微带宽度及其材料厚度基板厚度及介电常数相关。因此在做微带线仿真时,不必过分在意微带线的长度。对于SMT连接器,一旦其Pitch及锡脚宽度确定,其PCB PAD的宽度几乎就确定了,仿真的重点在于确定基板厚度,以实现阻抗匹配。

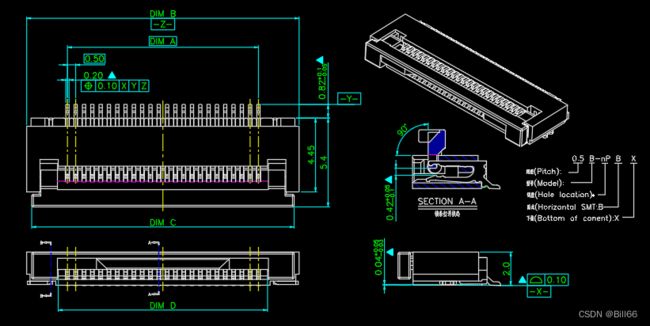

下图是一款FPC连接器。

下图是锡脚的放大图:

从放大图可以看出,在对这款连接器做信号完整性分析时,就不方便直接在PAD上设置端口,需在PCB PAD或其延长线上设置端口。这款FPC Connector 的PAD宽度为0.30。现在以已该连接器为例,讲解微带线仿真。假定此处连接器的目标特性阻抗为50欧姆,那么其PCB PAD及其延长微带线阻抗也应是50欧姆,才不会影响仿真准确性。

在用CST仿真前,需构建3D模型。在画微带线前,先用计算工具计算出基板的大概厚度,以便绘制微带3D模型。下面是计算结果:

下面是在UG中画出的微带线结构(当然也可以在CST中直接画出):

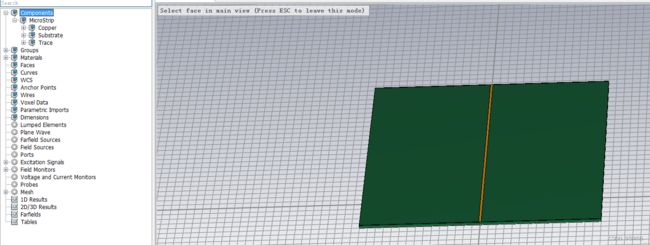

导入CST后如下图示(这里是用的CST2023做演示):

这个仿真使用的是多Pin无屏蔽连接器仿真模版 。

下面设置材料。

1. 设置基板(Substrate)材料:

2. 设置微带(Trace)材料:

3. 设置覆铜(copper)材料:

设置端口

这里需要设置波导端口。在设置波导端口前,先用CST宏工具计算波导端口边界延伸系数K。如下:

从图可以看出K的取值范围为3.78~7.67,可在设置端口时将K值取5。

设置端口1如下:

设置端口2如下:

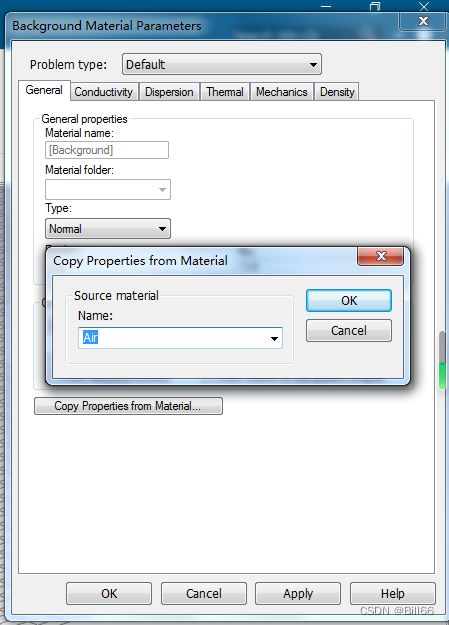

设置背景 设置背景为空气,如下:

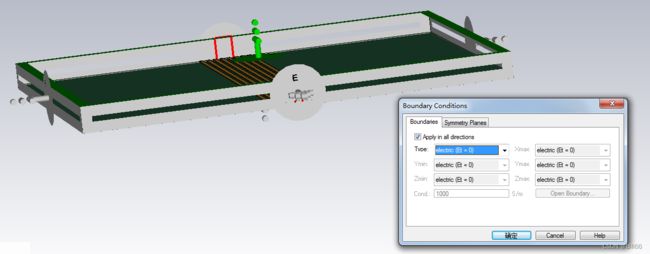

设置边界条件 将边界条件设置为电边界,设置如下:

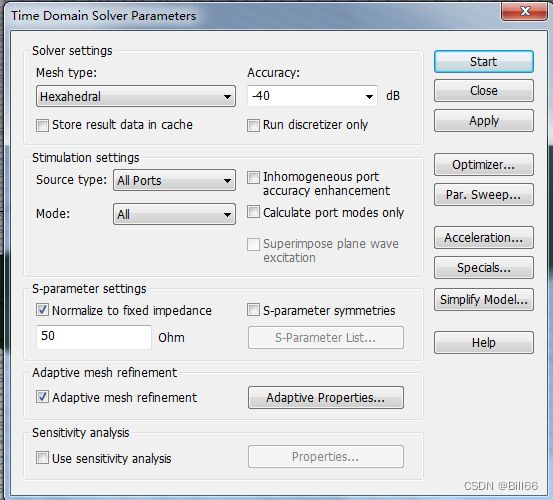

开始仿真 仿真设置如下:

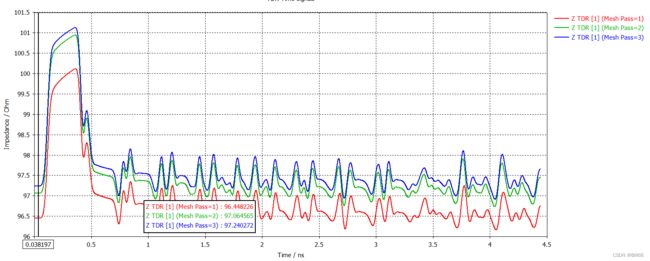

查看仿真结果 仿真结果如下:

从TDR曲线可以看出微带线阻抗其实是在75欧姆左右,并非目标值50欧,说明计算结果不是十分精确。

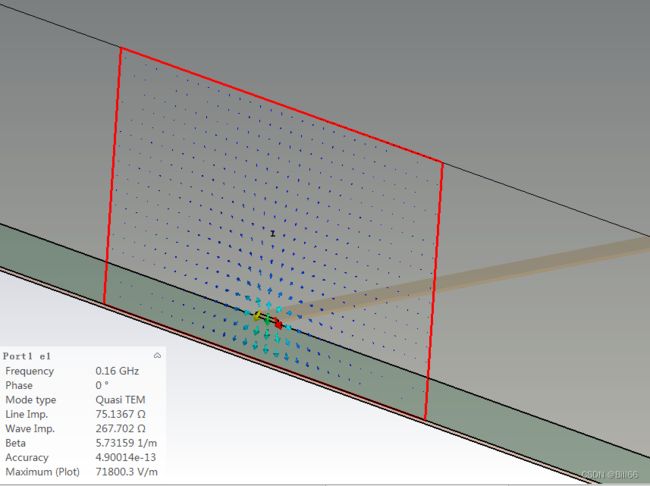

下面是Port Mode:

从上图可以看出无论Port1还是 Port2其线性阻抗都是75.1367欧姆,这个就是微带线特性阻抗。

要做到阻抗匹配,需继续调整PCB基板厚度,再做仿真,直到阻抗匹配程度在允许的公差范围内。

下面再用Txline计算一下仿真模型的特性阻抗,结果如下:

Txline的计算结果为:77.3034欧姆,其结果更接近仿真结果。如果要用计算工具微带线的特性阻抗,建议使用Txline。下面用Txline试算一下基板厚度结果如下:

下面将基板厚度调整到0.172mm,再做一次仿真,看下结果如何。仿真结果如下:

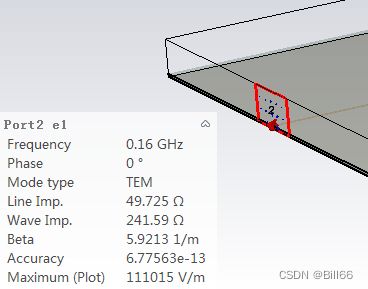

下面是Port Mode:

从仿真结果可以看出,Txline的计算结果与仿真结果差异并不大,在1%以内。以这个精度计算微带阻抗来匹配连接器信号完整性仿真已经够了,也就是说如果你不想通过仿真来调节匹配连接器的微带线参数,可以用这个工具来计算。

三 差分微带线仿真

为了减少串扰,提高传输可靠性,高速高频信号基本都是通过差分线来传输的。如PCI E标准中,严格定义了连接器的差分对Pin,基本上是一个·差分对间隔两个GND Pin,完全做到差分对Pin不相邻。现在又用上面的FPC Connector 来做这种差分微带线阻抗仿真,假定该Connector的目标特性阻抗为100欧姆。在绘制3D模型前,同样先使用工具计算基板的厚度,结果如下:

绘制的模型如下图示:

导入CST后如下(采用多Pin无屏蔽连接器仿真模版):

与微带线仿真一样设置材料 。

设置差分端口

在设置端口前,先用宏工具,计算端口边界延伸系数K,如下:

这里K可取6。

设置端口Port1 如下:

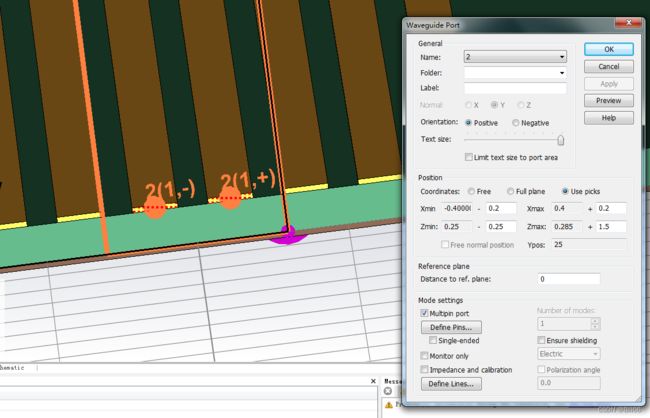

设置端口Port2 如下:

设置背景为Air

设置边界为电边界 如下:

开始仿真

查看仿真结果 TDR如下:

Port Mode如下:

从仿真分析结果可以看出,计算结果与目标阻抗还是存在些出入。如果需要精确匹配还需对基板厚度再做调整,适当加厚。将基板厚度调整到0.35后的仿真结果,如下:

从仿真分析结果可以看出,计算结果与目标阻抗还是存在些出入。如果需要精确匹配还需对基板厚度再做调整,适当加厚。将基板厚度调整到0.35后的仿真结果,如下:

从结果可以看出,差分微带线的阻抗已很接近目标阻抗100欧,其差异小于5%,匹配精度已经足够。

从结果可以看出,差分微带线的阻抗已很接近目标阻抗100欧,其差异小于5%,匹配精度已经足够。

微带线及差分微带线阻抗仿真操作比较简单。本期教程就讲到这里。

到目前为止,与连接器信号完整性仿真相关的基本操作,都已做了介绍。欢迎有兴趣的朋友上传模型,探讨具体的仿真操作或仿真中面临的问题。

本期仿真实例及微带计算工具Txline有打包上传到CSDN,文档连接为:https://download.csdn.net/download/billliu66/88259421