【无标题】RC抽取工艺文件(三)Layer map错误

qrclayermap的作用是把Innovus里的层和qrcTechFile里的层对应起来。

Innovus的层信息来自LEF或OA tech library,其使用字符串MET1, VIA1等代表层 。qrcTechFile里也使用字符串代表层,但和Innovus的字符串不同,需要用这个qrclayermap把两者对应起来。

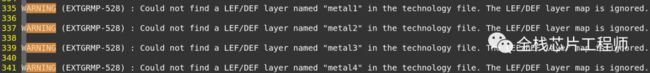

在后端实践中发现log中有如下告警,layermap的层次名字不对!开始定位。

可见,检查EDA工具的log是非常重要的。

如何找对正确的Layermap关系呢?介绍几种方法:

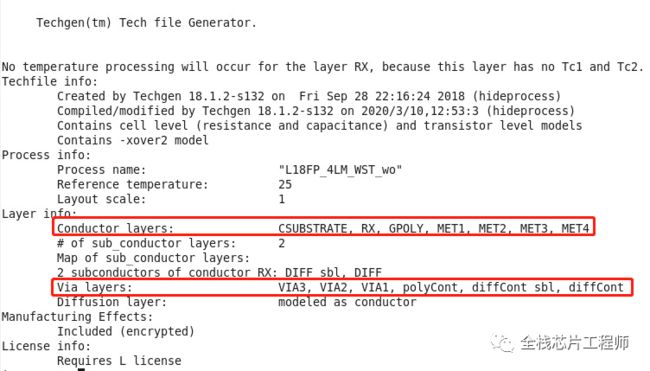

方法1:Techgen

innovus 7> Techgen -techinfo ../PDK/qrcTechFile

方法2:extractRC

跑完route后,再跑一下extraction、timeDesign。

这时不需要signoff 精度的parasitics,-effortLevel high就可以了。

setExtractRCMode \-engine postRoute \-coupled true \-effortLevel highextractRC

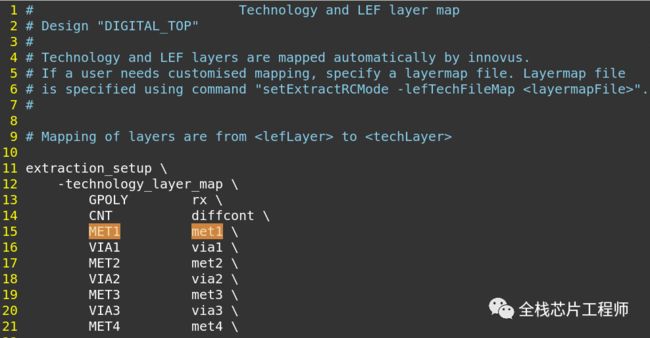

extractRC结束后,Innovus会在当前工作目录下生成一个extLogDir,在里面生成了innovus自动生成的layer map。

INFO (EXTIQRC-105) : Starting design extraction....

No layermap file specified. Automatically mapping tech and lef layers. Log file is 'extLogDir/IQuantus_06-May-2022_14:50:21_259818_3ioJJS/extr.DIGITAL_TOP.layermap.log'.打开:extLogDir/IQuantus_06-May-2022_14:50:21_259818_3ioJJS/extr.DIGITAL_TOP.layermap.log

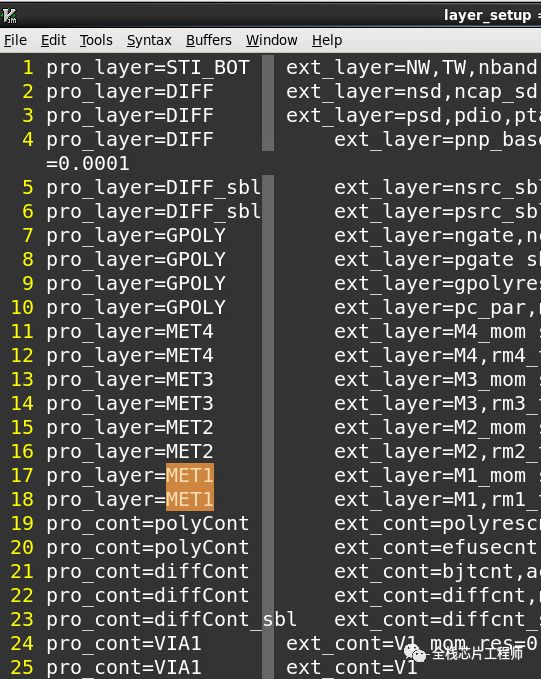

左边这列是Innovus 的层,右边是qrcTechFile的层。

注意:

以前常用的flow是从Innovus导出GDS或DEF,在命令行跑Quantus QRC生成SPEF。现在可直接在Innovus调用Quantus QRC生成signoff质量的SPEF。

setExtractRCMode \-engine postRoute \-coupled true \-effortLevel signoffextractRCrcOut -rc_corner $corner \-spef $spefFile

但是-effortLevel signoff 是必须的,否则Innovus会用自带的IQuantus或 TQuantus extraction engine,生成的SPEF精度会差些,因为我们需要用的是Quantus QRC,而不是IQuantus、TQuantus。

方法3:查看qrctechfile

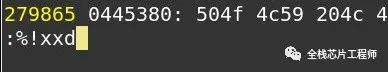

qrcTechFile默认打开是乱码,采用如下命令即可查看:

xxd是linux的一个命令,vim可以通过”!”来调用外部命令,其功能就是进行十六进制的dump或者反之。

方法4:查看PDK的layer_setup

当然还有其他方法,比如参考starRC的map文件等等,欢迎补充,另外,通常我们直接运行命令执行RC提取:

qrc -64 -cmd qrc.tcl MCU.def

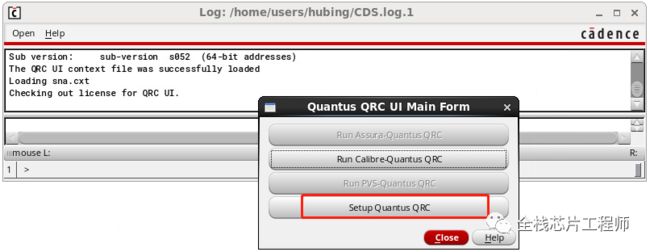

我们也可以启动GUI:

qrcui &

% qrcui [ -help | -h | -H ]

[-V | -v] displays the Quantus version

[-nograph] starts the standalone Quantus UI in non-graphical mode

[-nocdsinit]

[-replay filename]

[-log filename]

RISC-V E203设计之旅(二)

RISC-V E203设计之旅(一)

RC抽取工艺文件(一)

RC抽取工艺文件(二)

DFT设计实战(一)

DFT设计实战(二)

DFT设计实战(三)

DFT设计实战(四)

DFT设计实战(五)-ATPG

如何对ICG过约束:set_clock_gating_check

芯片ECO(一)

详解GDSII文件

详解SPEF文件

详解SPI协议

详解I2C协议

详解GearBox设计原理

详解set_clock_gating_style命令

【MCU】Cortex-M3 SoC的主栈指针

低功耗设计之Multi-Bit Cell

剖析数字后端site、track、pitch的概念

Verilog中,2'b1x和2’b0x造成的仿真器、综合器的mismatch!

【剖析】傅里叶变换、拉普拉斯变换、Z变换

【剖析】傅里叶变换、拉普拉斯变换、Z变换(二)

芯片设计之CDC异步电路(五)

芯片设计之CDC异步电路(四)

芯片设计之CDC异步电路(三)

芯片设计之CDC异步电路(二)

芯片设计之CDC异步电路(一)

OCV分析计算

低功耗设计之Power Switch Cell

深度剖析“异步复位、同步撤离”

芯片后仿(二)

时钟切换clk_switch

8B/10B、64B/66B编解码(一)

8B/10B、64B/66B编解码(二)

剖析FPGA怎么实现“超前进位加法器”(一)

剖析FPGA怎么实现“超前进位加法器”(二)

FPGA原型验证-时钟门控的替换

行波进位/超前进位加法器详解

AES加密算法(一)

Cadence Voltus-功耗分析&IR-drop(一)

Cadence Voltus-功耗分析&IR-Drop(二)

Cadence Voltus-功耗分析&IR-drop(三)

Cadence Voltus-功耗分析&IR-drop(四)

欢迎加入CIS、MCU技术交流群,先加我微信,我拉你进群!

感谢阅读,别走!点赞、关注、转发后再走吧