【文献学习】异质异构集成

在项目学习遇到“三维异质异构集成,3D Heterogeneous Integration”这个概念,理解起来很是困难,所以查阅一些文献帮助理解。

先说结论:异质异构集成,是指应用跨学科思维(能集成进去的东西很多,概念包含范围很广)将单独制造的组件集成到一个更高层次的组件,在系统级别是获得更强的功能和工作特性。

异构集成背后的总体思路是在同一封装中集成多个组件,使封装能够以小尺寸执行特定的高级功能,具体的实现过程在微系统、MEMS、集成电路等方向都有很多研究。不同于电路集成或封装集成,传统的电路集成只会使芯片更贵更大,封装集成只是装在一起工作没有深层次整合。

用于异质集成的组合组件可以在系统级(预组装的封装或子系统)、功能级(专用处理器、DRAM、闪存、电阻器/电容器/电感器、滤波器、连接器、MEMS 设备、传感器)和技术(例如,一种针对芯片尺寸进行优化的技术,或另一种针对低功耗进行优化的技术)。

在HETEROGENEOUS INTEGRATION ROADMAP 网站给出了许多方向异质异构集成的已有方法和发展趋势,许多出版刊物中也有异质异构集成实现方法的研究,包括材料学、物联网、智能硬件、芯片等领域。

2019 Edition - IEEE Electronics Packaging Society![]() https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2019-edition.html

https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2019-edition.html

如果要深入理解这个集成过程,需要读懂某个集成组合过的“为什么”和“怎么做”

例如,在"Wafer-Level Heterogeneous Integration for MOEMS, MEMS, and NEMS"中,要把MOEMS,MEMS,希望在制造时使用高性能材料和子系统,例如,单晶硅、锗、III-V 族材料、压电材料、形状记忆合金、碳纳米管或纳米线等 高性能光子、机械、电气和纳米材料的组合。可能某些芯片需要这些特殊组合,否则无法实现设想的功能。

至于为什么“两个组件的集成能实现更好的功能与特性”这就涉及到底层的物理知识,比如“不同的材料堆叠在一起,可能能形成有规律的晶向或结构”,或者是“需要芯片有更高的处理频率,就需要把一些能承载高频的材料通过特定工艺集成上去”想实现这个功能,就需要带额外的“扩展功能库”,而这个“功能库”你要是用外接的话不仅体积大而且性能还不好。

两个例子:

两个 90-nm SiGe BiCMOS 收发器与一个 45-nm 专用集成电路 (ASIC) 的集成,用”传统的电路集成”方式,大部分活动功率耗散在芯片外围的高速链路中,并且极不均匀。峰值温度可能会增加 40 °C; 如果用heterogeneous integration 用特定的工艺做集成,能一定程度上缓解这个高速链路产热。

CdS过滤器与 (In, Ga)N LED、Si PIN光电探测器和微流体装置的异质集成。

激光诱导荧光 (LIF) 检测技术具有选择性和高灵敏度,是一种用于生物分析检测应用的热门检测技术。想要把荧光检测组件小型化到微系统级别,以提供便携性和低制造成本的优势。此外,小型化可以实现新功能。(具体啥功能原文没说)

把特定的功能模块集成到硅基上,实现基于多色荧光的生物测定和化学检测微系统。

至于,如何进行“异质异构集成”, MOEMS、MEMS 和 NEMS 的晶圆级异构集成里面详细介绍了:MOEMS、MEMS 和 NEMS 设备的晶圆级异构集成技术和平台的最新技术,可以分为两类:1) 使用via-first 工艺的异构集成和2) 使用via-last 工艺的异构集成。具体的实现过程异常复杂,设计很多物理原理和工艺技术,我目前基本看不懂。但是,知道这个异质集成的方法是有很多人在研究并且可行的

调研过程:

从字面意思看,三维异质异构集成应该是一种集成技术,类似于封装技术,把异质异构的材料或者元器件、芯片深层次连结到一起,发挥更优越的性能。

尝试在wiki百科查找这个词,但发现没有被收录。查英文辞典:

多种类的,不均一的,多相的,混杂的。

分别在nature和science及其子刊中搜索 Heterogeneous Integration 相关文献,发现主要方向都集中在:MEMS、半导体材料和集成电路。在查阅的文献中,大多是用”Heterogeneous Integration “这个方法实现一些功能或者突破,得到更微型的封装、更好的性能。这个概念都没有溯源引用,就像一些”众所周知的技术或方法“。

N. M. Jokerst et al., "The heterogeneous integration of optical interconnections into integrated microsystems," in IEEE Journal of Selected Topics in Quantum Electronics, vol. 9, no. 2, pp. 350-360, March-April 2003, doi: 10.1109/JSTQE.2003.813307.

光互连与集成微系统的异质集成 异构集成,是实现化合物半导体光电器件、Si CMOS电路和有机材料集成的一种方法。异构集成方法利用可以独立生长和优化的不同材料,结合在一起形成一个集成系统,是创建高性能微系统的高效方法。文章描述了使用薄膜异质集成将各种光学互连集成到微系统中。 集成微系统的表面粗糙度可以到几微米以内,薄膜器件的两侧都可以进行contacted, optically coated等加工,并实现三维堆叠结构。M. Lapisa, G. Stemme and F. Niklaus, "Wafer-Level Heterogeneous Integration for MOEMS, MEMS, and NEMS," in IEEE Journal of Selected Topics in Quantum Electronics, vol. 17, no. 3, pp. 629-644, May-June 2011, doi: 10.1109/JSTQE.2010.2093570.

针对Moems、Mems和Nems的晶圆级异构集成 用于微光机电系统 (MOEMS)、微机电系统 (MEMS) 和纳米机电系统 (NEMS) 的晶圆级异构集成技术,可以将不同类别的材料和组件组合成单个系统。因此,高性能材料和子系统可以以一些不可思议的方式组合,从而形成复杂且高度集成的微纳米系统Chediak, J.A., Luo, Z., Seo, J., Cheung, N., Lee, L.P., Sands, T.D., 2004. Heterogeneous integration of CdS filters with GaN LEDs for fluorescence detection microsystems. Sensors and Actuators A: Physical 111, 1–7.. doi:10.1016/j.sna.2003.10.015

用于荧光检测微系统的CdS滤波器与GaN LED的异质集成 将CdS 薄膜过滤器、(In、Ga)N 薄膜蓝色 LED 和一次性 PDMS微流体装置异质集成到 Si PIN光电探测器基板上,实现混合荧光检测微系统。 制造了基于多色荧光的生物测定和化学检测微系统。

比较有溯源性的文献:

S. S. Iyer, "Heterogeneous Integration for Performance and Scaling," in IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 6, no. 7, pp. 973-982, July 2016, doi: 10.1109/TCPMT.2015.2511626.

文章是Heterogeneous Integration关键词较早的文章,且引用次数较多。文章提到,摩尔定律一直依赖于硅基地工艺、CMOS工艺尺寸不停的缩小,而且以及要逼近极限。此外,研究发现了诸如Cu interconnects, low-k dielectrics for interconnects, strained channelsand high-k materials for gate dielectrics 这些功耗更低、性能更高、尺寸更小的工艺,催生了 SoC 方法,即芯片系统。单个芯片上能够集成越来越多的功能,同时在包装和板上集成多个模具尺寸比例只有3到5倍,作者对这个效果不太满意。

随着半导体特征尺寸的减小放缓和物联网的到来,异质集成和系统化封装,是支持芯片更小更强的有力技术。封装技术变得更侧重于整体系统性能和成本,而不是单个组件。

异质集成可以理解为一种更深层次的封装,其不再是一种保护裸片的方法,而是一种将组件们互连的方法,这种集成方案尝试获得更紧密的电气连接、更简单的裸片到裸片连接协议,以更低的延迟和更低的功率实现更高的带宽等。已有的 3-D (异质)集成的一定程度上实现了上面的设想,“芯片堆栈技术”已经证明了这些特性。(这应该指芯片集成领域的”异质集成“)

这种转变(异质异构集成、Soc、三维封装技术),将成为未来几年维持摩尔定律的支柱。

在调研 Heterogeneous Integration 技术时,发现了一共很有权威性的网站:异质异构集成发展线路图

HETEROGENEOUS INTEGRATION ROADMAP

异质异构集成路线图 (HIR) 是由三个 IEEE 协会(电子封装协会、电子器件协会、光子协会)SEMI 和 ASME EPPD 发起的。它致力于在任何地方拥抱创新,并尽可能促进合作,以加速微电子市场格局的进步。

在书中的overview章节介绍:

异质异构集成是指,将单独制造的组件集成到一个更高层次的组件( 封装中的系统 - SiP )中,在系统级别是获得更强的功能 enhanced functionality 和工作特性 operating characteristics 。

在这个定义中,组件应该被看作是集成到单个封装中的任何单元,无论是单个芯片、MEMS器件、无源元件和组装的封装或子系统。操作特性也应在其最广泛的意义上加以考虑,包括系统级性能和成本等。

通过SiP的异构集成从较小的功能单独打包构建大型复杂系统。异质性和相关的集成影响深远,可以与材料、组件类型、电路类型、节点、互连方法以及源或起源相关。

此外,找到了介绍异质异构集成的论文:

W. Chen and B. Bottoms, "Heterogeneous Integration Roadmap: Driving Force and Enabling Technology for Systems of the Future," 2019 Symposium on VLSI Technology, 2019, pp. T50-T51, doi: 10.23919/VLSIT.2019.8776484.

论文名和book HETEROGENEOUS INTEGRATION ROADMAP 第一章标题相同,但是内容有所差异。

论文中给出的定义和书中基本一致。

组合组件可以在系统级(例如,预组装的封装或子系统)、功能(例如,专用处理器、DRAM、闪存、表面贴装设备 (SMD) 电阻器/电容器/电感器、滤波器、连接器、MEMS 设备、传感器)和技术(例如,一种针对芯片尺寸进行了优化,另一种针对低功耗进行了优化)。

异构集成背后的总体思路是在同一封装中集成多个芯片。这使封装能够以小尺寸执行特定的高级功能。

文中提到,半导体行业试图将所有东西都挤进一个单片芯片中。然而,普通的集成指挥使芯片变贵变大。异构集成通过将具有不同工艺节点和技术的芯片相结合来解决这个古老的问题。该技术可以持续增加功能密度并降低每个功能的成本,以保持电子产品成本和性能的进步。异构集成对于保持更高的性能、更低的延迟、更小的尺寸、更轻的重量、每个功能的功率要求更低和成本更低的进展速度至关重要。

论文给了几个例子:

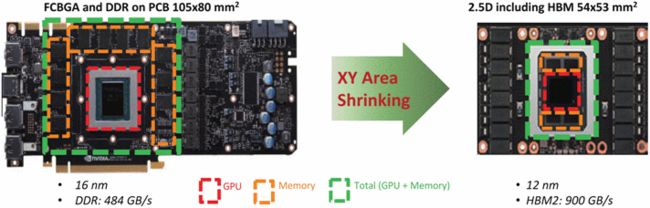

2.5D 硅中介层集成了高级节点 ASIC 和 HBM 内存堆栈,由 AMD 和 ASE 开发

使用 2.5D 封装与 异质异构集成的方法,实现了 XY 外形尺寸的减小和更高的速度。

英特尔开发的硅桥示例,用于在有机基板上将多个芯片紧密连接在一起。不同节点或来自不同公司的组件可以异构集成在一个 SiP 中。

半导体芯片的异构集成技术 - hotchips的文章 - 知乎

https://zhuanlan.zhihu.com/p/26279506

一直以来电磁频谱中的毫米波(mmW)和亚毫米波(sub-mmW)/太赫兹(THz)都未被人类充分利用 想利用起来,而当前半导体和封装技术的快速进展以及商用测试设备已经达到了1太赫兹的测试能力,使得在这些高频段频谱上开发重要应用已成为可能。

以低成本获得更佳性能、更小型、更有效、更可靠而愈加复杂的功能。

硅是半导体技术的主导材料,有很多成熟的技术。

众多应用只能使用像磷化铟(InP)和氮化镓(GaN)这样的化合物半导体技术才能实现。

1太赫兹的晶体管,具备高增益和高功率,以及超高速混合信号电路。

氮化镓能使器件具备大带宽、高击穿电压、以及高达100GHZ的输出功率。

将异类半导体集成为一体——即异构集成。

产生即经济又具有小尺寸的更大设计灵活性和更好的系统性能

频率的上升 互联块和线内的损耗迅速地增加 缺乏几何和互联清晰度

为了克服寄生效应 要求复杂的三维单片或晶圆级异构集成不同的半导体

简而言之,介绍的是一种把磷化铟(InP)和氮化镓(GaN)Heterogeneous Integration到硅片上实现THz频率工作。

另一篇有一定参考价值的中文文献:

[1]郝继山,向伟玮.微系统三维异质异构集成与应用[J].电子工艺技术,2018,39(06):317-321.

文中给出的异质异构集成定义:

三维异质异构集成 是指通过跨学科多专业融合, 通过协同设计和微纳集成制造工艺, 实现不同材料、不同结构和不同功能元件的一体化三维集成。三维异质异构集成的典型特征有:1) 三维异质异构集成是系统设计与微纳集成的紧密结合;2) 三维体现在三维结构和三维互连;3) 异质异构集成体现在多材料体系的融合;4) 三维异质异构集成的实现需要多工艺体系的运用。

应用:

通过将化合物半导体器件在硅基射频电路上的堆叠集成, 以可接受的成本大幅提升电路性能和集成密度, 体积质量仅为传统产品的1/40, 且集成一致性更好。