数字集成电路后端(Innovus)开发设计

一、本文目的是对数字IC进行:

1、平面规划设计(Floorplanning the Design);

2、电源路径设计(Routing Power with Special Route);

3、使用Early Global Router分析路径(布线)可行性(Analyzing Route Feasibility with the Early Global Router)。

二、设计过程与结果:

1、平面规划设计(Floorplanning the Design)

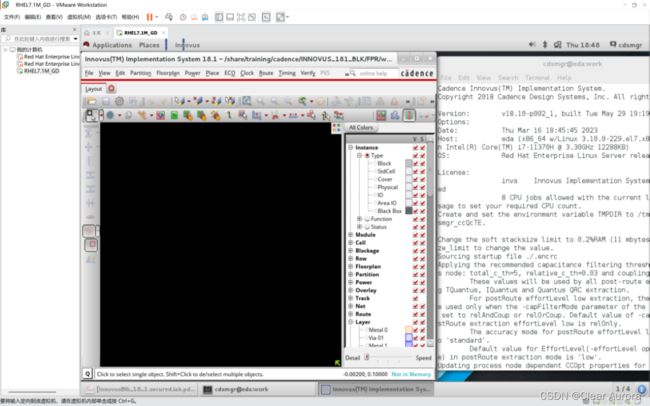

1)从根目录进入工作路径/share/training/cadence/INNOVUS_181_BLK/FPR/work,如下图所示:

2)在此路径下打开Innovus如下图:

3)导入路径/share/training/cadence/INNOVUS_181_BLK/FPR/work下dtmf.globals设计文件,如下图:

4)切换到floorplan view查看设计中的macro,module和port,如下图:

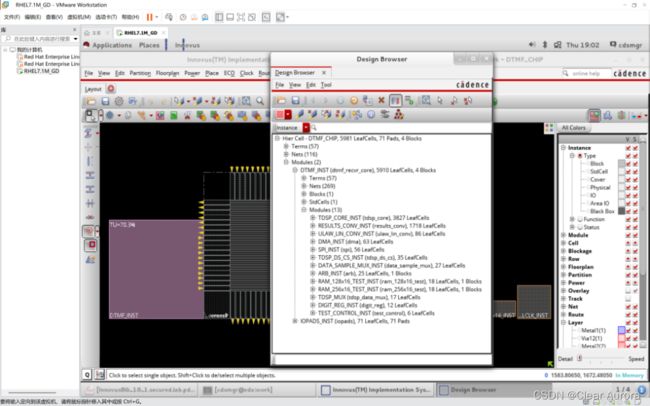

5)通过Tools > Design Browser显示设计的hierarchy层次,如下图:

6)尺寸定义与设计检查:通过Floorplan > Specify Floorplan定义芯片与模块大小,芯片或模块大小有两种方式来指定,我根据Aspect Ratio,即给定利用率指定尺寸,由工具算出H和W,默认矩形,H×W即为面积,如下图所示:

(此外可通过Dimension定义尺寸,即直接指定H和W大小)

7)由于此lab是带IO的设计,需要指定Core2IO的间距(如果是模块级设计则需要指定Core2Die的间距),此时将IO和CORE之间的距离设为100μm,如下第一张图,设置完后Layout如下第二张图所示:

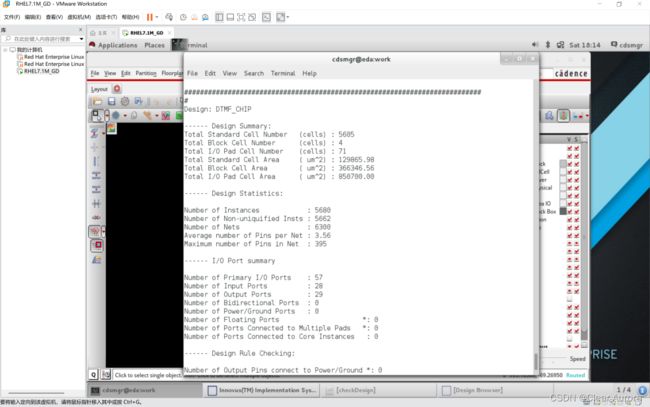

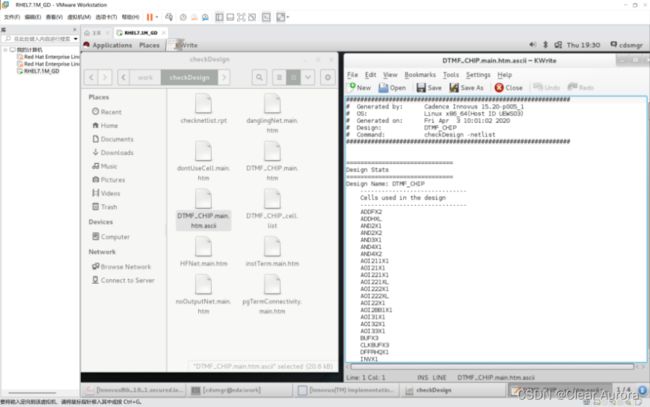

8)使用命令Check Design -netlist检查设计参考库以及netlist本身的问题,运行后在work/checkDesign/目录下生成了DTMF_CHIP.main.htm.ascii文件,是Check Design的详细信息,如下图:

2、电源路径设计(Routing Power with Special Route)

1)手动摆放macro,ip与halo,或执行File > Load > Floorplan选择dtmf_blocks.fp,完成后的Layout如下图所示:

2)更改PLLCLK网络的Placement Halo使之均为30μm,如下第一张图,改动成功后结果如下第二张图所示:

3)进行Powerplaning设计,加入电源环,设置参数如下第一张图所示,加入电源环后效果如下第二张图所示(红色与蓝色部分):

4)之后给PLLCLK网络加上电源环,选中PLLCLK后,基本参数设置与电源环形状设置如下两张图所示:

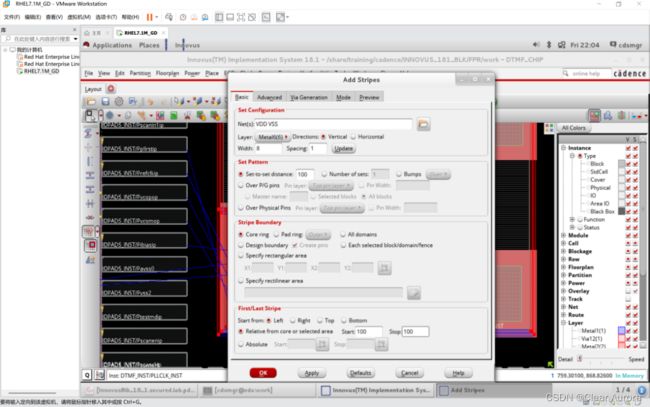

6)添加Power Stripe:Power > Power Planning > Add Power Stripe,将各参数设置如下图所示:

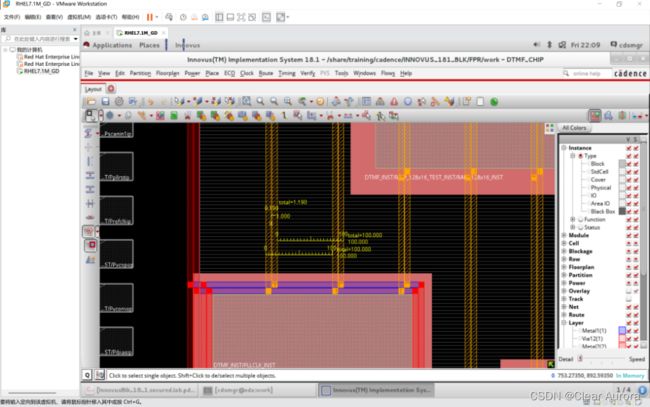

7)添加Power Stripe后,可见VDD与VSS间距为1微米,且VDD组间距、VSS组间距均为100微米,结果如下图:

8)摆放cell:Design Browser > 选中cell后 > q键指定坐标,参数如下图所示:

9)切换physical view即可看见这颗cell的坐标变化结果,如下图:

10)添加Power Rail并且和Power Stripe打孔:从M6打孔到M1(各层均打VIA),设置参数如下图所示:

3、使用Early Global Router分析路径(布线)可行性(Analyzing Route Feasibility with the Early Global Router)

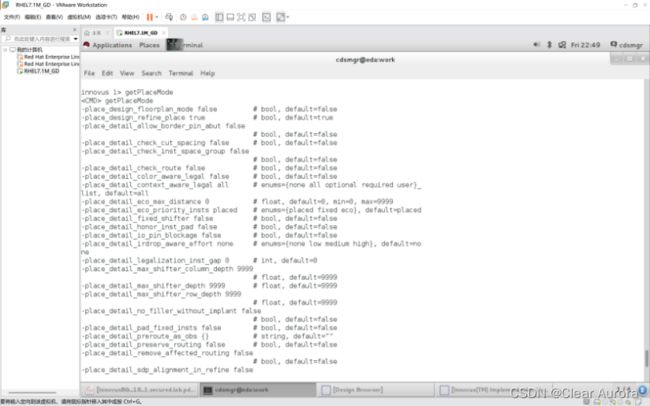

1)在命令行界面输入getPlaceMode后,输出了所有的PlaceMode如下图:

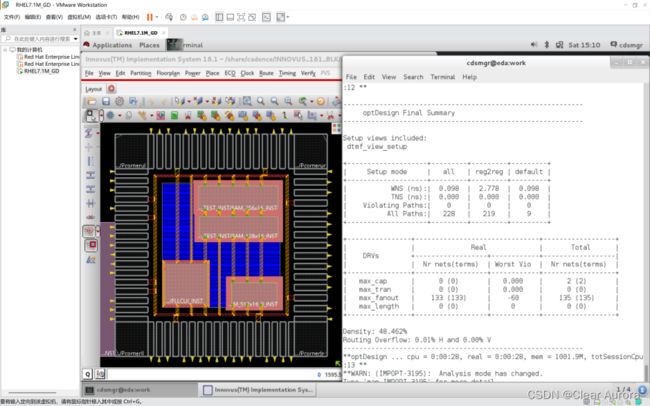

2)输入命令defIn scan_input.def,在Place之前读入scan chain的def进一步优化congestion,之后跑Placement命令place_opt_design,可得到Timing Report、DRV结果,以及整体Density的值为48.462%,Routing Overflow大小为0.01%H和0.00%V,如图:

3)输入指令defOutBySection -noNets -noComps -scanChains scan.def,显示Scan Chain连接示意图,也可直接操作:Place > Display > Scan Chain,如下图:

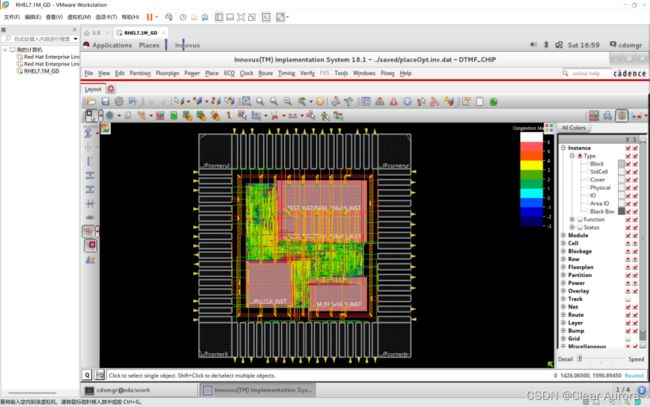

5) 输入指令restoreDesign ../saved/placeOpt.inv.dat DTMF_CHIP打开Placement后保存的数据,使用前期Global Router引擎分析潜在绕线问题:Route > Early Global Router,操作如下图所示:

6)可见垂直方向上存在Congestion,其中一条Congestion上绕线风险如图所示:

7)取消勾选垂直方向V的显示,去掉Congestion Label,可见设计均不存在Congestion了,如图:

8)使用命令saveDesign ../saved/earlyGlobalRouterByLiTianhao.inn保存设计,之后通过restoreDesign ../saved/earlyGlobalRouterByLiTianhao.inn.dat DTMF_CHIP可以打开设计。设计结果如图:

放大可查看具体布线情况,确保不存在绕线,如图:

三、补充问题:

四、作业:

1、Import Design读入数据后,执行checkDesign –netlist输出的结果关注要点:

Q1.Instance数:5680个,Block数:4个。

Q2.IO数:57个,其中Input数:28个,Output数:29个。

Q3.Standard Cell的面积:129865.98平方微米。

2、读入dtmf.fp后,确认如下信息:

Q1. pllclk这个Block的形状:长280微米,宽300微米,位置坐标:{355.28 355.44} (X-Y系)

Q2. CoreRing使用的Layer:Metal 5与Metal 6,宽度是:8微米。

Q3. Stripe使用的Layer:Metal 6,宽度是:8微米。

3、PowerPlan的操作要点(3个)

①先给整个芯片加上电源环后再选中BLOCK,给小的BLOCK加电源环;

②基本参数包括宽度等设置好后,还需注意设置电源环形状;

③添加Power Stripe后,须添加Power Rail并且和Power Stripe打孔。

4、Floorplan设计的注意事项(3个)

①如果lab是带IO的设计,需要指定Core2IO的间距(如果是模块级设计则需要指定Core2Die的间距);

②芯片或模块大小有两种方式来指定,我根据Aspect Ratio,即给定利用率指定尺寸,由工具算出H和W,默认矩形,H×W即为面积,此外可通过Dimension定义尺寸,即直接指定H和W大小;

③导入Floorplan设计时须使用命令Check Design -netlist检查设计参考库以及netlist本身的问题,运行后在work/checkDesign/目录下生成以.main.htm.ascii为后缀的文件,是Check Design的详细信息。

5、Lab 10 Place完成后Timing的确认:

Q1. Place之前的Timing确认:0.098纳秒,截图WNS的Slack:

Q2. Place之后的Timing确认:0.112纳秒,截图WNS的Slack: