verilog-实现按键消抖模块

文章目录

- 1.按键消抖原理

- 2.实现方案-状态机(Mealy型)

- 3.Verilog代码

-

- (1)高电平有效的情况

- (2)低电平有效的情况

1.按键消抖原理

轻触按键:相当于是一种电子开关,按下时开关接通,松开时开关断开,实现原理是通过轻触按键内部的金属弹片受力弹动来实现接通和断开。

说明: 如上图,产生的抖动次数以及间隔时间均是不可预期的,这就需要通过滤波来消除抖动可能对外部其他设备造成的影响。一般情况下抖动的总时间会持续20ms以内。这种抖动,可以通过硬电路或者逻辑设计的方式来消除,也可以通过软件的方式完成。其中硬件电路消除抖动适用于按键数目较少的场合。

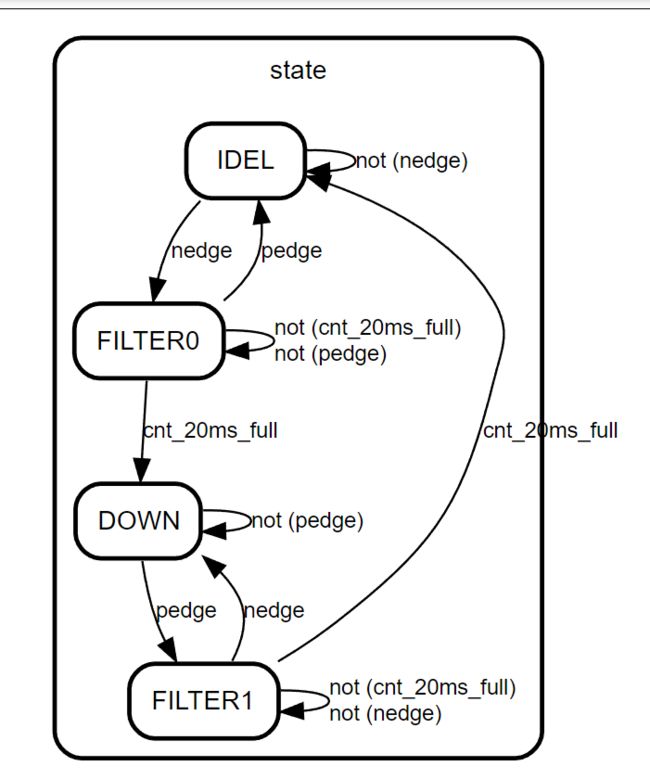

2.实现方案-状态机(Mealy型)

说明:

3.Verilog代码

**ps:**代码中涉及的脉冲边缘检测电路,可以看博主的文章:

脉冲边缘检测电路-verilog实现

(1)高电平有效的情况

高电平有效的Verilog实现//---------------------------------------------------

//高电平有效

//输出模板 o_key_flag && !o_key_state (一个脉冲)表示按下

module key1_filter_module(

input i_clk ,

input i_rstn ,

input i_key ,

output reg o_key_flag ,

output reg o_key_state

);

parameter

IDEL = 4'b0001,

FILTER0 = 4'b0010,

DOWN = 4'b0100,

FILTER1 = 4'b1000;

reg [3:0] state ;

reg [19:0] cnt_20ms ;

reg en_cnt_20ms ;//使能计数寄存器

reg i_key_a,i_key_b ;

reg key_tmp_a,key_tmp_b ;

reg cnt_20ms_full ;//计数满标志信号

wire pedge,nedge ;

//---------------跨时钟域处理,打两个拍子----------------//

always@(posedge i_clk or negedge i_rstn)

if(!i_rstn)

begin

i_key_a <= 1'b0;

i_key_b <= 1'b0;

end

else

begin

i_key_a <= i_key;

i_key_b <= i_key_a;

end

//-------------边沿监测电路----------------------------//

always@(posedge i_clk or negedge i_rstn)

if(!i_rstn)begin

key_tmp_a <= 1'b0;

key_tmp_b <= 1'b0;

end

else begin

key_tmp_a <= i_key_b;

key_tmp_b <= key_tmp_a;

end

assign nedge = !key_tmp_a & key_tmp_b ;

assign pedge = key_tmp_a & (!key_tmp_b);

//------------------------20ms计数器------------------//

always@(posedge i_clk or negedge i_rstn)

if(!i_rstn)

cnt_20ms <= 20'd0;

else if(en_cnt_20ms)

cnt_20ms <= cnt_20ms + 1'b1;

else

cnt_20ms <= 20'd0;

always@(posedge i_clk or negedge i_rstn)

if(!i_rstn)

cnt_20ms_full <= 1'b0;

else if(cnt_20ms == 999_999)

cnt_20ms_full <= 1'b1;

else

cnt_20ms_full <= 1'b0;

//----------------fsm-----------------------------

always@(posedge i_clk or negedge i_rstn)

if(!i_rstn)begin

en_cnt_20ms <= 1'b0;

state <= IDEL;

o_key_flag <= 1'b0;

o_key_state <= 1'b1;

end

else begin

case(state)

IDEL :

begin

o_key_flag <= 1'b0;

if(pedge)begin

state <= FILTER0;

en_cnt_20ms <= 1'b1;

end

else

state <= IDEL;

end

FILTER0:

if(cnt_20ms_full)begin

o_key_flag <= 1'b1;

o_key_state <= 1'b0;

en_cnt_20ms <= 1'b0;

state <= DOWN;

end

else if(nedge)begin

state <= IDEL;

en_cnt_20ms <= 1'b0;

end

else

state <= FILTER0;

DOWN:

begin

o_key_flag <= 1'b0;

if(nedge)begin

state <= FILTER1;

en_cnt_20ms <= 1'b1;

end

else

state <= DOWN;

end

FILTER1:

if(cnt_20ms_full)begin

o_key_flag <= 1'b1;

o_key_state <= 1'b1;

en_cnt_20ms <= 1'b0;

state <= IDEL;

end

else if(pedge)begin

en_cnt_20ms <= 1'b0;

state <= DOWN;

end

else

state <= FILTER1;

default:

begin

state <= IDEL;

en_cnt_20ms <= 1'b0;

o_key_flag <= 1'b0;

o_key_state <= 1'b1;

end

endcase

end

endmodule

`timescale 1ns / 1ps

module tb_key1_filter_module;

//port

reg i_clk = 1 ;

reg i_rstn = 0 ;

reg i_key ;

wire o_key_flag ;

wire o_key_state ;

key1_filter_module uut (

.i_clk (i_clk ) ,

.i_rstn (i_rstn ) ,

.i_key (i_key ) ,

.o_key_flag (o_key_flag ) ,

.o_key_state (o_key_state )

);

always #10 i_clk <= ~i_clk ; //50MHZ

initial begin

i_key <= 1;

#20 i_rstn <= 1;

#10_000_000;

i_key <= 0; #1000;

i_key <= 1; #2000;

i_key <= 0; #1400;

i_key <= 1; #2600;

i_key <= 0; #1300;

i_key <= 1; #200;

i_key <= 0; #30_000_000;

i_key <= 1; #2000;

i_key <= 0; #1000;

i_key <= 1; #2600;

i_key <= 0; #1400;

i_key <= 1; #200;

i_key <= 0; #1300;

i_key <= 1; #30_000_000;

end

endmodule

(2)低电平有效的情况

低电平有效的Verilog实现//---------------------------------------------------

//低电平有效

//输出模板 o_key_flag && !o_key_state (一个脉冲)表示按下

module key0_filter_module(

input i_clk ,

input i_rstn ,

input i_key ,

output reg o_key_flag ,

output reg o_key_state

);

parameter

IDEL = 4'b0001,

FILTER0 = 4'b0010,

DOWN = 4'b0100,

FILTER1 = 4'b1000;

reg [3:0] state ;

reg [19:0] cnt_20ms ;

reg en_cnt_20ms ;//使能计数寄存器

reg i_key_a,i_key_b ;

reg key_tmp_a,key_tmp_b ;

reg cnt_20ms_full ;//计数满标志信号

wire pedge,nedge ;

//---------------跨时钟域处理,打两个拍子----------------//

always@(posedge i_clk or negedge i_rstn)

if(!i_rstn)

begin

i_key_a <= 1'b0;

i_key_b <= 1'b0;

end

else

begin

i_key_a <= i_key;

i_key_b <= i_key_a;

end

//-------------边沿监测电路----------------------------//

always@(posedge i_clk or negedge i_rstn)

if(!i_rstn)begin

key_tmp_a <= 1'b0;

key_tmp_b <= 1'b0;

end

else begin

key_tmp_a <= i_key_b;

key_tmp_b <= key_tmp_a;

end

assign nedge = !key_tmp_a & key_tmp_b ;

assign pedge = key_tmp_a & (!key_tmp_b);

//------------------------20ms计数器------------------//

always@(posedge i_clk or negedge i_rstn)

if(!i_rstn)

cnt_20ms <= 20'd0;

else if(en_cnt_20ms)

cnt_20ms <= cnt_20ms + 1'b1;

else

cnt_20ms <= 20'd0;

always@(posedge i_clk or negedge i_rstn)

if(!i_rstn)

cnt_20ms_full <= 1'b0;

else if(cnt_20ms == 999_999)

cnt_20ms_full <= 1'b1;

else

cnt_20ms_full <= 1'b0;

//----------------fsm-----------------------------

always@(posedge i_clk or negedge i_rstn)

if(!i_rstn)begin

en_cnt_20ms <= 1'b0;

state <= IDEL;

o_key_flag <= 1'b0;

o_key_state <= 1'b1;

end

else begin

case(state)

IDEL :

begin

o_key_flag <= 1'b0;

if(nedge)begin

state <= FILTER0;

en_cnt_20ms <= 1'b1;

end

else

state <= IDEL;

end

FILTER0:

if(cnt_20ms_full)begin

o_key_flag <= 1'b1;

o_key_state <= 1'b0;

en_cnt_20ms <= 1'b0;

state <= DOWN;

end

else if(pedge)begin

state <= IDEL;

en_cnt_20ms <= 1'b0;

end

else

state <= FILTER0;

DOWN:

begin

o_key_flag <= 1'b0;

if(pedge)begin

state <= FILTER1;

en_cnt_20ms <= 1'b1;

end

else

state <= DOWN;

end

FILTER1:

if(cnt_20ms_full)begin

o_key_flag <= 1'b1;

o_key_state <= 1'b1;

en_cnt_20ms <= 1'b0;

state <= IDEL;

end

else if(nedge)begin

en_cnt_20ms <= 1'b0;

state <= DOWN;

end

else

state <= FILTER1;

default:

begin

state <= IDEL;

en_cnt_20ms <= 1'b0;

o_key_flag <= 1'b0;

o_key_state <= 1'b1;

end

endcase

end

endmodule

`timescale 1ns / 1ps

module tb_key0_filter_module;

//port

reg i_clk = 0 ;

reg i_rstn = 0 ;

reg i_key ;

wire o_key_flag ;

wire o_key_state ;

key0_filter_module uut (

.i_clk (i_clk ) ,

.i_rstn (i_rstn ) ,

.i_key (i_key ) ,

.o_key_flag (o_key_flag ) ,

.o_key_state (o_key_state )

);

always #10 i_clk <= ~i_clk ; //50MHZ

initial begin

i_key <= 0;

#20 i_rstn <= 1;

#10_000_000;

i_key <= 1; #1000;

i_key <= 0; #2000;

i_key <= 1; #1400;

i_key <= 0; #2600;

i_key <= 1; #1300;

i_key <= 0; #200;

i_key <= 1; #30_000_000;

i_key <= 0; #2000;

i_key <= 1; #1000;

i_key <= 0; #2600;

i_key <= 1; #1400;

i_key <= 0; #200;

i_key <= 1; #1300;

i_key <= 0; #30_000_000;

end

endmodule

本文来自参考:小梅哥的设计方案

https://www.bilibili.com/video/BV1KE411h7AZ?p=8&vd_source=696332c534453c3966f51e8e54ca6453

本篇随笔为学习记录所用,如有侵权,请联系博主。