AMD 自适应和嵌入式产品技术日

概要

时间:2023年11月28日

地点:北京朝阳新云南皇冠假日酒店

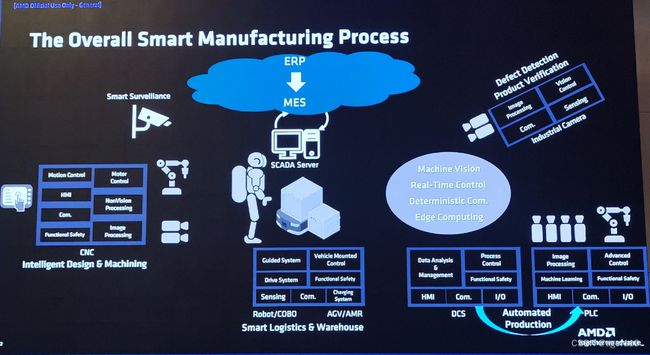

主题内容:AMD自适应和嵌入式产品的更新,跨越 云、边、端的AI解决方案,赋能智能制造的机器视觉与机器人等热门话题。

注:本文重点关注FPGA,SoC相关的产品和技术,对于CPU,GPU产品和技术大多数都是直接略过哈。

会议的议程:

AMD在各行业的创新

1:新器件发布

1.1: 最大规模的逻辑器件——Versal Premium

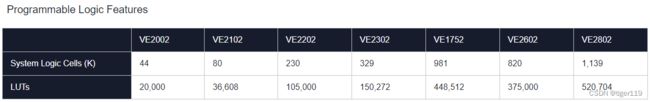

这自然是会议的重中之重,Versal Premium VP1902 发布,逻辑容量,Serdes数目,计算能力是VU19P的2倍。5.6kk 规模,汗,国内现在还没见到500K的(正式量产的)

Xilinx FPGA最大逻辑规模又突破了一大步!

1.2: Versal Prime 系列

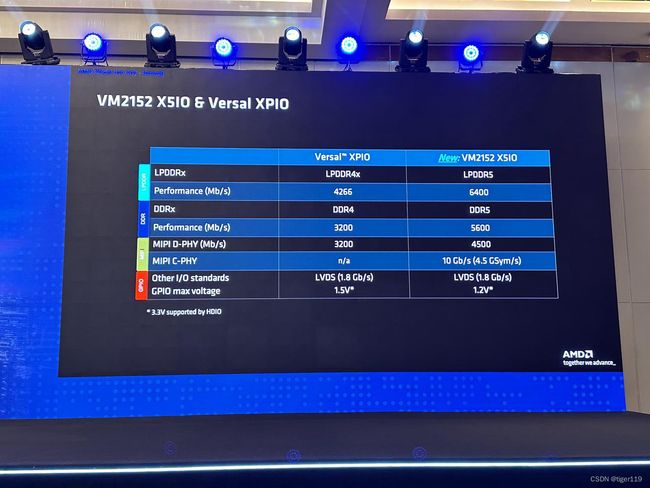

Versal Prime VM2152,第一款XPIO支持DDR5和MIPI C-PHY的Versal芯片,其中DDR5速率可达5.6Gbps,LPDDR5速率可达6.4Gbps

MIPI D-PHY速率可达4.5Gbps,C-PHY速率可达10Gbps,LVDS可达1.8Gbps

1.3: 受限低价系列的产品也有推出。

-- Artix UltraScale+ 家族最小的AU7P(80K)

-- ZYNQ UltraScale+ ZU3TCG/EG,150KLUT规模,带8个Serdes,与ZU3CG比,加入了8对Serdes和14M的Uram,DSP的数量也多了1.6倍;

-- 明年会发布16 nm的低成本,低功耗的SPARTAN UltraScale+ 系列,Serdes IO最高可支持25Gbps

1.4: Kria K24 SOM 开发模块(System-on-Module)

主要用于电机控制和数字信号处理;

1.5: Versal系列的芯片跨越了云,通讯(RF),边缘,端

Versal 系列的芯片,全部是SoC的,没有纯FPGA的芯片。

理解一下HBM,Prime,Preminu的区别:

Prime是最广泛,最通用的场景使用。

Preminum是高级的片子,逻辑单元多,适合于处理更复杂的运算。

HBM 因为是对内存的访问量大,快速。应该是适用于内存要求高,带宽要求高的场景。

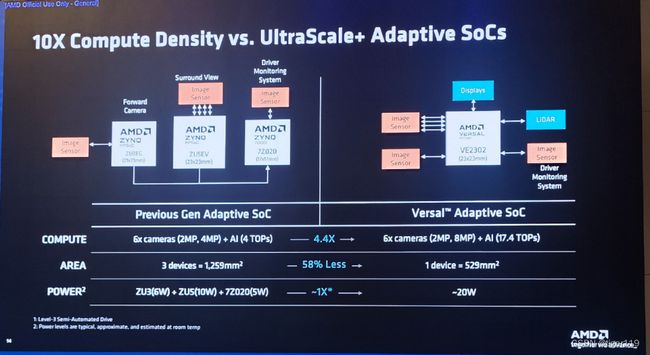

1.6: 芯片在车硅行业的布局:

2:无处不在的AI

2.1: 丰富的产品组合,满足不同的AI需求。

2.2: GPU的解决方案(CNDA & RDNA)

GPU的解决方案,可以转换到NV的方案。

2.3: CPU的解决方案(RDNA)

必须要强调一下新款的Ryzen CPU for PC,可以使用 AMD Rezen AI ,AIE集成到CPU的应用。

支持开源大模型

以Ryzen AI 7840HS系列的芯片为例,凡是搭载了这款芯片的笔记本电脑,都具备了AI功能,可以快速在笔记本上部署开源的大模型应用,完成大模型的推理部分的应用(训练当然是不可能的,推理也有限制,现场演示的是 chatglm2-6b 的模型),而且,这款芯片也集成了Radeom显卡,可以处理一些图像,多媒体。

2.4: SoC的AI 边缘计算解决方案(XDNA)

包括AIE,ARM,FPGA 的Soc产品,在边缘计算中。

看一下AI 边缘计算用到的芯片,逻辑单元的数量实际上是很小的。主要的能力是在AIE和DSP的能力。针对性非常的强。

2.5: 生态,软件模型层,AMD计算平台

3:行业应用

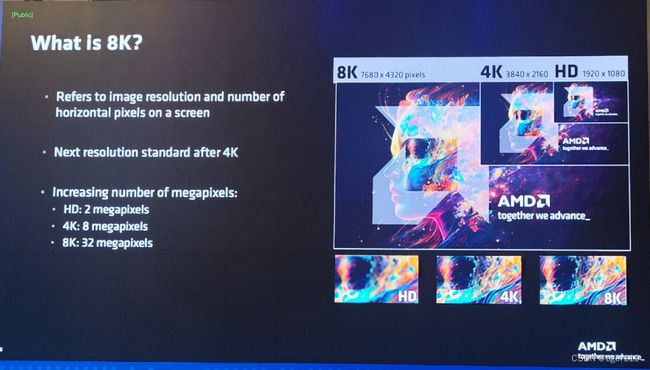

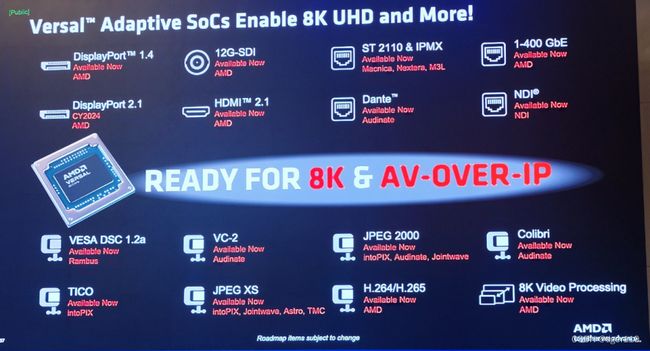

3.1: 针对8K视频处理

实际上就是必须使用更高速的接口,如上。

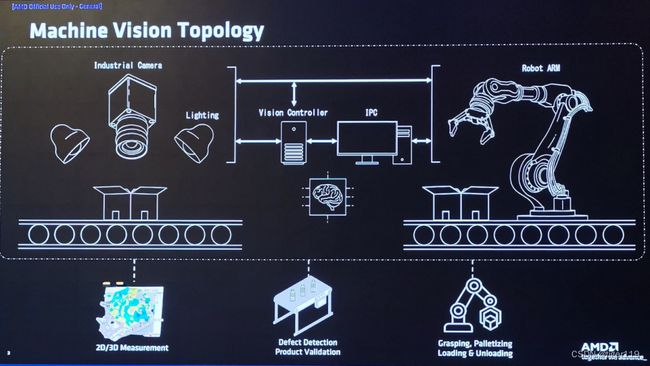

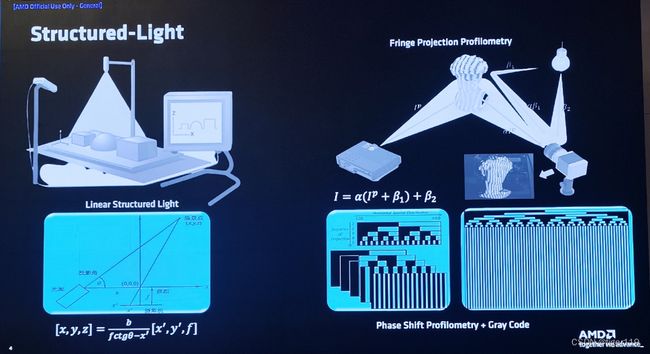

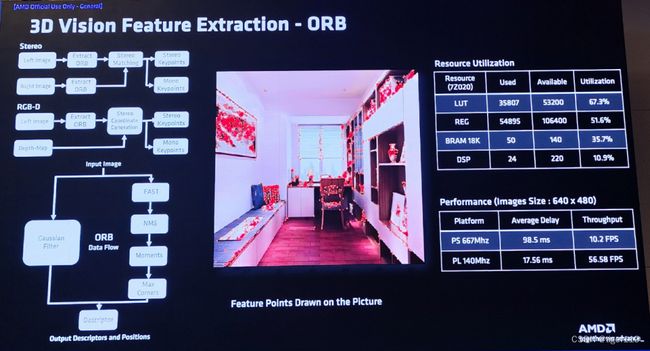

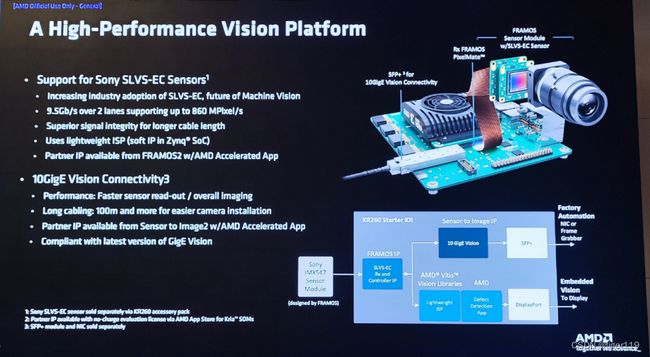

3.2: 机器视觉与机器人

现场有展示工业相机,就是机器视觉的一个案例,涉及到智能制造和机器视觉的应用很多,从上面可以看到,这里就不一一介绍了,后续有机会,逐个分析一下相应的应用点。

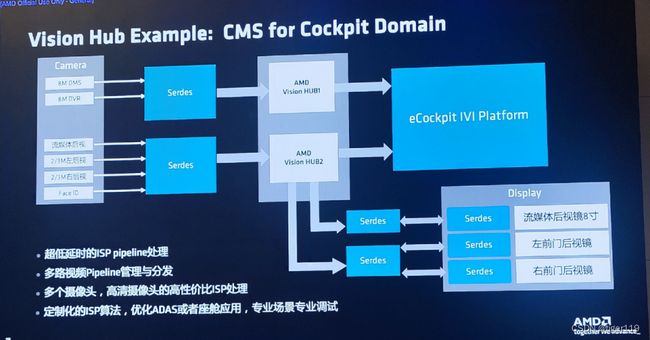

3.3: 沉浸式座舱解决方案

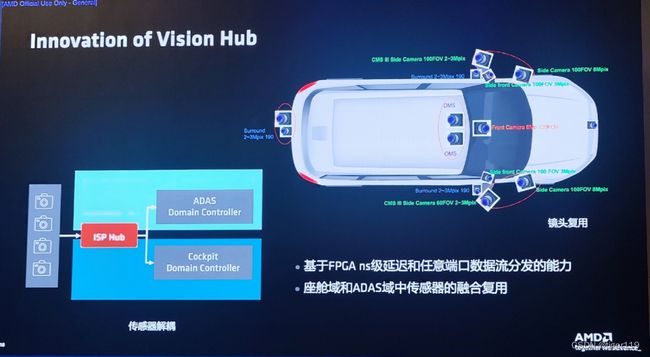

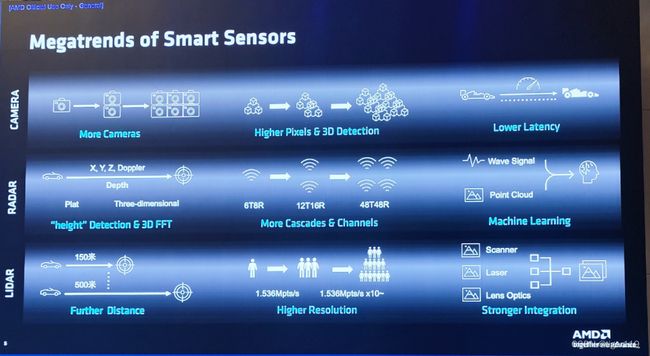

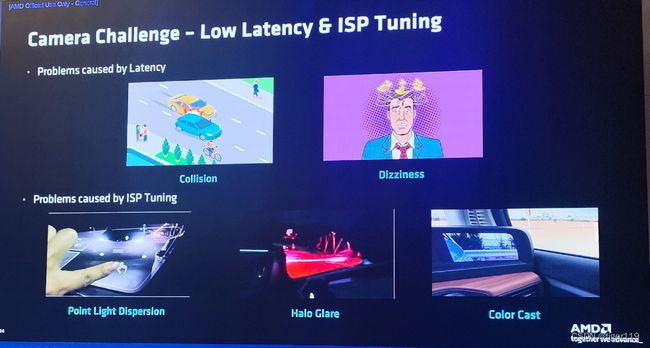

3.4: 汽车智能传感器——自动驾驶

首先是传感器

同时,也可以通过3D视觉的方式,通过检测来感知。当然,对于时延要求会很高。

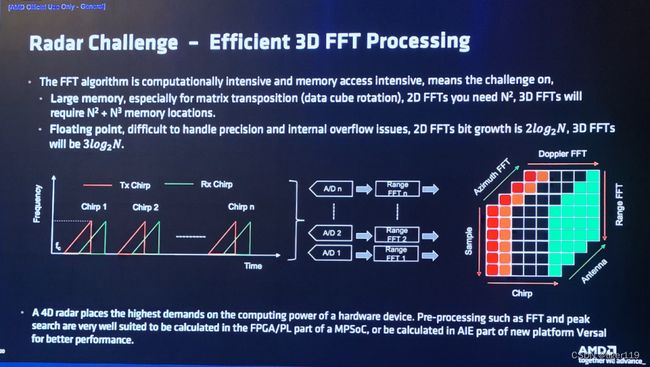

还有雷达算法非常复杂,需要有大量的处理,3D FFT

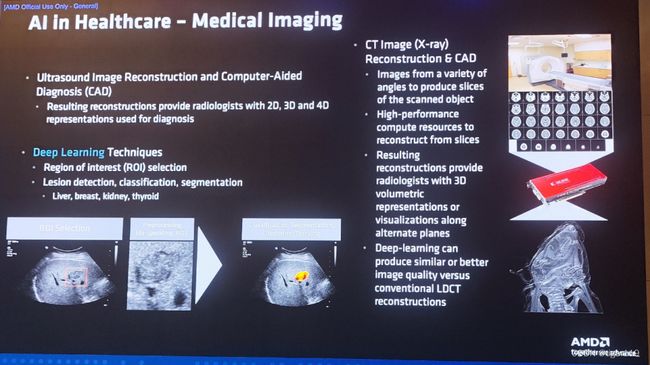

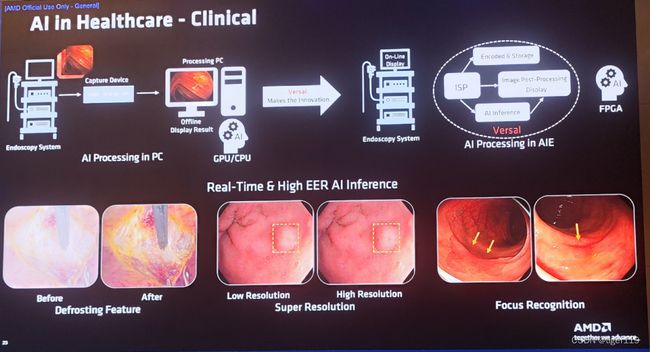

3.5: 医疗影像中的应用

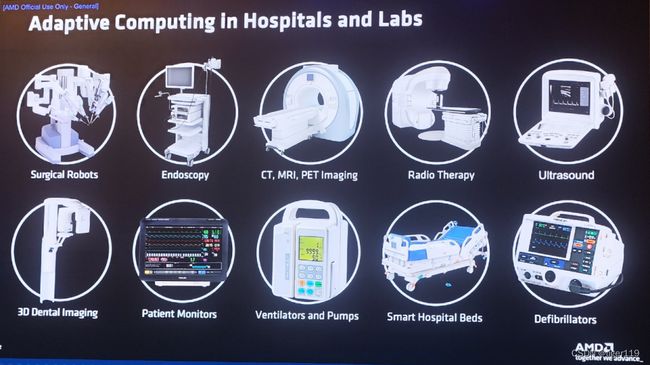

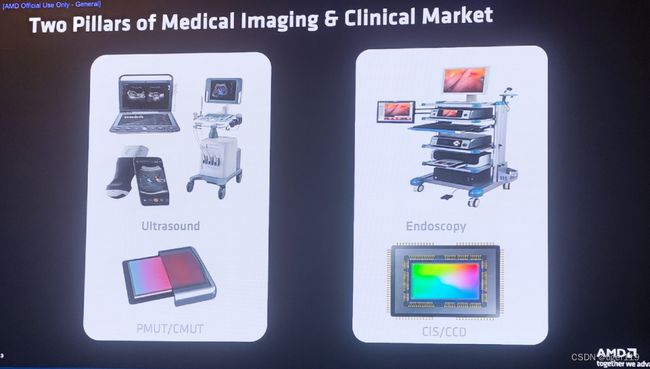

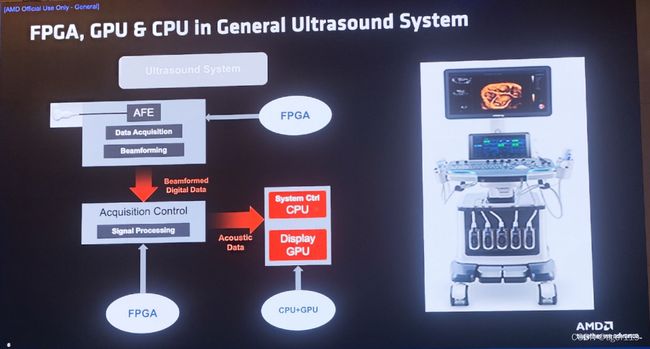

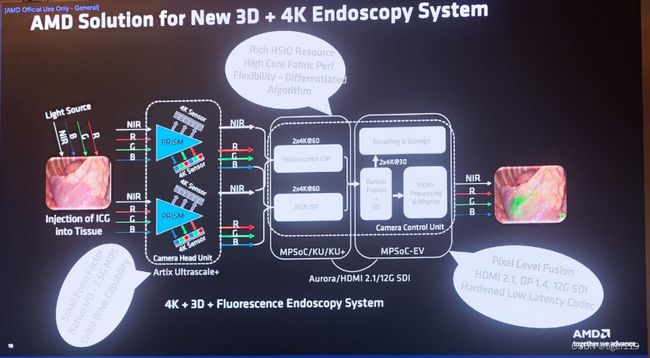

手术机器人、内窥镜、超声,AMD都是NO1,CT/MRI/PET 与东软、联影都有合作;3D牙科成像、监护增长也比较快。

工业相机、监控的厂家也会进入来做内窥镜

图像处理、分割、目标选择、器官分类;超声图像呈现,提升CT 3D图片的质量

AI去雾算法,,超分处理(提升分辨率),识别与分类

3.6: 其它

在现场,其实还看到一些其它展品,具体原理不说了,这里只是列出来,后面再分析

4:设计与开发

4.1: Versal Soc架构的先进性

PMC —— 生命周期管理,这个相应的功能有增强吗?不清楚

添加双arm核,主频应该有所增强。

逻辑容量的提升,主要原因是制程是7nm,

AIE 和 DSP 的增强

AIE 的运算能力,吞吐最有增强,并对 ML 有优化。

DSP Engine的运算力有增强

针对AIE的编程——C++ 编码,也可以基于已有模型直接转换。

使用Noc来进行通讯——带宽最大,布局/布线更简单。

可使用的内存更加丰富——

以太网络的速度更高——600G

两种PCIe可选

高速的Transceivers

I/O 可骗程度更高

PDM——电源管理

更好的支持 硬件/软件/数据 开发人员

4.2:Versal Soc 硬件设计

硬件设计,主要是使用Vitis,对各种硬核 IP进行配置。

创建工程:

Noc的配置

Memory Controller的配置

CPM的设计

网络的设计

DSP的设计

clock的设计

内存设计

Select IO的设计

Transceiver的设计

4.3: Versal Soc 软件设计

软件开发包括:SoC的开发配置,加速应用处理,AI模型开发

如何搭建平台:

对于软件开发这一节,我觉得没有讲什么真正的软件开发,还是在介绍架构和原理居多。

4.4: Vitis 新版

Vitis 新版,实际上就是做了一些架构和打包上的改造,好象并没有什么功能上的大的突破性的变化。

原有安装包做了瘦身。

之前是三个IDE。

嵌入式软件开发包

前端:eclectron 这是一个流程的开源框架,可以通过html+JS 来构建桌面应用,内核基于chrome。最新桌面应用很多都是使用eclectron,因为开发周期短,技术栈通用。

框架:Eclipse Theia 基于Web的IDE,高度模块化,兼容VS Code插件,完全开源。编码:TypeScript,Node.js 和 React。IDE定制。

项目元数据:JSON 流程的web数据交换的格式定义,与web对象兼容。

硬件元数据:System Device Tree 描述设备和设备间关系。硬件信息,如:CPU,内存,外设接口,I/O设备,中断和地址映射等……

版本管理:Git 代码仓和版本管理

命令接口:Python 最通用的脚本/解释型语言

-

后端的变化

System Deive Tree: 使用SDT传递数据到VITIS

Lopper Framework: 解析,提取,修改,可脚本化和自动化,支持SDT。

Base Address : 基于地址来访问硬件设备,简化和提效。更直接的硬件访问。

YAML:软件配置,硬件描述。更易读,简洁,更容易编辑。(通用于容器化技术中docker,k8s,CI/CD)

CMake: 驱动,库,应用程序模板使用cmake来构建,标准的软件工程实践,提供更好的跨平台的支持,更灵活的项目配置维护/管理,提升开发效率和项目管理的灵活度。

由上可见,Vitis unified 版本的变化:

-

更小的可配置开发包,更灵活(之前的太臃肿)

-

前端IDE到语言更多使用开源方案,扩大生态,提供开发生态的接入

-

底层格式采纳更通用的标准格式,更灵活,扩展性更好

-

构建系统和项目管理方式借鉴软件行业的规范,提升效率。

4.5: vivado 新功能

这块儿的内容,实际上我没有听,因为时间原因,当天要从北京离开,需要去赶高铁。

PS:对于行业专场,我是从同事那里获得的信息,因为下午和技术开发场冲突。