电平设计基础:LVDS&CML 电平

一,LVDS逻辑电平

LVDS :低电压差分信号(Low-Voltage Differential Signaling)是美国国家半导体(National Semiconductor, NS)于1994年提出的一种信号传输模式的电平标准,它采用极低的电压摆幅高速差动传输数据(采用CMOS 工艺的低电压差分信号器件),实现点对点(或则点对多:M-LVDS)的连接,具有低功耗、低误码率、低串扰和低辐射等优点,已经被广泛应用于串行高速数据通讯场合当,如高速背板、电缆和板到板数据传输与时钟分配,以及PCB内的通信链路。

LVDS 器件的传输机制是把 TTL 逻辑电平转换成低电压差分信号,以便于高速传输。与传统的 ECL逻辑相比,它采用 CMOS 工艺,其电压摆幅更低(LVDS只有 400mV,ECL 为 800mv),动态功耗更小(输出电流 3~5mA,只有 ECL 电路的 1/7),低 EMI,价格更低,因而在中等频率(几百M~几GHz)差分信号应用上具有较大的优势。

——LVDS技术规范有两个标准,即TIA(电讯工业联盟)/EIA(电子工业联盟)的ANSI/TIA/EIA-644标准(LVDS也称为RS-644接口)与IEEE 1596.3标准。

1,LVDS基本电路结构

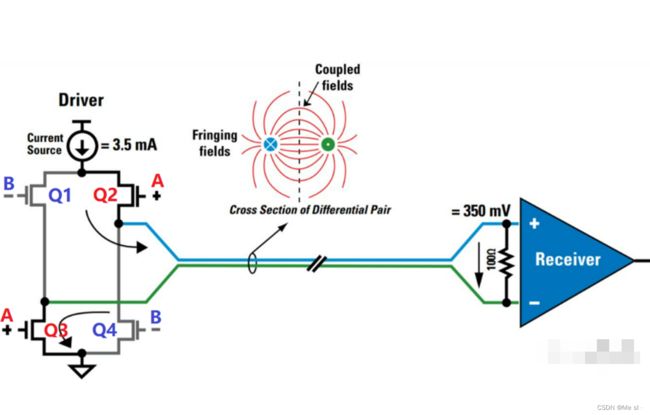

如下图所示为典型的基本LVDS电路,采用一对差分信号线传输数据;通过驱动3.5mA的稳定电流源,以350mV低振幅(100Ω终端匹配)的差动信号来高速传送数据。其数据传输速度在规格内限定最大为655Mbit/秒,但这并不是极限值。通过各半导体厂商改进,可以实现3Gbit/秒左右的高速传输速度。

1. LVDS的输出端驱动是一个3.5mA的电流源,并由两组MOS管(4个)组成一对发送输出;

2. 当A+导通,B-断开时:

1, 电流从右上角Q2(A+ MOS管)驱动出到蓝色传输线,即右上A+ MOS管电流方向是:电流源(Driver)à右上A+ MOS管à蓝色传输线à100Ω终端电阻;

2, 左下角Q3(A+ MOS管)驱动接至GND,所以此时电流从绿色传输线通过左下角Q3流出到GND;左下A+ MOS管电流方向是:GNDà左下A+ MOS管à绿色传输线à100Ω终端电阻;

3, 整个电流通路最终电流在100Ω终端电阻侧导通,并形成输出电压:3.5mA *100Ω = 350mV。

——因为传输线提供的100Ω阻抗是交流阻抗(只在信号边沿有用的阻抗,忘记的胖友们务必复习《从电感、电容到理想传输线》相关章节),对于直流来说是传输线是高阻抗,所以终端必须有100Ω端接电阻来提供信号固定电平状态下的回流,以保证输出电压;

——需要再次强调的是:3.5mA电流从电源源流出到蓝色传输线,和绿色传输线3.5mA电流流入GND,这两者同时发生的,才能保证信号边沿的同步;驱动电流的路径并非是:电流源àQ2à蓝色传输线à100Ω终端电阻à绿色传输线àQ3àGND(有点违反直觉哈,胖友们务必回顾“传输线”相关理论)。

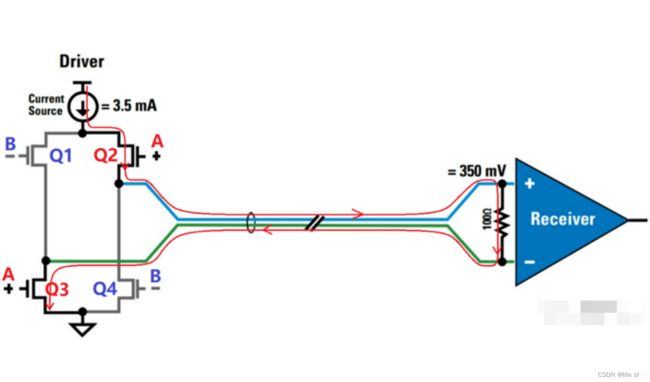

3. 当B-导通,A+断开时:

1, 此时3.5mA驱动电流从左上角Q1(B- MOS管)流出,并流入绿色传输线;

2, 同时蓝色传输线电流流入右下角Q4(B- MOS管);

——具体电流传输的方向,如上。

3, 电流通路最终电流还是在100Ω终端电阻侧导通,但是电流方向与“A+导通,B-断开”相反,并形成反向的输出电压:-3.5mA *100Ω = -350mV。

4. 最终在输出端形成 +350mV和-350mV信号摆幅的差分输出。

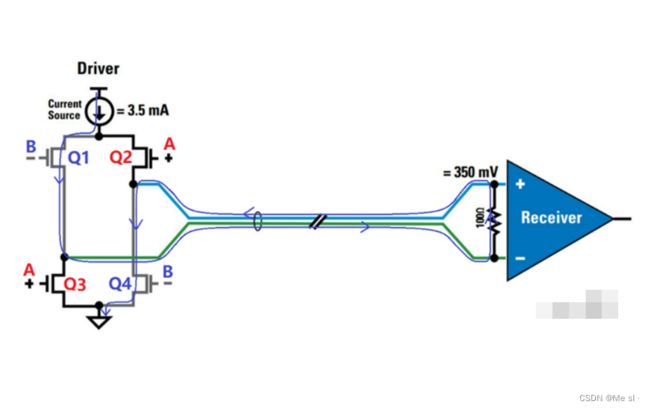

——在一本非常优秀的“信号完整性”相关书籍中,作者认为LVDS是伪差分线,因为从LVDS驱动机制来说,它只需要驱动3.5mA电流流过终端100Ω电阻形成的压差来实现,似乎并不需要一定是对耦差分线;但通过上述两条传输线的电流路径分析,我觉得LVDS应该是真正的对耦差分线。

2,LVDS电平分析

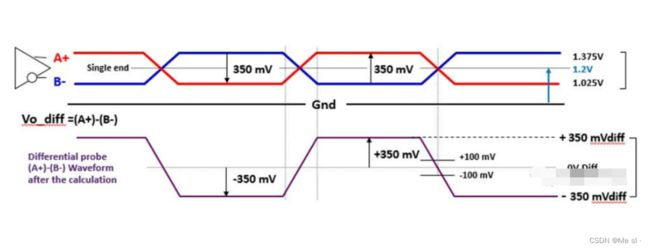

LVDS的差分信号的两根差分信号线:正电极信号(A+)和负电极信号(B−);共模偏置电压为:1.2V,差模电压摆幅是:350mV。如果我们用示波器来测试信号波形,并对两个信号电压值取差:(A+)−(B−);那么我们可以得到差分摆幅为:-350mV和+350mV。具体波形如下图所示。

上述波形是理想的情况,如下所示为器件资料(Intel® Stratix® 10 Device)中关于LVDS相关参数的描述;其输出共模电压(VOCM)和差模电压(VOD)的具体规格如下蓝色框内所示;如果要正确接收其它器件发送过来的信号,必须满足红色框内关于输入共模电压(VICM(DC))和差模电压(VID)的参数要求。

3,LVDS电平特点

LVDS 的特点是电流驱动模式,低电压摆幅 350mV 可以提供更高的信号传输速率,使用差分传输的方式可以减小信号和噪声的EMI辐射:

1. 输出电平切换不需要设计类似TTL/CMOS的“死区时间”,可以支持更高速率;

——由于是电流驱动,所以不需要防备电压源直接接地的风险。

2. 低输出电压摆幅(350mV)):

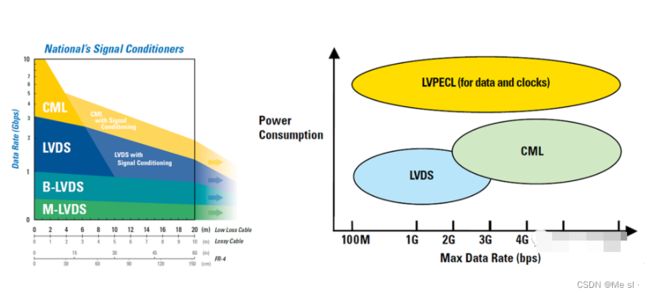

1, 可以支持更高速率(1Gbps以上),具体支持速率对比如左下图所示;

2, 功耗消耗更低(如右下图所示),内部散热更小,有助于提供芯片集成度。

3. 低EMI电磁辐射:

1, 低的信号边缘变化率:dV/dt = 0.350V/0.5ns = 0.7V/ns;

——如下图所示,虽然速率高(ps级别),但是由于摆渡小所以边沿变化率要求不高。

2, 耦合差分信号线的电磁干扰相互抵销,对外辐射小;

3, 耦合差分信号线抗电磁干扰性强。

4. 允许输入的共模电压范围大,支持1V的共模偏置电压差(如上图所示);

5. 传输线匹配简单。

——无论是使用电缆还是PCB走线,LVDS的高速信号传输都必须考虑阻抗匹配问题:阻抗不连续或终端不匹配会影响传输信号;所以需要控制传输线阻抗,并保证合适的端接。

1, 对于点到点的链路(LVDS),如下图所示,只需要使用100Ω端接在距离驱动器最远处;

——如果输出端和输入端共模偏置电压不匹配(或考虑上电时序的漏电影响),则需串接100nF电容器进行AC耦合,AC耦合电容器对信号传输影响不大(相当于短路,胖友们可以动手算一算:100nF电容器在100MHz频率时的阻抗是多少~)。

2, 对于多分支总线(M-LVDS),如果驱动器在总线的一端,则可采用相同的端接方法(即,在距离驱动器最远端端接100Ω电阻,如下图所示);否则需要端接总线的两端。

——M-LVDS可以实现点对多,而且长距离的传输(如下左图所示),与RS-485总线的应用有明显重叠;两者参数对比如下右图所示,有兴趣的胖友可以自行学习;本章不对M-LVDS和RS-485展开分析。

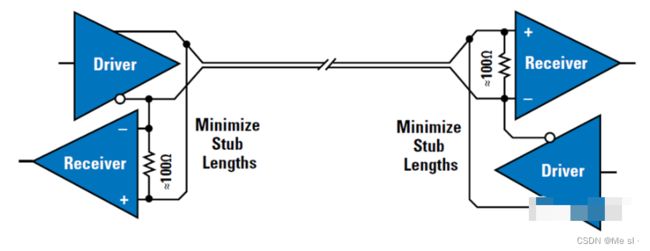

3, 如下图所示,还有一种多点拓扑是:“半双工”拓扑;它由两个驱动/接收对组成,在单个互连上传输和接收两个点之间的信号。

4,LVDS电路设计

对于LVDS PCB的设计来说,不论LVDS信号对数量是多少,都建议使用多层板,最少四层设置: LVDS、GROUND、POWER、TTL。

1. 对 LVDS 信号和其它信号(举个栗子,TTL 信号;避免受到干扰),最好能使用不同的走线层,如果因为设计限制必须使用同一层走线,LVDS 和 TTL 的距离应该足够远,至少应该大于 3~5 倍差分线间距;

2. 保证收发器到接插件的距离足够短,防止由于 Stub 线过长引起信号的崎变,一般要求距离小于 10mm;

3. 对收发器的电源使用滤波电容,滤波电容的位置应该尽量靠近电源和地管脚,滤波电容其的容值参照器件手册;

——如果没有推荐滤波电容器值,那么可以按照1个uF级电容(举个栗子:10uF)+每个管脚1个100nF电容的经验值进行设计。

4. 对电源和地管脚与参考平面的连接应该使用短和粗的连线连接,同时使用多点连接;

——参考《电源完整性》相关章节,主要为了减小寄生电感。

5. 对走线的阻抗要求进行控制,一般差分阻抗控制在 100 欧姆;

——匹配电阻的阻值可以进行调整,根据差分线阻抗和输出差模电压范围来决定。

6. 对走线方式的选择没有限制,微带线和带状线均可,但是必须注意有良好的参考平面。对不同差分线之间的间距要求间隔不能太小,至少应该大于 3~5 倍差分线间距;

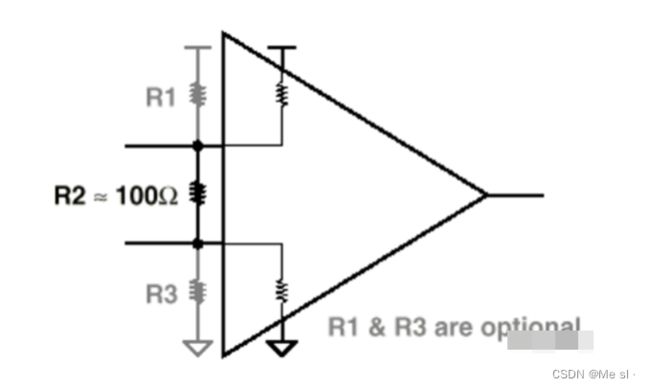

7. 对接收端的匹配电阻到接收管脚的距离要尽量的靠近(一般小于 7mm,最大不能超过 12mm); 未使用的输入管脚可以悬空,如下图所示;

8. LVDS 在电缆中的使用同在 PCB 中的使用方式并无大的差别,需要注意在不同电缆中 LVDS 差分信号需要不同的排布方式,如下图所示;

——电缆本身的插损需要满足支持该频率高速信号传输,举个栗子:屏蔽双绞线比较适合作为 LVDS 传输的介质,CAT3 电缆可以传输 5m,CAT5 电缆可以传输更远距离的 LVDS 信号。

二,CML逻辑电平

CML:电流模式逻辑(即Current Mode Logic),电路主要靠电流驱动,也是所有高速数据接口形式中最简单的一种,它的输入与输出的匹配集成在芯片内部,基本不需要外部端接,从而使单板硬件设计更简单、更简洁。由于CML电路内部三极管同ECL一样工作在非饱和状态,逻辑翻转速率极高,相比于LVDS要快很多;所以CML电平一般被用于高速SerDes链路(举个栗子:光模块接口SerDes总线)。

从标准规范来说,CML电平也没有统一的国际标准。

——ECL,CML都没有统一的国际标准,只有LVDS有国际标准,所以电平互连上需要特别注意检查是否匹配。

1,CML基本电路结构

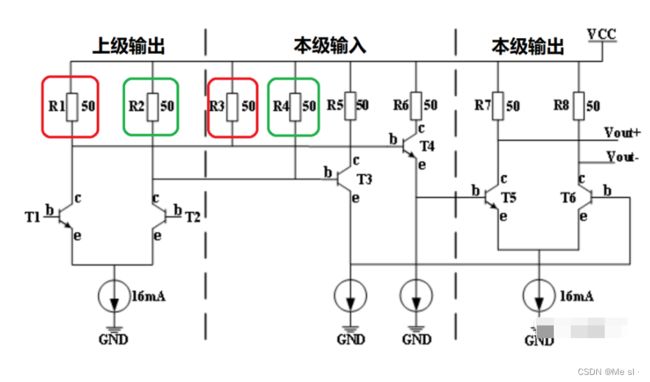

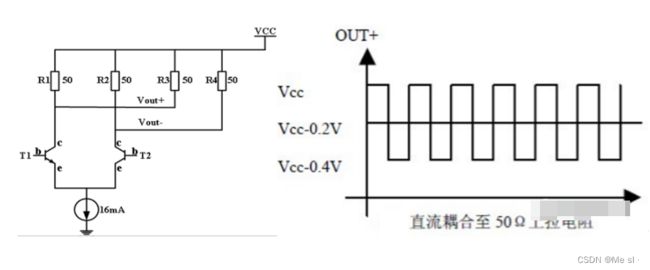

CML电路如下图所示分为:本级输入和本级输出两部分;

1. 输入电路是一对射极跟随器后跟一个差分放大器:射极跟随器起到隔离,增加驱动能力的作用,上拉的50Ω电阻是为了保证与前级输出电路形成阻抗匹配;

2. 当输入为高电平时,即T3管为N端,T4管为P端,当P大于N时即输入为高电平:当接收为高电平时T5导通、T6截止,16mA电流均从T5流过,此时CML输出为低电平;

——当输入为低时情况类似,所以CML输入输出存在倒相的关系。

3. 输出电路是一个差分对,如上图“本级输出”所示:该差分对的集电极电阻为50Ω,输出信号的高低电平切换是通过共发射极差分对的开关控制的,差分对的发射极到地的恒流源典型值为16mA;

1, 当CML输出直流耦合至50Ω上拉电阻负载时(如下左图R1、R3和R2、R4同时上拉50Ω),所以输出端差分对中的三极管T1和T2同时只能导通一个;

(1)首先进行静态分析:由于T1、T2参数对称,故16mA电流平均流过T1、T2,每个管流过8mA的电流,分到R1~R4四个电阻上,每个电阻流过的电流为4mA,所以直流耦合时的共模电压为:Vc = Vcc – 4mA*50Ω = Vcc -0.2V;

(2)当有差模电压输入时:T1、T2只会导通一个(以T1导通为例),16mA电流由R1、R3一起提供,每个电阻提供8mA电流,因此单端摆幅为:Vswing = 8mA * 50Ω = 0.4V;

——当负载为50Ω上拉电阻时,输出信号线上总共上拉电阻为50Ω//50Ω = 25Ω,所以计算导通三极管的集电极电阻上的压降为:16mA*25Ω = 0.4V。

(3)如上可知共模电压为:Vcc-0.2V,而差模电压为:0.4V,所以CML单端输出信号为以Vcc-0.2V为中心,摆幅为0.4V的信号,即单端信号摆幅为:Vcc~(Vcc-0.4V),其输出波形如下左图所示;

——在这种情况下差分输出信号摆幅为800mV:差分电压分别为-400mV和+400mV,摆幅为它们之和。

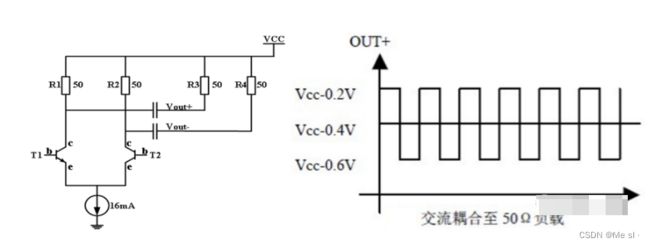

2, 当CML输出交流耦合至50Ω上拉电阻负载时(如下左图R1、R3和R2、R4同时上拉50Ω),所以同样输出端差分对中的三极管T1和T2同时只能导通一个;

(1)首先进行静态分析:由于电容器的隔直作用,R3和R4不能向T1、T2提供直流电流,因此16mA电流平均流过R1、R2,每个电阻流过8mA的电流,所以交流耦合时的共模电压为:Vc = Vcc – 8mA*50Ω = Vcc -0.4V;

(2)当有差模电压输入时(同直流耦合一样):T1、T2只会导通一个(以T1导通为例),16mA电流由R1、R3一起提供,每个电阻提供8mA电流,因此单端摆幅为:Vswing = 8mA * 50Ω = 0.4V;

(3)如上可知共模电压为:Vcc-0.4V,而差模电压为:0.4V,所以CML单端输出信号为以Vcc-0.4V为中心,摆幅为0.4V的信号,即单端信号摆幅为:(Vcc-0.2)~(Vcc-0.6V),其输出波形如下右图所示。

——在这种情况下差分输出信号摆幅同样是800mV:差分电压分别为-400mV和+400mV,摆幅为它们之和。

2,CML电平分析和匹配

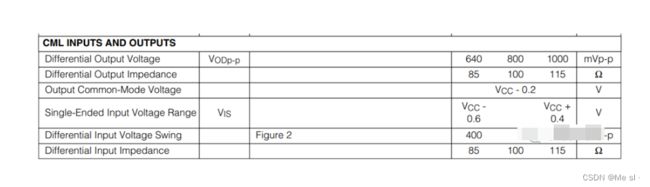

上一节我们已经从理论层面了解了CML电平的理想电压值,如下图所示为Maxim MAX3831器件的CML电平规格;除了有对单端、差分信号的具体定义之外,还有对阻抗进行了定义(精度15%),CML逻辑电路无需外部提供电路阻抗匹配(只需直连或AC耦合直连),这是因为CML输入端内部电路已经做了终端并联匹配:单端输入50Ω上拉至Vcc;那么我们就知道差分信号线之间的阻抗为100Ω。所以在传输线设计时需保证:单端50Ω,差分100Ω的传输线阻抗设计(松耦合差分线)。

——终端并联匹配是否必须要接至GND?单端50Ω时差分就必然是100Ω么(单端阻抗与差分阻抗是否有关系)?或则说什么情况下单端50Ω,差分会小于100Ω?关于这些问题,忘记的胖友们请继续复习《从电感、电容到理想传输线》和《特殊的串扰-差分信号》相关章节,相信能给你个满意的答案。

由于CML电平没有任何标准,从而出现了很多供应商自行制定的规范,因此胖友们在使用CML电平时一定要仔细查阅芯片手册(后续在《硬件开发流程基础:详细设计》相关专题中会介绍,如何保证单板上各器件之间的电平匹配)。

说到这里,突然想起一个事情来:我最早接触高速串行链路时会将SerDes和CML/LVPECL/LVDS逻辑电平的概念搞混掉。我们在使用串行链路时,经常会用SerDes指代高速串行链路,但SerDes却并非是逻辑电平的概念,比逻辑电平(纯物理接口)的层次更高一些,因为它包含了物理层的部分协议。举个栗子:你可以说这条SerDes链路是基于CML逻辑电平的。

4,CML电平特点

1. CML电路输出晶体管工作在放大区域(同ECL一样),所以CML信号比采用饱和状态操作的CMOS、LVDS信号拥有更快的开关速度;

2. CML输出电路中的恒流源具有较小的开关噪声,信号的上升时间和下降时间小,因此CML理论极限速度可达10Gbit/s以上;如下图所示为:LVPECL、LVDS和CML三种逻辑电路功耗及速度比较示意图;

3. 低功耗(差分输出信号摆幅约为800mV,略低于LVPECL);

4. 电路简单,几乎不需要外围器件。

5,CML电路设计

CML电路设计规则,参考LVDS电路设计要求。如上很多针对高速链路的设计要求是通用的。