论文笔记_Fundamental Performance Limits and Scaling of a CMOS Passive Double-Balanced Mixer

Fundamental Performance Limits and Scaling of a CMOS Passive Double-Balanced Mixer

时间:2008年6月

作者:Krenar Komoni, Sameer Sonkusale, Geoff Dawe

文章目录

- Fundamental Performance Limits and Scaling of a CMOS Passive Double-Balanced Mixer

-

- 省流

- 摘要

- Introduction

- 无源双平衡混频器(FET-Quad Mixer)

- 对FET-Quad Mixer的分析

-

- 变频增益

- 1dB压缩点和IIP3

- 噪声系数

- 测量与仿真结果

- AI解析

-

- 文章概述

- 研究背景

- 研究思路

- 研究结果

- 研究结论与讨论

省流

本文仿真了350nm-32nm工艺制程下,FET-Quad无源双平衡混频器的变频增益、1dB压缩点、SSB噪声系数3个参数,并提出FOM参数(类似品质因数,定义见公式12)来综合考量这3个参数。最终得到图5。

研究意义:

- 工艺制程的缩小会带来FET-Quad混频器性能的提升,但是性能的提升有极限

- 可以在工程设计过程中,参照图5选择满足自己性能需求的混频器的工艺制程

摘要

本文研究了双平衡无源混合器的基本性能和尺寸极限。对无源双平衡混频器的分析将展示晶体管栅长(LG)的缩小对其性能指标的直接影响。我们根据变频增益(GC)、1-dB压缩点(P1-dB)和SSB噪声系数(NF)来分析性能。我们将展示,随着CMOS工艺技术的发展,双平衡无源混频器结构将变得更加有利,并进一步提升性能。我们通过对CMOS从350nm至32nm工艺设计的混频器的仿真和建模结果验证了这一点。我们引入了混频器的品质因数(FOMMIXER)来比较性能和工艺尺寸。电路设计人员和系统架构师可以使用这篇论文来找到一个满足他们对混频器需求的合适制程。

In this paper, fundamental performance limits and scaling of a double-balanced passive mixer are examined. Analysis of the passive double-balanced mixer will show how its performance metrics are directly affected by the down-scaling of the transistor gate length, LG. We analyze the performance in terms of conversion gain (GC), 1-dB compression point (P1-dB) which we derive, and SSB Noise Figure (NF). We will show that as CMOS process technology evolves, the double-balanced passive mixer architecture will become more favorable and yield improved performance. This is verified through simulation and modeling results for mixers designed in CMOS 350nm to 32nm technology. We introduce a mixer’s figure-of-merit (FOMMIXER) to compare performance with technology scaling. Circuit designers and System architects can use this paper to find a suitable process technology that will meet their specifications.

Introduction

FET-Quad 双平衡无源混频器的性能极限在哪里?

1990年早期,双极性晶体管渐渐被性能更好的CMOS管替代,尤其是模拟无线收发机的元件。这带来了一个新问题,CMOS技术可以带我们往前再走多远?

在CMOS技术中,最常用的两种混频器结构是:有源双平衡混频器,或吉尔伯特混频器;无源双平衡混频器,或FET-Quad混频器。

无源混频器的优势有:

- 不需要偏置的直流电流

- 没有静息功耗

- 具有更高的线性度

- 可以在电压域对信号进行整流

无源混频器的缺点:(可以随工艺制程的下降而改善)

- 噪声系数高

- 带宽有限

- 变频损耗大

通过变频增益(GC)、1-dB压缩点(P1-dB)和SSB噪声系数(NF)来分析混频器的基本性能极限

虽然没有明说,但是作者的意思应该是:无源混频器优点很突出,劣势能改善,所以无源混频器是趋势。并在后文只介绍了无源双平衡混频器(FET-Quad)

无源双平衡混频器(FET-Quad Mixer)

对无源双混频器(FET-Quad Mixer)进行了简介

无源双平衡混频器,也被称为FET-Quad混频器

- 双平衡结构有助于提高 RF-IF 和 LO-IF 的隔离度

- RF 和 LO 端口通过巴伦产生差分信号(在如图所示的模型中,巴伦认为是理想的)

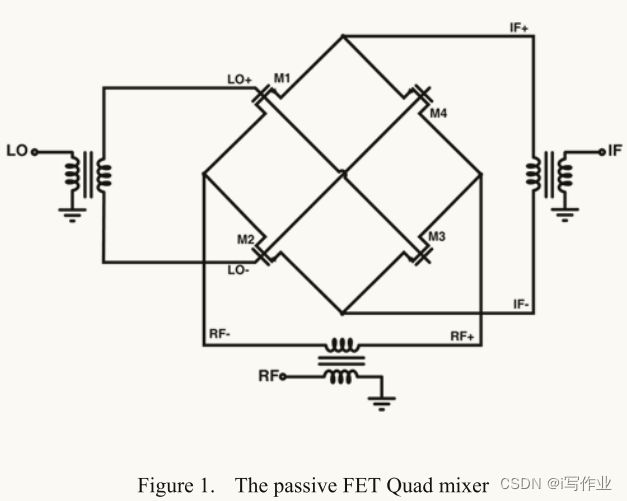

采用CMOS技术的双平衡无源混频器如图1所示:

FET-Quad混频器主要通过4个CMOS管(视作开关)不断的打开关闭来完成。RF信号从漏极输入,IF信号通过源极输出。LO信号从栅极输入,通过调制CMOS管的阻值来在电压域混合RF和LO信号。理想情况下希望LO信号的加入可以在CMOS管栅极的阈值电压附近变化。如图2,采用理想方波进行输入,对应的可以控制CMOS管的导通和关闭(即开关),图2(b)是分析单晶体管混频器的变频损耗模型。

该过程会产生所需的 ω R F ± ω L O \omega_{RF}\pm\omega_{LO} ωRF±ωLO 成分,还有各阶谐波相互混合的杂散 m ω R F ± n ω L O m\omega_{RF}\pm n\omega_{LO} mωRF±nωLO,理想情况下可以通过带通滤波器滤除所有杂散。

对FET-Quad Mixer的分析

分析分为2部分:

- 介绍单管的非平衡无源混频器,这会帮助分析和建模无源双平衡混频器

- 对无源双平衡混频器进行分析和建模

对比混频器的如下性能:变频增益、IIP3、1dB压缩点、噪声系数;并在最后引入FOM来综合对比这些性能

由于本文是分析混频器的基本性能极限,所以假设LO信号是理想的方波信号

变频增益

理想的方波信号:

v L O , s q u a r e = 1 2 + 2 π [ s i n ( ω L O t ) + s i n ( 3 ω L O t ) 3 + s i n ( 5 ω L O t ) 5 + ⋯ ] (1) v_{LO,square}=\frac12+\frac2\pi\left[ sin(\omega_{LO}t)+\frac{sin(3\omega_{LO}t)}{3}+\frac{sin(5\omega_{LO}t)}{5}+\cdots \right] \tag{1} vLO,square=21+π2[sin(ωLOt)+3sin(3ωLOt)+5sin(5ωLOt)+⋯](1)

假设RF信号为 c o s ( ω R F t ) cos(\omega_{RF}t) cos(ωRFt),其与理想方波本振相乘(理想单管无源混频)得到的电压最大值为 1 / π 1/\pi 1/π,即其理想变频增益为 20 log 10 ( 1 / π ) = − 9.943 d B 20\log_{10}(1/\pi)=-9.943\ dB 20log10(1/π)=−9.943 dB。

无源单管混频器最终变频增益的结果由2部分组成:

- 将混频器视为LTI1系统,即 not switching

- 将混频器是为LPTV2系统,即 switching

以下内容参考图2、图3

1.Not Switching - LTI System

为了便于计算,做出如下假设:

-

忽略 R S , R D R_S,R_D RS,RD,因为其远小于 r d s r_{ds} rds(on-resistance)

-

假定 Z O F F Z_{OFF} ZOFF的阻抗受线性栅-漏极和栅-源电容的支配

-

在低频低频率情况下,漏极电容和源极电容的非线性可以忽略不计

得到 R O N , Z O F F R_{ON},Z_{OFF} RON,ZOFF

R O N = r d s = L g μ n C O X W ( ( V g − g c ⋅ v R F ) − V t h − V d s ) (2) R_{ON}=r_{ds}=\frac{L_g}{\mu_nC_{OX}W((V_g-g_c\cdot v_{RF})-V_{th}-V_{ds})} \tag{2} RON=rds=μnCOXW((Vg−gc⋅vRF)−Vth−Vds)Lg(2)

Z O F F = 1 j ω R F ( C G S ( V G S = 0 ) ∣ ∣ C G D ( V G S = 0 ) ) (3) Z_{OFF}=\frac1{j\omega_{RF}(C_{GS(V_GS=0)}||C_{GD(VGS=0)})} \tag{3} ZOFF=jωRF(CGS(VGS=0)∣∣CGD(VGS=0))1(3)

根据图2(b),当开关闭合时变频增益为:

g c = ∣ Z L ∣ ∣ Z L + R O N ∣ ∣ Z O F F ∣ (4) g_c=\frac{|Z_L|}{|Z_L+R_{ON}||Z_{OFF}|} \tag{4} gc=∣ZL+RON∣∣ZOFF∣∣ZL∣(4)

当开关打开时,变频增益为公式(5),其变频增益非常接近于0

g c = ∣ Z L Z L + Z O F F ∣ (5) g_c=\left|\frac{Z_L}{Z_L+Z_{OFF}}\right| \tag{5} gc= ZL+ZOFFZL (5)

2.Switching - LPTV System

晶体管受理想方波调制不断开关(Switching),其变频增益为:

g c = 1 π ( Z L Z L + R O N ∣ ∣ Z O F F ) (6) g_c=\frac1\pi\left( \frac{Z_L}{Z_L+R_{ON}||Z_{OFF}} \right) \tag{6} gc=π1(ZL+RON∣∣ZOFFZL)(6)

图1分析的晶体管模型,也适用于FET-Quad的每一个晶体管。将FET-Quad的晶体管替换为图1的模型后,得到图4。在ON-OFF电容均为线性的前提下,得到最终的变频增益方程为(7)

G C = 10 log 10 ( 2 π ( Z L Z L + R O N ∣ ∣ Z O F F ) − 2 π ( Z L Z L + Z O F F ) ) (7) G_C=10\log_{10}\left( \frac2\pi \left( \frac{Z_L}{Z_L+R_{ON}||Z_{OFF}} \right) -\frac2\pi\left( \frac{Z_L}{Z_L+Z_{OFF}} \right) \right) \tag{7} GC=10log10(π2(ZL+RON∣∣ZOFFZL)−π2(ZL+ZOFFZL))(7)

可以看到此模型下FET-Quad的变频增益已经很接近理想值 2 / π 2/\pi 2/π了

工艺制程的下降会导致 L g L_g Lg、 μ 0 \mu_0 μ0、 C O X C_{OX} COX、 W W W 发生变化,并带来显著影响:

- L g L_g Lg 下降, R O N R_{ON} RON 也会下降,从而改善无源混频器的变频增益

- 通过增加 W W W 的宽度,也可以减小 R O N R_{ON} RON;但是其固有电容随 W W W 增加而成比例增加,导致 Z O F F Z_{OFF} ZOFF 减小,进而导致混频器工作带宽受限,在[15]3中具体讨论了栅长对截止频率的影响

IF端口的镜频和谐波频率也会对其变频增益带来负面影响,但是本篇文章忽略掉了

1dB压缩点和IIP3

公式(2)表示, R O N R_{ON} RON 的值与输入电压成比例,( g c ⋅ v R F g_c\cdot v_{RF} gc⋅vRF 越接近 V g − V t h − V d s V_g-V_{th}-V_{ds} Vg−Vth−Vds, R O N R_{ON} RON 越大);由于 R O N R_{ON} RON 的非线性性,输出信号 v I F = g c ⋅ v R F v_{IF}=g_c\cdot v_{RF} vIF=gc⋅vRF 会产生压缩,并最终导致1dB压缩点的出现。

利用多项式拟合该非线性性,得到公式(8)

v I F = c 0 + c 1 v R F + c 2 v R F 2 + c 3 v R F 3 + ⋯ (8) v_{IF}=c_0+c_1v_{RF}+c_2v_{RF}^2+c_3v_{RF}^3+\cdots \tag8 vIF=c0+c1vRF+c2vRF2+c3vRF3+⋯(8)

将 v I F = g c ⋅ v R F v_{IF}=g_c\cdot v_{RF} vIF=gc⋅vRF 表示为幂级数形式,并求解出了系数后,得到了公式(9)

∣ c 1 / c 3 ∣ = Z L ( Z O F F − L g μ n C O X W ( V g − V t h − V d s ) ) ( Z L + L g μ n C O X W ( V g − V t h − V d s ) ) 2 − L g μ n C O X W ( V g − V t h − V d s ) ⋅ ( Z L V g − V t h − V d s ) 2 ( Z L + Z O F F ) (9) |c_1/c_3|= \frac {Z_L\left( Z_{OFF}-\frac{L_g}{\mu_nC_{OX}W(V_g-V_{th}-V_{ds})} \right)\left(Z_L+\frac{L_g}{\mu_nC_{OX}W(V_g-V_{th}-V_{ds})} \right)^2} {-\frac{L_g}{\mu_nC_{OX}W(V_g-V_{th}-V_{ds})}\cdot \left( \frac{Z_L}{V_g-V_{th}-V_{ds}} \right)^2(Z_L+Z_{OFF}) } \tag 9 ∣c1/c3∣=−μnCOXW(Vg−Vth−Vds)Lg⋅(Vg−Vth−VdsZL)2(ZL+ZOFF)ZL(ZOFF−μnCOXW(Vg−Vth−Vds)Lg)(ZL+μnCOXW(Vg−Vth−Vds)Lg)2(9)

由(8)、(9)可以计算出1dB压缩点,如公式(10)所示:

P 1 d B = 10 log 10 ( 1000 ⋅ ( 0.145 ∣ c 1 / c 3 ∣ / 2 ) 2 4 Z S ) d B m (10) P_{1dB}=10\log_{10}\left( \frac{1000\cdot\left(\sqrt{0.145|c_1/c_3|}/\sqrt2\right)^2}{4Z_S} \right)dBm \tag{10} P1dB=10log10 4ZS1000⋅(0.145∣c1/c3∣/2)2 dBm(10)

噪声系数

忽略正弦LO导致的ON-OFF状态混叠带来的噪声。其输出电压的噪声谱密度为 v n 2 = 8 k T 0 / g d s v_n^2=8kT_0/g_{ds} vn2=8kT0/gds,其最终的噪声系数为如公式(11)所示:

F = 1 g c 2 + F M I X g c 2 ⋅ k T 0 R s = 1 g c 2 + 8 k T 0 / g d s g c 2 ⋅ k T 0 R s ⇒ S S B N F = 10 log 10 ( 1 g c 2 + 2 g c 2 ⋅ g d s ⋅ R s ) (11) \begin{align*} F=&\frac1{g_c^2}+\frac{F_{MIX}}{g_c^2\cdot kT_0R_s}=\frac1{g_c^2}+\frac{8kT_0/g_{ds}}{g_c^2\cdot kT_0R_s} \\ \Rightarrow& SSB\ NF=10\log_{10}\left( \frac1{g_c^2}+\frac2{g_c^2\cdot g_{ds}\cdot R_s} \right) \end{align*} \tag{11} F=⇒gc21+gc2⋅kT0RsFMIX=gc21+gc2⋅kT0Rs8kT0/gdsSSB NF=10log10(gc21+gc2⋅gds⋅Rs2)(11)

测量与仿真结果

仿真得到的变频增益、1dB压缩点、噪声系数如图5所示。其仿真采用Cadence Spectre-RF软件,依次采用130nm-65nm工艺制程的高精度高频晶体管模型,并与其它论文结果进行了对比。本文还实测了一个130nm工艺的混频器,也在图5中标出来了。

定义 F O M FOM FOM 来综合考量混频器的变频增益、1dB压缩点、噪声系数等指标,得到公式(12)

F O M M I X E R ( d B m / H z ) = G c − S S B N F + P 1 d B − P C O N S U M E D (12) FOM_{MIXER}(dBm/Hz)=G_c-SSB\ NF+P_{1dB}-P_{CONSUMED} \tag{12} FOMMIXER(dBm/Hz)=Gc−SSB NF+P1dB−PCONSUMED(12)

虽然无源混频器没有用使用直流电源,但是却采用了LO的能量,于是添加了 P C O M S U M E D = V D D I D C + P L O P_{COMSUMED}=V_{DD}I_{DC}+P_{LO} PCOMSUMED=VDDIDC+PLO

AI解析

文章概述

本文研究了CMOS无源双平衡混频器的基本性能限制和扩展。通过分析单晶体管无源混频器的模型,进一步分析了双平衡混频器的性能。研究发现,随着CMOS工艺技术的发展和MOSFET器件的门长减小,FET-Quad混频器的性能参数接近其理想的基本限制。该研究为比较不同技术的混频器性能提供了必要的工具。

研究背景

本篇文章的研究背景是关于CMOS无源双平衡混频器的基本性能和尺寸的极限的研究。文章介绍了CMOS技术在无线收发器的模拟组件中取代双极性晶体管的趋势,并探讨了随着CMOS工艺尺寸缩小,无源双平衡混频器的性能指标如转换增益、1-dB压缩点和噪声系数等如何受到影响。研究表明,随着CMOS工艺技术的发展,无源双平衡混频器的架构将变得更加有利,并能够提供更好的性能。这一结论通过在CMOS 350nm到32nm工艺下设计的混频器的模拟和建模结果得到验证。文章还引入了混频器的性能评估指标(FOMMIXER),以比较不同工艺尺寸下的性能。这篇论文可以帮助电路设计师和系统架构师找到适合其规格要求的工艺技术。

研究思路

本研究的研究问题是关于CMOS无源双平衡混频器的基本性能和尺寸的极限。研究通过分析无源双平衡混频器的性能指标,如变频增益、1-dB压缩点和SSB噪声系数,来探讨晶体管栅长的缩小对其性能的直接影响。研究还通过模拟和建模结果验证了随着CMOS工艺技术的发展,无源双平衡混频器架构将变得更有利并能进一步提高性能。此外,研究引入了混频器的性能评估指标(FOMMIXER),用于比较不同工艺尺寸下的性能表现。通过本研究,电路设计师和系统架构师可以找到适合其规格要求的工艺技术。

研究的思路主要包括以下几个方面:

- 首先,研究回顾了CMOS技术在无线收发器的模拟组件中取代双极性晶体管的发展历程,并介绍了CMOS无源双平衡混频器和有源双平衡混频器的优劣势。

- 接着,研究分析了无源双平衡混频器的基本工作原理,包括使用CMOS技术构建的FET-Quad混频器的结构和工作方式。

- 研究对无源双平衡混频器的性能进行了详细分析,包括电压转换增益、1-dB压缩点、IIP3和噪声系数等指标。通过建立模型和方程式,研究得出了这些性能指标与CMOS工艺尺寸缩放之间的关系。

- 最后,研究引入了一个新的性能评估指标(FOM),综合考虑了转换增益、IIP3、1-dB压缩点和噪声系数等参数。这个指标可以帮助电路设计师和系统架构师选择适合其要求的工艺技术。

- 通过以上研究思路和方法,本研究解决了关于CMOS无源双平衡混频器的性能极限和尺寸缩放的研究问题,并为电路设计师和系统架构师提供了选择合适工艺技术的参考依据。

研究结果

这篇文章主要研究了CMOS被动双平衡混频器的基本性能和尺寸极限。文章通过分析被动双平衡混频器的性能指标,如转换增益、1-dB压缩点和单边带噪声系数,展示了这些指标如何受到晶体管栅长缩放的直接影响。文章还介绍了一种混频器的性能评估指标(FOMMIXER),用于比较不同工艺尺寸的性能。

文章通过理论分析、仿真和实测验证了模型的准确性。作者还通过在CMOS 350nm到32nm工艺下设计的混频器进行仿真和建模,验证了随着CMOS工艺技术的发展,被动双平衡混频器的架构将变得更有优势并具有改进的性能。

至于实验的假设论证,文章没有明确提到具体的实验,而是通过理论分析、仿真和建模来验证模型的准确性。因此,文章没有提供实验假设的论证结果。

研究结论与讨论

1、研究结论:本文的研究结论是随着CMOS工艺技术的发展和晶体管栅长的缩小,双平衡无源混频器的性能参数将达到理想的极限。通过模拟和建模结果验证了这一结论,并引入了混频器的性能评价指标(FOMMIXER)来比较不同工艺的性能。

2、研究的创新性:本研究的创新之处在于对双平衡无源混频器的性能极限进行了分析,并提出了与工艺参数相关的新的性能评价指标。此外,通过模拟和建模验证了研究结论,为电路设计师和系统架构师选择合适的工艺技术提供了参考。

3、研究的不足之处:本研究的不足之处可能包括对其他混频器结构的比较不充分,以及对实际工艺的适应性的缺乏分析。此外,由于本文是基于理论和模拟结果的分析,可能存在与实际器件性能的差异。

4、研究展望:根据这项研究,后续可能的研究方向包括进一步探索不同混频器结构的性能极限和优化方法,以及与混频器性能相关的其他工艺参数的研究。此外,可以考虑将本研究扩展到更先进的工艺技术,并进行实际器件的测试和验证。

5、研究意义:本研究的理论意义在于揭示了双平衡无源混频器的性能极限和与工艺参数的关系,为混频器设计和工艺选择提供了指导。在实践意义上,本研究为电路设计师和系统架构师提供了选择合适工艺技术的依据,以满足系统规格要求并提高性能。

公式(2)变量解释:

- R O N R_{ON} RON: 晶体管开启时的电阻。

- r d s r_{ds} rds: 晶体管开启时的通态电阻。

- L g L_g Lg: 晶体管的栅长。

- W: 晶体管的栅宽。

- μ n \mu_n μn: n型沟道迁移率。

- C O X C_{OX} COX: 栅氧化层电容密度。

- V g V_g Vg: 晶体管的栅源电压。

- V t h V_{th} Vth: 晶体管的阈值电压。

- V d s V_{ds} Vds: 晶体管的漏极-源极电压

- v R F v_{RF} vRF: 射频信号的幅度。

- g c g_c gc: 晶体管的跨导。

- ( V g − g c ⋅ v R F ) − V t h − V d s (V_g-g_c\cdot v_{RF})-V_{th}-V_{ds} (Vg−gc⋅vRF)−Vth−Vds: 得到晶体管工作时的电压。

公式(3)变量解释

- Z O F F Z_{OFF} ZOFF: 晶体管关闭时的阻抗。

- C G S ( V G S = 0 ) C_{GS(V_GS=0)} CGS(VGS=0): 当晶体管的栅源电压为0时的栅源电容。

- C G D ( V G S = 0 ) C_{GD(V_GS=0)} CGD(VGS=0): 当晶体管的栅源电压为0时的栅漏电容。

- ||: 表示并联。

公式(11)的变量解释

- F M I X F_{MIX} FMIX:混频器本身的噪声系数。

- k:玻尔兹曼常数。

- T 0 T_0 T0:系统的参考温度。

- R s R_s Rs:混频器输入端的源电阻。

- g d s g_{ds} gds:混频器的跨导。

公式的第一部分 1 / g c 2 1/g_c^2 1/gc2 表示了输入信号的转换增益的倒数,即输入信号功率的倒数。这部分表示了信号被混频器转换产生的信号增益。

第二部分 F M I X g c 2 ⋅ k T 0 R s \frac{F_{MIX}}{g_c^2\cdot kT_0R_s} gc2⋅kT0RsFMIX 表示了混频器本身的噪声系数相对于输入信号的转换增益。这部分表示了混频器内部噪声对整体噪声系数的贡献。

通过组合这两部分,我们可以得到总体的噪声系数。

最后,公式通过引入SSB NF(单边带噪声系数),将噪声系数转化为以分贝为单位的值。

Linear Time Invariant,线性时不变系统 ↩︎

Linear Peroid Time Variant,线性周期时变系统 ↩︎

Woerlee, et al, “RF CMOS performance trends”, IEEE Trans. ED, vol.48, no.8, pp.1776-1782,. August 2001 ↩︎