开源verilog模拟 iverilog verilator +gtkwave仿真及一点区别

开源的 iverilog verilator 和商业软件动不动几G几十G相比,体积小的几乎可以忽略不计。

两个都比较好用,各有优势。

iverilog兼容性好。

verilator速度快。

配上gtkwave 看波形,仿真工具基本就齐了。

说下基本用法

计数器

counter.v

module counter(

input wire clk,

input wire rst_n,

output reg[7:0] out

);

always @(posedge clk or negedge rst_n)

if(!rst_n)

out <= 0;

else

out <= out + 1;

endmodule

testbench

test.v

module test;

reg rst_n;

reg clk;

initial begin

#10 rst_n = 1;

#10 rst_n = 0;

#10 rst_n = 1;

#50 $finish;

end

initial begin

$dumpfile("test.vcd");

$dumpvars(0,test);

$monitor("time=%t, out=%h",$time,out);

end

always #1 clk = !clk;

wire[7:0] out;

counter c1(clk, rst_n, out);

endmodule

rst_n和clk故意未赋初值 能看出些区别。

先用iverilog

iverilog test.v counter.v

生成a.out

直接运行

./a.out

或

vvp a.out

会生成test.vcd

vcd全称 value change dump

从名字可以看出来用来记录数值变动的文件

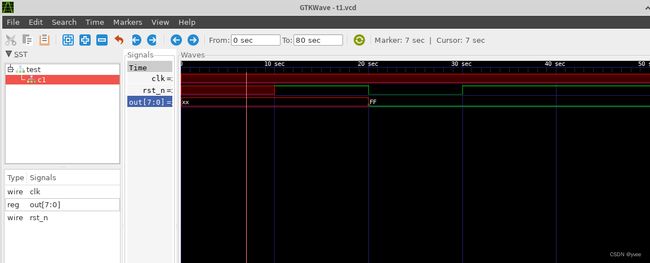

gtkwave test.vcd

可以看出由于clk没有初值,翻转后也不定。上面直接是红色的,xx不确定。

verilator 可以写个c++调用顶层,也可以不写,用个-binary参数,编译。

verilator -binary -trace test.v counter.v

注不加-trace编译运行后 不生成波形文件。

会在当前目录下创建 obj_dir,中间文件和生成的文件都在里面。

会生成一个以第一个verilog+V命名的可执行文件以上面为例 会生成Vtest

如果把counter放前面会生成Vcounter,运行

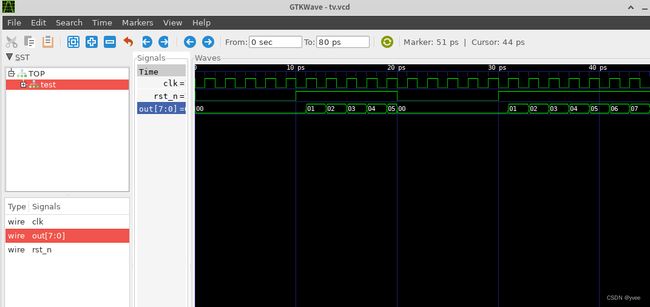

./obj_dir/Vtest

当前目录下会生成test.vcd

可以看出直接已经帮你赋初值了

再给rst_n赋初值0

如果给rst_n 赋初值1

中间加个 #5 rst_n = 0;

可以看出,rst_n从开始至变0以前 out的值也是不确定的,上面都直接表示了出来

iverilog兼容性非常好,拿个老文件,基本直接就能编译通过。

但编译的比较慢,文件一多感受就非常明显了。同样一大运行的也慢。

verilator检查比较严格, 但是增量编译,动哪个编哪个,最后再链接。

各有优点吧。反正体积不大,都装上吧。