Verilog语言交通灯课程设计

一、 设计思路

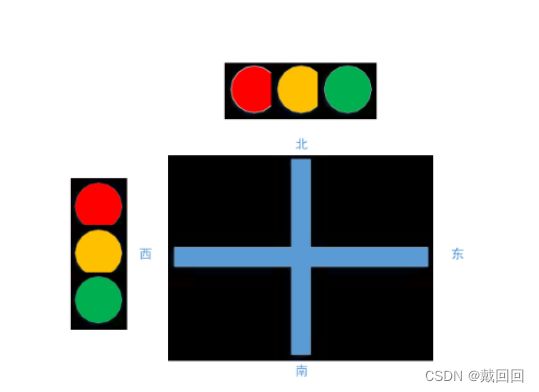

1)设计一个十字路口交通灯控制器。交通灯处于东西大街和南北大街,如图2-1所示用寄存器模拟十字路口交通信号控制情况。当东西方向为绿灯时,南北方向为红灯,二南北方向为绿灯时,东西方向为红灯。东西向通行时间为11s,南北向通行时间为11s。

图2-1路口示意图

diagrammatic sketch

2)东西、南北方向黄灯都亮3s。

3)用高低电平分别表示灯灭灯亮,用计数器实现状态跳转。

二、设计原理

1.首先了解实际交通灯的变化情况和规律。初始时东西向绿灯,g1输出高电平,南北向红灯,r2输出高电平。12个时钟脉冲后,原绿灯方向变为黄灯,再3个时钟脉冲后,黄灯方向变红灯,同时原红灯方向变绿灯;随后又是12个时钟脉冲后,当前绿灯方向又变为黄灯,再过3个时钟脉冲后,黄灯方向变红灯,同时当前红灯方向又变为绿灯,如此循环往复。

2.共有四种状态,状态1东西方向绿灯亮11秒,南北方向红灯亮 11;状态2东西方向黄灯亮3秒,南北方向红灯亮 3秒;状态3东西方向红灯亮11秒,南北方向绿灯亮 11秒;状态4东西方向红灯亮3秒,南北方向黄灯亮 3秒。列出交通信号灯的状态表如下:(其中,1代表灯亮,0代表灯灭)

表2-1 状态表

state table

三、各输入输出变量说明

clk:计数时钟;

r1,r2,g1,g2,y1,y2:分别代表东西方向,南北方向红绿黄灯;

cnt: 译码器输出

中间变量:

code:代表r1,r2,g1,g2,y1,y2;

module DecCounter(clk,cnt);

output[4:0] cnt;

reg[4:0] cnt;

wire clr:清零信号;

module Decoder(cnt,code);

output[5:0] code;

reg[5:0] code;

四、主要程序代码:

module traffic_light(clk,r1,y1,g1,r2,y2,g2);

input clk;

output r1,y1,g1,r2,y2,g2;

reg[5:0] buf1=6'b001100;

wire[4:0] cnt;

wire[5:0] code;

DecCounter u1(clk,cnt);

Decoder u2(cnt,code);

always @(posedge clk)

begin

buf1=code;

end

assign {r1,y1,g1,r2,y2,g2}=buf1;

endmodule

module Decoder(cnt,code);

input[4:0] cnt;

output[5:0] code;

reg[5:0] code;

always @(cnt)

begin

case(cnt)

5'b00000: code=6'b001100;

5'b00001: code=6'b001100;

5'b00010: code=6'b001100;

5'b00011: code=6'b001100;

5'b00100: code=6'b001100;

5'b00101: code=6'b001100;

5'b00110: code=6'b001100;//7

5'b00111: code=6'b000100;

5'b01000: code=6'b001100;

5'b01001: code=6'b000100;

5'b01010: code=6'b001100;//4

5'b01011: code=6'b010100;

5'b01100: code=6'b010100;

5'b01101: code=6'b010100;//3

5'b01110: code=6'b100001;

5'b01111: code=6'b100001;

5'b10000: code=6'b100001;

5'b10001: code=6'b100001;

5'b10010: code=6'b100001;

5'b10011: code=6'b100001;

5'b10100: code=6'b100001;//7

5'b10101: code=6'b100000;

5'b10110: code=6'b100001;

5'b10111: code=6'b100000;

5'b11000: code=6'b100001;//4

5'b11001: code=6'b100010;

5'b11010: code=6'b100010;

5'b11011: code=6'b100010;//3

default: code=6'b000000;

endcase

end

endmodule

module DecCounter(clk,cnt);

input clk;

output[4:0] cnt;

reg[4:0] cnt;

wire clr;

assign clr=~(cnt[4]&cnt[3]&cnt[1]&cnt[0]);

always @(posedge clk)

begin

cnt[4]<=clr&(cnt[4]^(cnt[3]&cnt[2]&cnt[1]&cnt[0]));

cnt[3]<=clr&(cnt[3]^(cnt[2]&cnt[1]&cnt[0]));

cnt[2]<=clr&(cnt[2]^(cnt[1]&cnt[0]));

cnt[1]<=clr&(cnt[1]^cnt[0]);

cnt[0]<=clr&(~cnt[0]);

end

endmodule说明:蛮久以前写的,从课程设计报告上粘下来的,没写注释,代码里面包括了竞争冒险的消除,有问题可以留言。

运行截图: