E10—10G subsystem Ethernet IP实现万兆以太网上下位机通信

1.简介

当前多数PC集成的网卡多数是千兆以太网卡,因此通过介质实现PC与FPGA的通信需要使用专用的转接卡,转接卡就是将光介质进来的数据通过PCIE接口传递给CPU,以此实现通信。整体通路可以使用不同的协议实现通信,那么相应的设备上的代码以及转接卡的作用包括上位机的代码都会不同,参考Aurora IP核 是另一种方案的实现方式。本文介绍的是,通过以太网协议实现上下位机通信。那么下位机FPGA主要的实现方案是基于xilinx 10G subsystem Ethernet IP核,转接卡则是购买的光润通的双通道,对应的上位机使用的是网口调试助手,如果开发可以使用qt的udpsocket或者C++的winsock库。

Xilinx 10G以太网IP核帮助我们实现了以太网mac层和PCS/PMA层,如下图所示,二者之间通过XGMII接口传输数据,类似于MII、GMII、RGMII接口,为啥把单独的这个接口释放出来,是因为可以仅用一个PCS/PMA ip核就可以同其他设备通信,只不过MAC层的数据要用户侧解析,但这样做的好处是数据的延迟较小。下图中,MAC层主要是为了完成以太网帧mac层数据的解析及到用户侧AXI-Stream的数据转换,并为用户提供了一个AXI4-Lite接口,允许用户通过该接口完成对PHY层的寄存的配置,具体MAC层内部的结构如figure1-2所示,具体功能查看PG157。而PCS/PMA属于是PHY层,同serdes的pcs/pma基本一致,主要完成编码、电平转换等功能,这里设计用于10GBASE-R光模块接口和10GBASE-KR背板两种接口,同样具体内部结构如figure1-3。

需要说明的是,该IP核是付费的,可以在官网申请但有一定的时间要求和限制。在对应该文章的源码中给到了license文件。可以下载使用。

2.场景

创建一个场景是,PC端已知设备的IP与端口,使用网口调试助手向下发送数据时,系统会自动发出ARP指令,下位机响应ARP应答,随后下位机接收到数据之后可以原样返回。

3.以太网帧结构

3.1网络模型

该图清晰的展示了,10GBASE-R光模块接口和10GBASE-KR背板两种接口在物理层的实现上有不同,也展示了当前设计在以太网模型中所处的位置。

3.2帧结构

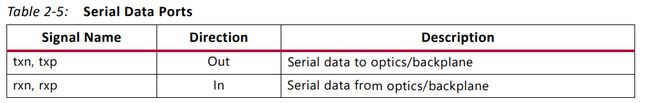

如下图所示为以太网帧结构,从左到右分别为前导码,帧定界符,目的mac地址,源mac地址,长度/类型如0800代表UDP帧,0806代表ARP命令;数据帧以及填充数据和帧校验字段。

需要说明的是,使用10G以太网IP核,用户侧输入数据将从目的mac地址开始,对于以太网帧没有IP的概念,只有IP的数据报文才ip的概念,这里的IP数据包是作为以太网的“Data”字段出现在以太网帧上的。其余的字段IP核内部会填充,这个在数据读写时序部分会有体现。另外,当数据+pad小于以太网的最小帧长46B时,会自动填充至最小帧长度。对于用户侧来说,就是按照以太网帧格式,将UDP数据打包进IP数据包,再将IP数据包打包进以太网帧,结合IP提供的功能,将用户侧数据按照axi的接口发送即可。如果使用巨型帧、VLAN等功能,需要通过AXI-Lite配置寄存器。如无特殊需求,默认配置即可实现基本功能。

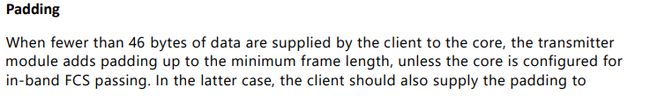

4.port说明

发送数据接口,与常用的axi stream接口基本一致,其中s_axis_tx_user信号代表当前包的好坏,设置为1即可。Tx_ifg_delay代表packets之间的间隔,设置为0即可,以太网要求两个帧之间的最小间隔是96个时钟,这个配置为0内部寄存器有最小的默认值,不必担心。

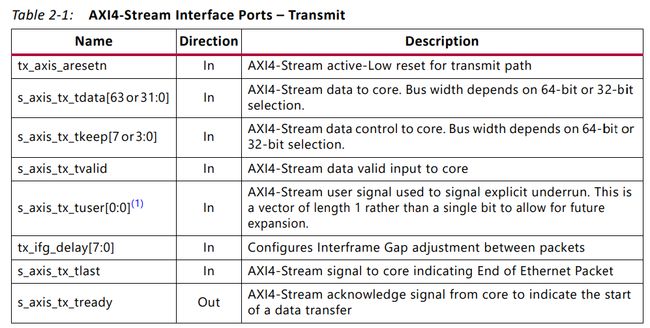

接收数据接口

这里需要说明的是tuser信号,当last信号与tuser信号同时拉高,代表一帧传输成功完成,同last一样,只拉高一个周期。当一帧中的长度字段与实际的数据长度不一致,或者一帧的数据小于以太网要求的最小长度,或者超出长度等情况发生的时候,会在该帧的结尾部分,拉高last但保持tuser为0标识标识该帧是一个有问题的帧。

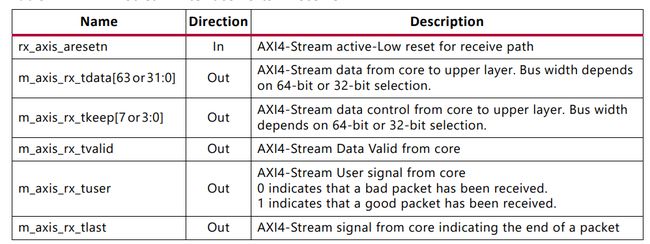

FPGA内部的serdes通道,与光电转换器或者背板连接器相连

光纤收发器信号

Tx_fault拉高时代表tx通过检测遇到错误,通常接上拉4.7k电阻。TX_DISABLE输入信号:在拉高时SFP+模块输出不工作,拉低SFP+工作。SFP0_MOD_ABS检测光模块是否插入,未插入则拉高。SFP0_RLOSS高电平时表示接收光信号电平低于相关标准。SFP0_RS0/1代表速率选择,通常两个都全部上拉,选择最高速率,Xilinx建议将SFP0_RLOSS与SFP0_MOD_ABS取或非作为signal_select的输入,实际使用中,可以将该信号值设置为1,但是有问题出现的时候,要排查发射笼的信号。tx_fault输入,可以直接设置为0,手册提及最新版本中IP内部并没有用该信号。tx_disable是输出信号,一般都不用,但是笼子上的tx_disable信号通常要拉为低。

当选择Include Shared Logic in example design和Shared Logic Included in Core时,关于时钟和复位的接口有所不同,,还有用于接口配置的AXI-Lite接口,下面不做介绍,大部分无需使用,如有使用时在查看即可。

5.AXI-Stream接口时序

需要注意的是,按照以太网帧格式,前导码、帧校验等字段无需给出,只需要从目的MAC地址开始,到数据结束即可。对于发送和接收来说,需要解析keep信号。另外,IP配置时位宽不同时序稍有不同。再有就是采用的是小端序,即FPGA给到用户的数据采用的是小端位序,即放在tdata低位处的数据,使用winsock接收之后,将放在缓冲区(指针区域)的低字节处,如果转换成数据,tdata最低位将对应array[0]。

6.ip核的配置

第一页根据自己的项目需求选择axi总线数据位宽,这里选64bit。使用的K7系列的板卡,K7系列不支持背板连接;第二页为了配置巨型帧的使用,勾选AXI4-Lite总线;第三第四页保持默认;第五页选择in core,当多个通道需要共享时钟复位资源的时候可以配置in example design。

7.代码设计

文章源码链接如果与上位机联合调试,那么可以直接使用;如果作为其他项目的接口文件可以分别设计读写控制模块以连接其他逻辑模块。该工程中可以实现ARP的应答,但不会主动的发起ARP请求,通过同步fifo将接收的数据传入,然后通过fifo后在用UDP协议原样返回,不支持Ping和ICMP等其他协议。在实际代码设计的时候需要注意,只有与上位机DHCP动态分配的(或者手动指定的)IP在同一个网段时,winsock库在向指定的IP(指下位机IP)发送UDP数据包时才会自动的发出ARP请求。

8.上板验证调试步骤

这里使用网口助手 和wireshark两个工具,调试以及网络数据包可以参考千兆以太网的实现,以下链接分别是TEMAC IP实现千兆以太网 组包写MAC实现千兆以太网 基于千兆以太网的小项目

8.1眼图测试信道质量

10.315G速率下,BER值为10的-12次方,信道质量良好。眼图测试参考链接

8.2查看ARP协议相应情况

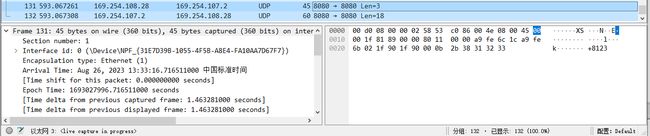

上位机mac地址:58-53-C0-86-00-4E

上位机ip地址 :169.254.108.28(DHCP自动获取,无需配置)

下位机mac地址:00-d0-08-00-00-02(提前配置)

下位机ip地址 :169.254.107.2(提前配置)

Wireshark抓包结果

![]() Windows shell 使用arp -a命令查看arp表,如图所示

Windows shell 使用arp -a命令查看arp表,如图所示

8.3UDP数据接收与发送

发送两个数据包,一个内容是“http://www.cmsoft.cn QQ:10865600”(代表正常帧长度)、另一个是“123”(帧长小于48bit,以测试上位机是否会自动补0),测试结果如下图

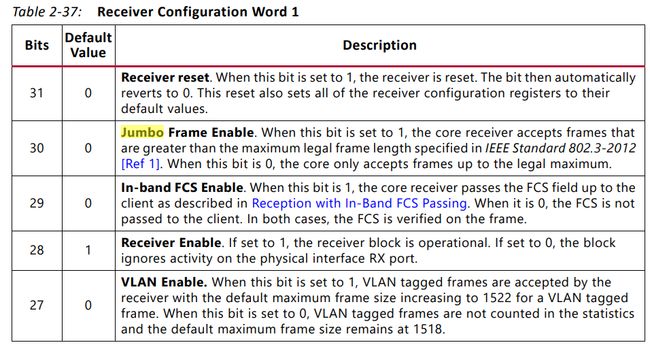

9.两种方法开启巨型帧

对于正常帧,数据字段的长度可以从0到1,500字节变化。IP core可以处理任何长度的巨型帧。该字段始终在分组数据中提供以进行传输,并且始终保留在接收分组数据中。为了提高效率,一些项目中会打开这个模式。1.当不选择axi_lite配置寄存器时,会生成mac_tx_configuration_vector 和mac_rx_configuration_vector 接口。如下图所示,发射机巨型帧启用。当该比特为1时,核心发射机允许发送大于IEEE标准802.3-2012 [Ref 1] 中指定的最大合法帧长度的帧。当设置为0时,核心发射机只允许发送不超过法定最大值的帧。开启方法:将mac_tx_configuration_vector 和mac_rx_configuration_vector的第4bit置1

2.当选择采用axi_lite配置寄存器时 寄存器地址为0x404 第30位置1