《低功耗方法学》翻译——第一章:介绍

第一章:介绍

1.1 概述

在过去的二十年时间里,复杂芯片的设计已经经历了一系列巨大的改变。20世纪80年代,引入了基于语言的设计和综合。在20世纪90年代,设计重用和IP成为主流设计。在过去的几年里,低功耗设计再次开始改变设计师处理复杂SoC设计的方式。

每一次技术革新都是对不断发展的半导体技术所带来挑战的回应。芯片密度的指数级增长推动了基于语言的设计和综合的应用,极大地提高了设计者的生产力。这种方法将摩尔定律搁置了大约十年,但在百万门设计的时代,工程师们发现,为一个新的芯片项目编写新的RTL是有限的。结果是,IP和设计重用被认为是用相对较小的设计团队设计大型芯片唯一实用的方法。如今,每个SoC设计都采用了大量的IP,以利用亚微米技术提供的不断增加的密度。

从130nm开始的深亚微米技术提出了一系列新的设计问题。我们现在可以在一个相当小的芯片上实现数千万个门,从而使功率密度和总功耗达到封装、冷却和其他基础设备所能支持的极限。随着技术缩小到90nm及以下,漏电流急剧增加,在一些65nm的设计中,漏电流几乎与动态电流一样大。

这些变化在芯片如何设计的问题上产生了重要影响。随着芯片制程的不断缩小,最高性能芯片的功率密度已经增长到无法再提高时钟速度的地步。因此,设计者正在设计多处理器芯片,而不是具有单个超高速处理器的芯片。

电池供电的设备是电子市场增长最快的领域之一,深亚微米工艺的泄漏是一个主要问题。为了解决这个问题,设计人员在设计过程的每一步,从软件到架构再到实现,都采用了比较针对性的的方法。这些方法包括功率门控,即模块在不使用时关闭电源,以及多阈值的单元库,可以在泄漏电流和速度之间进行权衡。

对于所有应用,复杂SoC的总功耗是一个巨大的挑战。为了解决这一挑战,设计人员正在从单一电源电压用于芯片的所有非IO门的方法转变为多电源架构,其中不同的模块根据各自的需求以不同的电压运行。在某些情况下,设计者使用电压调节技术来根据其工作负载和因此所要求的性能来改变关键模块的电源电压(和时钟频率)。

此书描述了很多可以用来降低复杂Soc设计功耗的技术。我们的方法是实用的,而非理论性的。我们在很大程度上借鉴了过去几年在制作一系列技术示例芯片方面获得的经验。我们相信,我们所描述的技术今天可以被芯片设计者用来显著改进他们设计的芯片。

1.2 问题的范畴

今天,一些最强大的微处理器芯片可以消耗100-150瓦的功率,平均功率密度为每平方厘米50-75瓦。芯片上的局部热量可能比这个数字高出好几倍。

这种功率密度不仅会给封装和冷却带来挑战,还会给可靠性带来问题,因为平均故障时间随温度呈指数下降。此外,计时随温度降低,泄漏随温度增加。

从历史上看,最高性能芯片的功率随着每一个新技术节点的出现而增加,但由于功率密度带来的问题,国际半导体技术路线图(ITRS)预测,这些芯片的功率将在2008年达到最大198瓦;在此之后,功率将保持不变。

微处理器芯片的总功耗已经给服务器领域带来了一个重要的问题。对于这些服务器群,基础设施成本(电源、冷却)可以等于计算机本身的成本。

对于电池供电的手持设备,数量更小,但问题仍然很严重。据ITRS的说法,这些设备的电池寿命在2004年达到了顶峰。此后,随着功能的增加超过了功率(每个频率)的减少,电池寿命就降低了。

对于几乎所有的应用程序,减少Soc的能耗,对于继续增加性能和特性并发展这些业务至关重要。

直到最近,功率一直是芯片设计的第二级问题,仅次于成本、面积和时间等第一个问题。今天,对于大多数SoC设计来说,功率预算是该项目最重要的设计目标之一。超过功率预算对一个项目来说可能是致命的,这意味着无论从一个廉价的塑料封装到一个昂贵的陶瓷封装,还是由于过度的功率密度导致无法接受的低可靠性问题,或者无法达到所需的电池寿命。

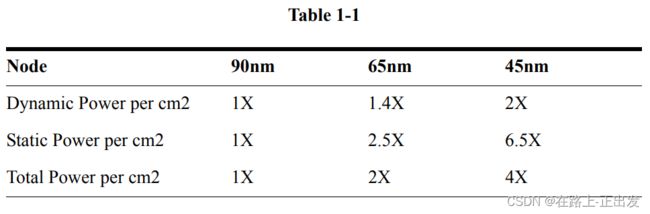

随着我们转向下一个技术节点,这些问题都会变得更糟。ITRS做出了以下预测:

不用说,许多设计团队正在非常努力地将功率增长降低到这些预测数字以下,因为即使是90纳米的设计,也有许多设计处于客户可以接受的极限。

1.3 功率 vs 能量

对于电池供电的设备来说,功率和能量之间的区别至关重要。图1-1说明了不同之处。功率是设备中的瞬时功率。能量是曲线下的区域-功率随时间的积分。例如,手机使用的功率因其所做的事情而有所不同--无论是在关闭盖子的情况下处于待机状态,还是打开并打开显示屏,或者从网络上下载。图1-1中图形的高度显示了功率,但决定电池寿命的是能量-曲线下的区域。

1.4 动态功率

SoC设计的总功率包括动态功率和静态功率。动态功率是指当设备处于活动状态时,即信号改变值时所消耗的功率。静态功率是指当设备通电但没有信号改变值时所消耗的功率。在CMOS器件中,静态功率消耗是由于泄漏导致。

动态功耗的第一个也是主要来源是开关功率--对栅极上的输出电容进行充电和放电所需的功率。图1-2显示了开关功率。

每次电平转换带来的能量为:

![]() 是负载电容,

是负载电容,![]() 是供电电压。此处书中给出的结论过于直接,这里给出我的推导过程,希望对读者的理解有所帮助。

是供电电压。此处书中给出的结论过于直接,这里给出我的推导过程,希望对读者的理解有所帮助。

动态功耗可以描述为:

![]() 为电平转换的频率,

为电平转换的频率, ![]() 为单元输出端电平转换的概率,

为单元输出端电平转换的概率,![]() 为系统时钟频率,如果我们定义:

为系统时钟频率,如果我们定义:

那我们就可以用更相似的表达式描述动态功耗:

注意,开关功率并不是晶体管尺寸的函数,而是开关活动性和负载电容的函数,因此它具有数据依赖性。

除了开关功耗,内部功耗也会导致动态功耗的增加。图1-3所示为内部开关电流、内部功率由短路电流(当NMOS和PMOS晶体管都打开时)以及单元内部电容充电电流导致。

如果加上内部功率,动态功率的表达式为

![]() 为短路电流的持续时间,

为短路电流的持续时间,![]() 为总的内部开关电流(短路电流加内部电容充电电流)。

为总的内部开关电流(短路电流加内部电容充电电流)。

只要保持输入信号的斜坡时间较短,短路电流在每个跃迁过程中只发生很短的一段时间,整个动态功率主要由开关功率决定,为此,我们经常简化开关功率公式:

但在某些情况下,短路电流(通常称为直通电流)令人兴趣。特别是,当我们讨论如何处理电源门控块的浮动输出时,我们将讨论如何防止过量过剩的方法。

在架构、逻辑设计和电路设计中,有许多技术可以降低在给定技术中实现的特定函数的功率。这些技术侧重于平衡点的电压和频率分量,以及减少与数据依赖的开关活动。

有各种架构和逻辑设计技术来最小化开关活动,这有效地降低了所涉及的门的开关活动。

一个有趣的例子是[1],它描述了工程师如何使用微结构结构修改来显著降低英特尔处理器的功耗。

由于功率对电压的二次依赖性,降低电源电压是降低动态功率的一种高度杠杆化的方法。但由于逻辑门的速度随着供应电压的降低而降低,这种方法需要谨慎地进行。SoC设计师可以通过以下几种方式来利用这种方法:

- 对于不需要运行特别快的块,如外设,我们可以使用比其他速度更关键的块更低的电压供应。这种方法被称为多电压。

- 对于处理器,我们可以提供一个可变的电源电压;在需要最高性能的任务中,我们可以提供一个较高的电源电压和相应的较高的时钟频率。对于需要较低性能的任务,我们可以提供一个较低的电压和较慢的时钟。这种方法被称为电压缩放。

另一种降低动态功率的方法是时钟门控。将频率驱动到零,将功率驱动到零。一些形式的时钟门控被应用在许多Soc设计中。

1.5 动态与静态功率的冲突

降低动态功率最有效的方式就是降低供电电压。在过去的15年时间里,随着半导体技术的不断攀升,供电电压![]() 已经从5V到3.3V再到2.5V到1.2V。ITRS路线图预测,2008年和2009年,高性能设备将使用1.0V,低功率设备将使用0.8V。

已经从5V到3.3V再到2.5V到1.2V。ITRS路线图预测,2008年和2009年,高性能设备将使用1.0V,低功率设备将使用0.8V。

降低![]() 的问题在于它会导致

的问题在于它会导致![]() 、晶体管的导通电流、驱动电流降低,最终导致速度下降。如果我们忽略速度饱和和发生在90nm以下的一些其他细微影响,单个MOSFET的

、晶体管的导通电流、驱动电流降低,最终导致速度下降。如果我们忽略速度饱和和发生在90nm以下的一些其他细微影响,单个MOSFET的![]() 估计值为:

估计值为:

![]() 为载流子迁移率,

为载流子迁移率,![]() 为栅极电容,

为栅极电容,![]() 为阈值电压,

为阈值电压,![]() 为栅源电压。从上式可以清晰地看出,为保持良好的性能,当我们降低

为栅源电压。从上式可以清晰地看出,为保持良好的性能,当我们降低![]() (等于

(等于![]() )时我们需要降低

)时我们需要降低![]() 。然而,降低阈值电压会导致亚阈值电流(

。然而,降低阈值电压会导致亚阈值电流(![]() )指数级增加。这将在后续章节说明。

)指数级增加。这将在后续章节说明。

因此,存在一个矛盾。为降低动态功耗,我们需要降低![]() ;为保持性能我们需要降低

;为保持性能我们需要降低![]() ;但是会导致漏电流增加。就目前的工艺来说,这是一个合理的工艺,因为泄漏电流产生的静态功率远低于动态功率。但随着90nm技术的发展,我们已经到了静态功率和动态功率一样大的问题,我们需要更仔细地研究这一问题。

;但是会导致漏电流增加。就目前的工艺来说,这是一个合理的工艺,因为泄漏电流产生的静态功率远低于动态功率。但随着90nm技术的发展,我们已经到了静态功率和动态功率一样大的问题,我们需要更仔细地研究这一问题。

1.6 静态功率

一个CMOS门中有4个导致漏电流的源头:

- 亚阈值漏电流(

):工作在弱反型区的晶体管 漏极流向源极的电流。

):工作在弱反型区的晶体管 漏极流向源极的电流。 - 栅极漏电流(

):由于栅极氧化物隧穿和热载流子注入而直接从栅极通过氧化物流到衬底的电流。

):由于栅极氧化物隧穿和热载流子注入而直接从栅极通过氧化物流到衬底的电流。 - 栅诱导漏极泄漏电流(

):从漏极流到衬底的电流,由高

):从漏极流到衬底的电流,由高 引起的MOSFET漏极中的高场效应引起。

引起的MOSFET漏极中的高场效应引起。 - 反向偏置结电流(

):这是由少数载流子漂移和耗尽区中电子/空穴对的产生引起的。

):这是由少数载流子漂移和耗尽区中电子/空穴对的产生引起的。

当CMOS门没有完全关闭时,会发生亚阈值泄露。其值为:

W和L为晶体管尺寸,![]() 为热电压kT/q(室温下25.9mV)。参数n是设备制造工艺的函数,取值范围1~2.5。

为热电压kT/q(室温下25.9mV)。参数n是设备制造工艺的函数,取值范围1~2.5。

这个方程告诉我们,亚阈值泄露取决于![]() 和

和![]() 差值的e指数幂。因此,当我们为了限制动态功耗而缩减

差值的e指数幂。因此,当我们为了限制动态功耗而缩减![]() 和

和![]() 时,泄露功率将会指数级变差。

时,泄露功率将会指数级变差。

栅极泄露是栅氧化层隧穿电流的结果。在90 nm栅中,栅氧化层厚度(Tox)只有几个原子厚,这是如此之薄,以至于隧穿电流可以变得很大。在以前的技术节点中,漏电流一直以亚阈值泄漏为主。但从90 nm节点开始,栅漏电流可能是亚阈值泄漏的近三分之一。在某些情况下,65 nm节点可以等同于亚阈值泄漏。未来的节点将需要高k介质材料来控制栅漏。这似乎是减少栅漏的唯一有效方法。

亚阈值泄露电流随温度指数级增加。这使得设计低功率系统的问题极为复杂。即使在室温下的泄漏是可以接受的,在最坏的情况下,它也可能超过芯片的设计目标。

有几种使泄漏电流最小化的方法。

其中一个技术就是多阈值电压(Multi-VT):在性能需求的地方使用高阈值电压的单元,在必须满足时序要求的地方使用低阈值电压的单元。

第二种技术就是当逻辑块不需要工作时就对该逻辑块彻底断电。这种方法又称为功率门控。

这两种方法在后续章节会详细讨论,现在我们提一下其他三种技术。

VTCMOS

多阈值CMOS(Variable Threshold CMOS ,VTCMOS)是减少备用泄漏功率的另一种有效方式。通过对衬底施加一种反向偏置电压,可以减小(

-

)的差值。有效增加

。这种方法可以将备用泄漏减少多达三个数量级。然而,VTCMOS增加了单元库的复杂性,且需要两个额外的功率网络分别控制施加到阱的电压。不幸的是,反体偏置的有效性已经被证明随着缩放技术的发展而降低[2]。

Stack Effect

叠加效应,或者叫自偏压,当栈中有超过一个晶体管关闭,就会有助于减小亚阈值泄露。主要因为少量的亚阈值泄漏导致堆叠晶体管之间的中间节点浮离电源/接地轨。降低的体源极电势导致略微负的栅极-源极漏电压。因此,此方法将会减小(

-

)的差值,有效增加

,减小亚阈值泄露。两个晶体管堆叠的泄漏已被证明比单个晶体管的泄漏小一个数量级[3]。堆叠效应使得逻辑门的泄露高度依赖于输入端。对任何多输入电路,有一个最小泄露状态;在理论上,该状态恰好在停止时钟之前应用以最小化泄漏。在实践中,在大多数设计中应用这种状态是不可行的。

Long Channel Devices

从亚阈值电流的方程可以清楚地看出,使用非最小最小长度的通道将减少泄漏。不幸的是,长通道器件具有较低的动态电流,降低了性能。它们也更大,因此具有更大的栅极电容,这对动态功耗有不利影响,并进一步降低性能。除非长沟道器件的开关活动性低,否则总功耗可能不会降低。因此,在使用长通道设备时,必须考虑切换活动和性能目标。

1.7 本书目标

《低功耗方法学》的目的在于描述在Soc设计中管理动态和静态功率的最有效的新技术。我们描述了工程师在设计低功耗芯片时需要做出的决策,并提供了他们做出良好决策所需的信息。基于我们在实际芯片设计和一套流片技术示例的经验,我们提供了一组建议,并描述了低功耗设计中的常见陷阱。

设计复杂芯片的过程本身就非常复杂,涉及许多利益相关者和参与者:系统工程师、RTL设计师、IP设计师、物理实现工程师、验证工程师和库开发人员。这些截然不同的参与者之间的沟通总是一个挑战。每个小组都有自己的关注领域、优先事项,通常还有自己的语言。本书的一个目标是为这些小组提供一种讨论低功耗设计的通用语言,并对实现低功耗策略所涉及的问题有一个共同的理解。

当然,SoC设计团队必须做出的第一个低功耗决定是追求什么功耗策略——使用什么技术,何时何地以及芯片的哪一部分。这个基本问题推动了这本书的结构。

- 第一章(本章)给出并概述了低功耗设计的挑战和基本方法。

- 第二章讨论时钟门控的方法,多阈值电压设计,逻辑级功率降低技术,以及多电压设计。

- 第三章对多电压设计进行了更详细的描述,专注于架构和设计问题。

- 第四章概述功率门控。

- 第五章解决了RTL级功率门控的设计问题。

- 第六章提供了一个RTL级功率门控芯片设计的示例。

- 第七章讨论了功率门控的架构问题。

- 第八章功率门控IP设计的相关问题,包含一个示例。

- 第九章讨论了在动态电压和频率缩放的架构级和RTL级设计问题。

- 第十章讨论了电压和频率缩放的一些示例。

- 第十一章讨论了低功率设计的实现问题:综合、布局布线、时序分析以及功率分析。

- 第十二章讨论了功率门控的标准单元库和内存需求。

- 第十三章讨论了保持寄存器设计与存储器中的数据保持。

- 第十四章讨论了设计的功率开关网络。

- 附录A提供了关于休眠晶体管和功率开关网络的电路设计的一些附加信息。

- 附录B提供了本文中用到的UPF命令的详细描述。

在整本书中,我们将参考作者用于探索低功耗技术的几个低功耗技术示例项目。这些项目包括:SALT项目(Synopsys ARM低功耗技术示例)是一个90nm的设计,由ARM处理器和许多Synopsys外围设备和IO IP组成。该项目主要关注功率门控技术。处理器和USB OTG核心都是电源门控的

参考

1. Baron, M., “Energy-Efficient Performance at Intel”, Microprocessor Report, December 11, 2006.

2. Neau, C. and Roy, K. “Optimal Body Bias Selection for Leakage Improvement and Process Compensation over Different Technology Generations,” Proceedings of the ISLPED, 2003.

3. S. Narendra et al. “Scaling of Stack Effect and its Application for Leakage Reduction”, Int. Symp. on Low Power Electronics and Designs, pp.195-200, 2001.

至此,第一章翻译结束,有问题的地方请在评论区留言~