USB2.0电气层信号的表示及速率的识别过程

USB2.0电气层信号的表示及速率的识别过程

本文为个人学习中的笔记整理,可能存在一些错误或描述不准确的地方,欢迎大家指正,共同学习。

1.USB的一些基本概念

1.1 概念1:host和device

usb是一种主从结构的总线,主机叫做host,从机叫做device。host由host controlle和roothub两部分组成,host controlle主要负责数据处理,roothub则负责向上下游提供接口。 device主要分为两类,一种是func,如U盘,鼠标等;两一种是hub,主要用于扩展接口。下图是主从机的拓扑结构图:

如上图所示,一个host最多可以扩展出7层device,usb中所有的通信都是由host发起的,device只能响应host发起的请求,hub只能扩展出端口,并不能扩展出带宽,所有的device共享一个host的带宽。下图是windows设备管理器中usb描述:

1.2 概念2:上游设备 和 下游设备

上游设备(upstream facing transceivers) 和下游设备(downstream facing transceivers) 是一组相对的概念,如上总线拓扑图为例,roothub是hub1的上游设备,即hub1是roothub的下游设备;再如hub1是func的上游设备,即func是hub1的下游设备;上游设备一定是hub,而下游设备可能是hub,也可能是func。

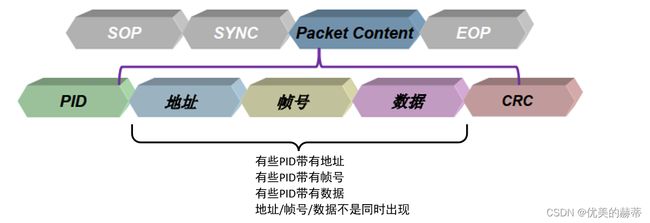

1.3 概念3:usb的数据交换的单位为packet

usb的速率协商数据包的交换均发生在一组上下游设备之间,数据交换的基本单位为packet,packet格式如下图所示:

2.usb的物理层信号

2.1usb信号位的表示

USB信号传输在物理层由4根线组成: VDD, D+, D-, GND,其中VDD和GND供电,信号的传输使用D+和D-表示,正是如下所述的各种物理层信号状态构成了可用于上下游设备通信的最小单位Packet ,此处有两个概念需要明确:

1. 通过**D+ D-** 在总线上处于不同的电压状态来表示数据状态,正是由一个个固定格式的电压状态组成**Packet** 用来传输数据。

2. 为了方便描述,协议给**D+D-** 每种不同的状态都起了一个别名,如**J状态** **K状态** **idle状态**,使用这些术语即可描述**packet** 的构成

2.1.1 在低速/全速模式下的信号表示

在低速/全速模式下**D+和D-**可以表示为4种状态:Differential “1”,Differential “0”,Single-ended 0 (SE0),Single-ended 1 (SE1),组成packet 的所有状态全部由这几种信号组成,如下图所示:

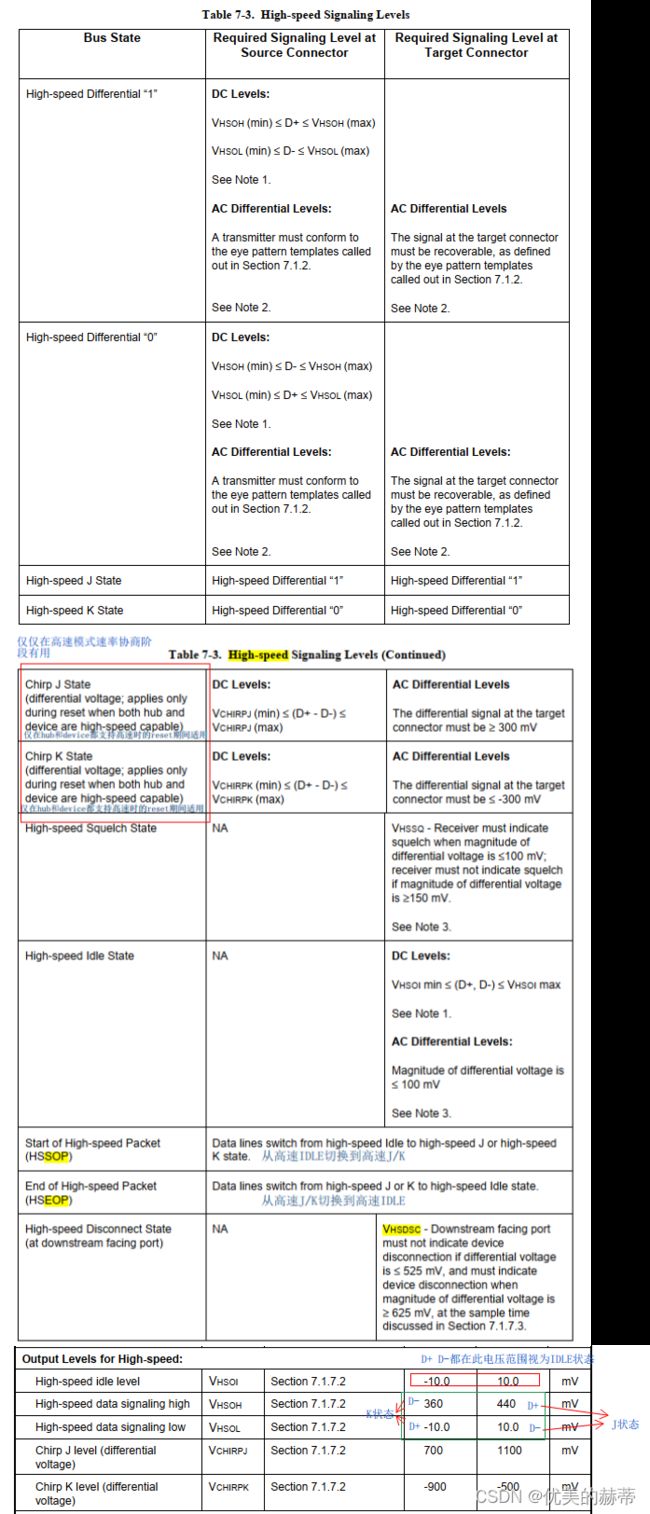

2.1.2 在高速模式中总线的信号表示形式如下图所示,

2.1.3 信号的位编码格式(NRZI)

问题的引入:USB总线通过D+和D-传输数据,并没有时钟线的概念,usb是如何来同步两边信号传输呢?我们需要了解一些编码方式,以便更好理解usb的速率协商和packet sync的意义。

2.1.3.1 RZ 编码(usb没使用)

RZ编码 全称是**Return-to-zero Code,也叫归零编码,**在该编码试工中,正电平代表逻辑1,负电平代码逻辑0,并且每次传输完一位数据,信号都会回到零电平。这样,在信号线上会产生3种电平:正电平、负电平、零电平,相应的信号图例如下:

从上图中可看出,每位数据传输中都有一个归零的过程,这样接收端只需要在归零后进行新的采样,这样就不需要单独的时钟信号。这虽然节省了信号线,但由于RZ编码信号中有大部分数据带宽被归零信号而浪费掉了。

2.1.3.2 NRZ 编码(usb没使用)

NRZ编码 全称是Non-return-to-zero Code,也叫不归零编码,这种编码方式很容易理解,逻辑高表示1,逻辑低表示1,信号中不再有归零的操作,但同时也失去了速率自同步的特性,响应的信号图如下所示:

2.1.3.3 NRZI编码(usb使用)

NRZI编码 全称是Non-Return-to-Zero Inverted Code,也叫反向不归零编码,NRZI编码与NRZ编码的区别就是NRZI编码用翻转来表示逻辑0,而信号保持不变来表示逻辑1,下图是NRZI编码与NRZ编码的对比图例:

由上述可知NZRI编码也不具备归零特性,故编码本身不具备编码自同步特性,在usb中,每个packet的最都存在一个同步域(SYNC),其值为00000001,在经过NRZI编码后,就是一串方波(在协议中描述为KJKJ…. 状态的切换),接收方通过同步域(SYNC)来计算发送方的频率,以便用这个频率来继续采样。到此为止,我们发现采用NZR编码也能实现同步域(SYNC)的概念,那么usb为什么要选择NZRI编码而非NZR编码呢?

这涉及到了NZRI编码的另外一个优势,由上图我们可以发现即使将NZRI编码翻转,传输的数据也不会被改变,这也是低速设备和全速设备在物理层能够完全兼容的根本原因,由前文所描述的usb的信号描述可知低速设备和全速设备的所有信号状态其实都是一组完全反向的信号,这是由于下游设备中的Rpu上拉电阻所决定的(在后面还会详细描述),usb的低速/全速设备正是通过控制Rpu的接通与断开来产生不同的状态来表示不同的数据。

NZRI编码的每次翻转(每个逻辑0)都是一次同步的过程,但也存在一种特殊的过程,比如总线中出现连续100个1,那么总线在很长一段时间内不会发生翻转,也就不会产生时钟同步,受两边节点时钟偏差的影响,可能会接到99个1,或101个1。为了避免这种情况,NZRI编码会在连续的6个1后面插入1个0来解决这种情况。

2.3usb设备的插入识别过程

2.3.1 usb的状态切换图

下图是usb的状态切换图,我在图中做了标注,可以先收悉一下这张图,后续描述便基于此图展开

2.3.2 usb的供电和速率识别

有以下两个概念需要明确:

- 供电:usb是通过上游设备向下游设备供电,即在下游设备插入上游设备后电源便被接通。

- 速率识别:速率识别分为两个阶段

- 设备在供电阶段首先会被识别为低速设备或全速设备,全速设备会兼容低速设备(全速设备和低速设备在数据传输信号表示上是一对反相的信号,得益于usb使用的NRZI编码信号反相不影响数据内容的特性,故低速设备和全速设备兼容)

- 全速设备的识别在低速设备/全速设备识别之后进行,设备只有首先被识别为全速设备,只有设备被识别为全速设备才会以全速设备的身份继续识别是否支持高速模式,若设备一开始被是被为低速模式,则后续不会继续识别是否支持高速模式,高速模式和低速模式/全速模式在底层信号上并不兼容。

2.3.2.1 低速设备/全速设备的识别

低速设备/全速设备的识别发生在上电过程中,即Attached–>Powered转换的过程,在usb设备进入Powered状态后就已经确定好速率,速率的确定依赖于Rpu上拉电阻。

下图是usb收发器内部电路示意图,在下游设备未插入的情况下,总线受Rpd下拉电阻的影响均处于被拉低的状态,将总线此时的状态称为Single-ended 0 (SE0),当设备插入后Rpu被供电,此时若Rpd上拉电阻连接D+,D+将被拉高,此时总线上的状态被称为Differential “1”;此时若Rpd上拉电阻连接D-,D-将被拉高,此时总线上的状态被称为Differential “0”。

低速设备的IDLE信号,J信号,都是使用Differential “0”来表示的,全速设备的IDLE信号,J信号,都是使用Differential “1”来表示的,将总线idle信号(J信号)维持超过2ms的状态称为connect信号,下游设备产生connect信号之后便进入Powered状态,此时设备支持的速率已经确定;即D+被拉高的时间超过2ms,便认为设备进入Powered模式且处于全速模式,若D-被拉高的时间超过2ms,便认为设备进入Powered模式且处于低速模式。

简单来说,即usb下游设备在插入usb上游设备后,上拉电阻Rpu将D+/D-持续拉高超过2ms(协议中将这一行为称为connect信号),设备便进入Powered状态(进入Powered状态,设备便已经被识别为低速设备/全速设备),下图是上述描述的简化图:

2.3.2.2 低速设备/全速设备的断开

针对上游设备的信号,上游设备检测到SE0信号维持超过2.5us的信号称为disconnect信号,上游低速/全速设备检测到disconnect信号便认为设备已经断开,下游设备故障或被拔出后,在失去了上拉电阻Rpu后,D+/D-会全部变为低(SE0信号),SE0信号维持超过2.5us,上游设备便认为下游低速/全速设备已经断开。

2.3.2.3高速设备的识别

高速设备的识别发生在Powered–>Default的过程,Powered–>Default的转化首先由上游设备发送一个reset信号(SE0信号维持超过10ms),之后的行为分为两种情况:

- 下游设备此时被识别为低速设备,在接受到上游设备发送的reset信号后直接进入Default状态,等待下一阶段的地址设置,此时不会去识别设备是否支持高速模式。

- 设备此时被识别为全速设备,此时由上游设备发送reset信号,之后双方协商是否支持高速模式,待速率协商完成后进入Default状态,等待进行地址设置,Default状态速率已经识别完成,但还没有进行地址分配,此时使用0地址进行下一步通信。只有进入到Default状态后设备才有了使用packet通信的能力。

注:下游设备处于Default状态之后的状态,上游设备也可通过发送reset信号重新使设备进入Default状态,然后按照usb状态切换图重新驱动设备。

下面描述高速设备的识别过程:

注:前提是usb已经被识别为全速设备且处于Powered状态。

- 下游设备在检测到上游设备发送的reset信号后,若下游设备支持高速模式则发出Chirp K 信号,上游设备在接受到Chirp K信号后,上游设备便知道下游设备支持高速模式,若上游设备也支持高速模式,就发出连续的Chirp K Chirp J信号,用来通知下游设备Hub也能支持高速模式。之后上游设备继续维持SE0信号直到10ms,断开Rpu电阻,便进入Default状态(高速模式),若速率协商阶段上下游设备中有任何一方不支持高速模式,便终止速率协商进入Default状态(全速模式)

2.3.2.4高速设备的断开

高速设备 断开,即Rs(45Ω)电阻也会断开,此时电气层信号会发生变化,高速设备基于此判断设备的断开。

2.4 packet的信号表示

在进入Default状态后,速率协商已经完成,之后设备便具有了使用packet通信的能力,packet是usb信息交换的最小单位。packet的格式如下图所示:

2.4.1 低速/全速设备的信号表示

SOP:Start Of Packet,Idle状态–>K状态。

SYNC: 3对KJ外加2个K。

EOP:End Of Packet,由数据的发送方发出EOP,数据发送方驱动D+、D-这两条线路,先设为SE0状态并维持2位时间,再设置为J状态并维持1位时间,最后D+、D-变为高阻状态,这时由线路的上下拉电阻使得总线进入Idle状态。

2.4.2 高速设备的信号表示

SOP:Idle状态–>K状态。

SYNC:KJKJKJKJ KJKJKJKJ KJKJKJKJ KJKJKJKK,即15对KJ,外加2个K。

EOP:略