【计算机组成与体系结构Ⅱ】MIPS指令系统(实验)

实验2:MIPS指令系统

一:实验目的

- 了解和熟悉指令级模拟器。

- 熟练掌握MIPSsim模拟器的操作和使用方法。

- 熟悉MIPS指令系统及其特点,加深对MIPS指令操作语义的理解。

- 熟悉MIPS体系结构。

二:实验要求

采用指令集和流水线操作级模拟器MIPSsim作为实验平台。

三:实验步骤

- 阅读MIPSsim模拟器的使用方法,了解MIPSsim的指令系统和汇编语言。

- 启动MIPSsim,用鼠标双击MIPSsim模拟器(64位).exe。

- 选择“配置”——“流水方式”选项,使模拟器工作在非流水方式下。

- 参照MIPSsim使用说明,熟悉MIPSsim模拟器的操作和使用方法。

- 以alltest.s为例,分析汇编代码并填写实验表格。

- 载入在本模拟器所在的文件夹下的“样例程序”文件夹中的样例程序alltest.s,然后分别以单步执行一条指令、执行多条指令、连续执行、设置断点等的方式运行程序,观察程序执行情况,观察CPU中寄存器和存储器的内容的变化,验证分析是否正确。

- 按照以上步骤运行并观察branch.s的模拟结果,对实验结果进行分析。

四:实验结果

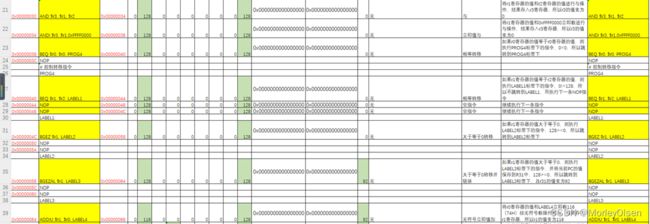

【1】alltest.s实验表格

如excel文件中的sheet1所示。

如excel文件中的sheet2所示。

【3】回答问题

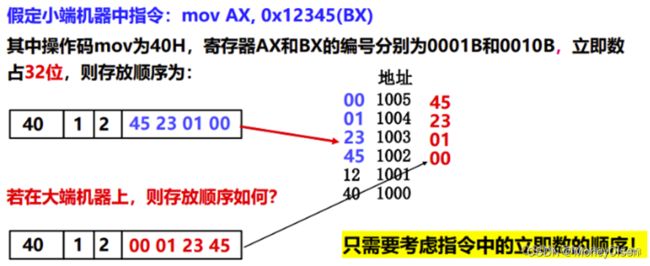

·模拟器中内存是小端存储还是大端存储,为什么?

小端存储。

以alltest.s中的【BUFFER:.word 300】为例。300 = 012C H,而在内存中可以发现,80H内存单元存储了2C,而81H内存单元存储了01,如下图所示。即数据的低位优先存储在低地址中,符合小端存储的特性。

而大端存储的特性是数据的高位优先存储在低地址中。两种存储方式的存放顺序如下图所示。

·模拟器中alltest的代码ADDIU $r8,$r0,DATA 为什么编译为ADDIU $r8,$r0,124,ADDIU $r8,$r0,BUFFER编译为ADDIU $r8,$r0,128?

DATA所存放的地址是0x0000 007C,7C H = 124。BUFFER所存放的地址是0x0000 0080,80H = 128。具体地址如下图所示。

ADDIU指令为无符号立即值加的指令,功能是rt ← rs + immediate。但是由于DATA和BUFFER是汇编程序中的标签,而不是具体的数值,所以编译器会将标签解析为它们在数据段.data中的地址,即124和128。

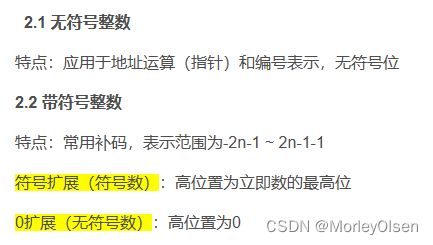

·执行到LB $r1,0($r8)时,R1的值为什么是-128,而LW $r1,0($r8)时为128,LBU $r1,0($r8)时为128?

LB指令为取字节的指令,且按有符号数操作,功能是rt ← memory[base + offset]。在LB $r1,0($r8)中,将r8寄存器中1个字节的内容以有符号数的形式取到r1寄存器中,即1000 0000 B,是一个负数,因此r1的值是-128。

LW指令为取字的指令,且按有符号数操作,功能是rt ← memory[base + offset]。在LW $r1,0($r8)中,将r8寄存器中1个字的内容以有符号数的形式取到r1寄存器中,由于64位计算机中1个字是8个字节,即0000 …… 1000 0000 B(共64位),是一个正数,因此r1的值是128。

LBU指令为取无符号字节的指令,功能是rt ← memory[base + offset]。在LBU $r1,0($r8)中,将r8寄存器中1个字节的内容以无符号数的形式取到r1寄存器中,即1000 0000 B,是一个正数,因此r1的值是128。

上述取指令的具体描述如下图所示。

·无符号数80H对应的十进制数为(D)

A.96 B.80 C.-128 D.128

80 H = 1000 0000 B

当80H表示无符号数时,所有位均是数位,即结果是2^7 = 128。

当80H表示有符号数时,最高位是符号位,其余位是数位。当符号位等于1时,表示负数;当符号位等于0时,表示正数。数位为000 0000,且表示负数,那么可以分析出它是表示范围内的最小负数而不是0,因为0的补码是唯一的。即结果是-128。

五:实验总结和分析

【1】空指令NOP

在本次实验的汇编程序中,有多行指令使用了空指令NOP。NOP在模拟器中编译后为SLL $r0,$r0,0。SLL指令是按立即值逻辑左移的指令,上述代码的含义为:将r0寄存器中的低32位进行逻辑左移,移动的位数是立即值0,结果按符号位扩展,然后放入r0寄存器中。执行该指令后,模拟器会保持r0寄存器中的值不变,即实际上是一个空操作,只是对PC的值进行了改变。

在本次实验中,NOP指令前面伴有分支指令,例如BEQ指令等。通过在分支指令后加入NOP指令,可以观察到执行分支指令时的PC变化情况,进而判断分支指令所执行的分支内容。具体而言,如果PC指向下一条NOP指令的地址,则表示分支内容为条件不成立后的结果;如果PC指向的不是下一条NOP指令的地址,则表示分支内容为条件成立后的结果。

【2】循环嵌套

在本次实验中,branch.s汇编程序采用了loop循环,其中包含一段BGTZ $r5,loop指令。BGTZ指令是大于0转移的指令,上述代码的含义为:如果r5寄存器中的值大于0,则继续loop循环,否则退出loop循环。这与高级语言中的循环结束的判断条件相似。

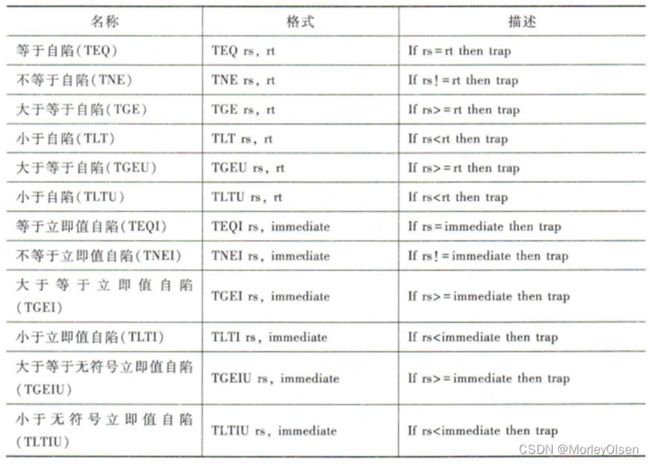

【3】自陷指令

在本实验中,alltest.s汇编程序在Label4处采用了TEQ $r0, $r0。TEQ指令是等于自陷的指令,上述代码的含义为:如果r0寄存器中的值等于r0寄存器中的值,则陷入陷阱中。在alltest.s中,如果执行到该指令,则表示程序运行完毕,应该结束程序。

其他自陷指令的具体描述如下图所示。

【4】跳转指令

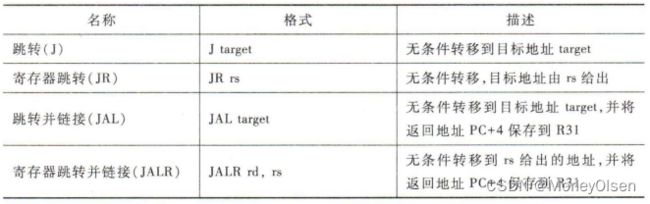

在本实验中,alltest.s汇编程序在Label3处采用了JALR $r3, $r1。JALR指令是寄存器跳转并链接的指令,上述代码的含义为:无条件转移到r1寄存器所给出的地址,并将返回地址PC+4保存到r31寄存器中。

其他跳转指令的具体描述如下图所示。

【5】分支指令

在本实验中,alltest.s汇编程序在多处位置采用了分支指令,用于判断转移。如果符合分支指令的条件,则跳转到某个程序标签处;否则执行下一条指令。

跳转指令的具体描述如下图所示。

【6】内存空间变化的情况

在本实验中,只有SW指令会触发内存空间的变化。SW指令是存字指令,其功能为memory[base + offset] ← rt。

其他存指令的具体描述如下图所示。

六:实验意见和建议

首先需要熟悉插件的使用,阅读附件的操作手册。其次需要熟悉MIPS指令的功能,以及汇编代码中所对应的寄存器。最后需要了解PC(程序计数器)的作用是指向下一条需要执行的指令,对指令的执行过程进行合理的分析。

七:附件

【1】alltest.s源文件

| # load和store指令 .text main: ADDIU $r8, $r0, DATA LB $r1, 0($r8) LW $r1, 0($r8) LBU $r1, 0($r8) ADDIU $r8, $r0, BUFFER SW $r1,0($r8) BEQ $r0, $r0, PROG2 NOP # 算术运算指令 PROG2: DADD $r3, $r1, $r2 DMULT $r1, $r2 BEQ $r0, $r0, PROG3 NOP # 逻辑运算指令 PROG3: AND $r3, $r1, $r2 ANDI $r3, $r1,0xFFFF0000 BEQ $r0, $r0, PROG4 NOP # 控制转移指令 PROG4: BEQ $r1,$r2,LABEL1 NOP NOP LABEL1: BGEZ $r1,LABEL2 NOP NOP LABEL2: BGEZAL $r1,LABEL3 NOP NOP LABEL3: ADDIU $r1, $r0, LABEL4 JALR $r3, $r1 NOP NOP LABEL4: TEQ $r0, $r0 NOP # 数据 .data .align 2 DATA: .word 128 BUFFER: .word 300 |

【2】branch.s源文件

| .text main: ADDI $r2,$r0,1024 ADD $r3,$r0,$r0 ADDI $r4,$r0,8 loop: LW $r1,0($r2) ADDI $r1,$r1,1 SW $r1,0($r2) ADDI $r3,$r3,4 SUB $r5,$r4,$r3 BGTZ $r5,loop ADD $r7,$r0,$r6 TEQ $r0,$r0 |