stm32RCC时钟模块

stmRCC时钟模块

文章目录

- stmRCC时钟模块

- **RCC** **主要作用—时钟部分**

- **RCC** **框图剖析—时钟部分**

-

- **系统时钟**

-

- **HSE** **高速外部时钟信号**

-

- **PLL** **时钟源**

- **PLL** **时钟** **PLLCLK**

- **系统时钟** **SYSCLK**

- **AHB** **总线时钟** **HCLK**

- **APB2** **总线时钟** **PCLK2**

- **APB1** **总线时钟** **PCLK1**

- 总结小表

- **设置系统时钟库函数**

- **其他时钟**

-

- A**、USB** 时钟

- B**、Cortex** 系统时钟

- C**、ADC** 时钟

- D**、RTC** 时钟、独立看门狗时钟

- E**、MCO** 时钟输出

- **配置系统时钟实验**

-

- 用LED灯验证是否时钟配置成功或者用逻辑分析仪

-

- main函数的验证

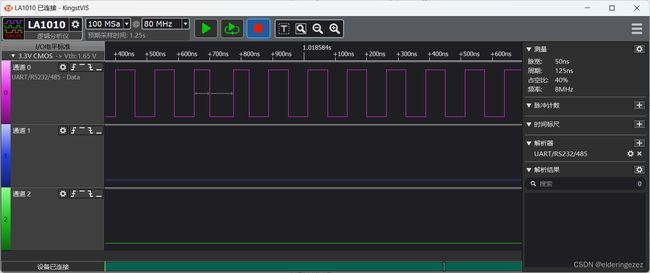

- 逻辑分析仪的验证

RCC 主要作用—时钟部分

设置系统时钟 SYSCLK、

设置 AHB 分频因子(决定 HCLK 等于多少)、

设置 APB2 分频因子(决定 PCLK2 等于多少)、

设置 APB1 分频因子(决定 PCLK1 等于多少)、

设置各个外设的分频因子;

控制 AHB、APB2 和 APB1 这三条总线时钟的开启、控制每个外设的时钟的开启。

对于 SYSCLK、HCLK、PCLK2、PCLK1 这四个时钟的配置一般是:PCLK2 = HCLK = SYSCLK=PLLCLK = 72M,PCLK1=HCLK/2 = 36M。这个时钟配置也是库函数的标准配置,我们用的最多的就是这个。

RCC 框图剖析—时钟部分

具体流程

1.时钟从OSC_IN 、OSC_OUT 进入---->2.变成PLL时钟源---->3.进入PLL时钟PLLCLK进行倍频操作---->4.变成系统时钟源---->5.进入AHB分频器---->6.APB1分频器---->7.APB2分频器

系统时钟

HSE 高速外部时钟信号

HSE 是高速的外部时钟信号,可以由有源晶振或者无源晶振提供,频率从 4-16MHZ 不等。

当使用有源晶振时,时钟从 OSC_IN 引脚进入,OSC_OUT 引脚悬空,当选用无源晶振时,时钟从OSC_IN 和 OSC_OUT 进入,并且要配谐振电容。

HSE 最常使用的就是 8M 的无源晶振。

当确定 PLL 时钟来源的时候,HSE 可以不分频或者 2 分频,这个由时钟配置寄存器 CFGR 的位 17:PLLXTPRE 设置,

我们设置为 HSE 不分频。

PLL 时钟源

PLL 时钟来源可以有两个,一个来自 HSE,另外一个是 HSI/2,**具体用哪个由时钟配置寄存器 CFGR 的位 16:PLLSRC 设置。**HSI 是内高速的时钟信号,频率为 8M,根据温度和环境的情况频率会有漂移,一般不作为 PLL 的时钟来源。

这里我们选 HSE作为 PLL 的时钟来源。

PLL 时钟 PLLCLK

通过设置 PLL 的倍频因子,可以对 PLL 的时钟来源进行倍频(增加多少倍的频率),倍频因子可以是:[2,3,4,5,6,7,8,9,10,11,12,13,14,15,16],具体设置成多少,由时钟配置寄存器 CFGR的位 21-18:PLLMUL[3:0] 设置。

72M 是 ST 官方推荐的稳定运行时钟,,最高为 128M。*

我们这里设置 PLL 时钟:PLLCLK = 8M 9 = 72M。

系统时钟 SYSCLK

系统时钟来源可以是:HSI、PLLCLK、HSE,具体的时钟配置寄存器 CFGR 的位 1-0:SW[1:0] 设置。

我们这里设置系统时钟:SYSCLK = PLLCLK = 72M。

AHB 总线时钟 HCLK

系统时钟 SYSCLK 经过 AHB 预分频器分频(降低多少倍数的频率)之后得到时钟叫 APB 总线时钟,即 HCLK,

分频因子可以是:[1,2,4,8,16,64,128,256,512],

具体的由时钟配置寄存器 CFGR 的位7-4 :HPRE[3:0] 设置。

APB2 总线时钟 PCLK2

APB2 总线时钟 PCLK2 由 HCLK 经过高速 APB2 预分频器得到,分频因子可以是:[1,2,4,8,16],

具体由时钟配置寄存器 CFGR 的位 13-11:PPRE2[2:0] 决定。

APB1 总线时钟 PCLK1

APB1 总线时钟 PCLK1 由 HCLK 经过低速 APB 预分频器得到,分频因子可以是:[1,2,4,8,16],

**具体的由时钟配置寄存器 CFGR 的位 10-8:PRRE1[2:0] 决定。**PCLK1 属于低速的总线时钟,最高为 36M。

总结小表

| 系统时钟(按调配顺序排列) | 作用 | 由GFGR控制端 |

|---|---|---|

| HSE 高速外部时钟信号 | 外部时钟源 | CFGR 的位 17:PLLXTPRE |

| PLL 时钟源 | 处理HSE后的时钟源 | CFGR 的位 16:PLLSRC |

| PLL 时钟 PLLCLK | 对 PLL 的时钟来源进行倍频 | CFGR的位 21-18:PLLMUL[3:0] |

| 系统时钟 SYSCLK | 处理HSI、PLLCLK、HSE后的时钟源 | CFGR 的位 1-0:SW[1:0] |

| AHB2 总线时钟 HCLK | 对PCLK2进行分频处理 | CFGR 的位 13-11:PPRE2[2:0] |

| APB1 总线时钟 PCLK1 | 对PCLK1进行分频处理 | CFGR 的位 10-8:PRRE1[2:0] |

设置系统时钟库函数

static void SetSysClockTo72(void)

2 {

3 __IO uint32_t StartUpCounter = 0, HSEStatus = 0;

4

5 // 1.使能 HSE,并等待 HSE 稳定

6 RCC->CR |= ((uint32_t)RCC_CR_HSEON);

7

8 // 等待 HSE 启动稳定,并做超时处理

9 do {

10 HSEStatus = RCC->CR & RCC_CR_HSERDY;

11 StartUpCounter++;

12 } while ((HSEStatus == 0)

13 &&(StartUpCounter !=HSE_STARTUP_TIMEOUT));//判断是否正常响应(不能超时)

14

15 if ((RCC->CR & RCC_CR_HSERDY) != RESET) {

16 HSEStatus = (uint32_t)0x01;

17 } else {

18 HSEStatus = (uint32_t)0x00;

19 }

20 // HSE 启动成功,则继续往下处理

21 if (HSEStatus == (uint32_t)0x01) {

22

23 //-----------------------------------------------------------

24 // 使能 FLASH 预存取缓冲区 */

25 FLASH->ACR |= FLASH_ACR_PRFTBE;

26

27 // SYSCLK 周期与闪存访问时间的比例设置,这里统一设置成 2

28 // 设置成 2 的时候,SYSCLK 低于 48M 也可以工作,如果设置成 0 或者 1 的时候,

29 // 如果配置的 SYSCLK 超出了范围的话,则会进入硬件错误,程序就死了

30 // 0:0 < SYSCLK <= 24M

31 // 1:24< SYSCLK <= 48M

32 // 2:48< SYSCLK <= 72M */

33 FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

34 FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

35 //------------------------------------------------------------

36

37 // 2.设置 AHB、APB2、APB1 预分频因子

38 // HCLK = SYSCLK

39 RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;

40 //PCLK2 = HCLK

41 RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;

42 //PCLK1 = HCLK/2

43 RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;

44

45 // 3. 设置 PLL 时钟来源,设置 PLL 倍频因子,PLLCLK = HSE * 9 = 72 MHz

46 RCC->CFGR &= (uint32_t)((uint32_t)

47 ~(RCC_CFGR_PLLSRC

48 | RCC_CFGR_PLLXTPRE

49 | RCC_CFGR_PLLMULL));

50 RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE

51 | RCC_CFGR_PLLMULL9);

52

53 // 4. 使能 PLL

54 RCC->CR |= RCC_CR_PLLON;

55

56 // 5.等待 PLL 稳定

57 while ((RCC->CR & RCC_CR_PLLRDY) == 0) {

58 }

59

60 // 6.选择 PLL 作为系统时钟来源

61 RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

62 RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

63

64 // 7.读取时钟切换状态位,确保 PLLCLK 被选为系统时钟

65 while ((RCC->CFGR&(uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08){

66 }

67 } else {// 如果 HSE 启动失败,用户可以在这里添加错误代码出来

68 }

69 }

其他时钟

通过对系统时钟设置的讲解,整个时钟树我们已经把握的有六七成,剩下的时钟部分我们讲解几

个重要的。

A**、USB** 时钟

USB 时钟是由 PLLCLK 经过 USB 预分频器得到,分频因子可以是:[1,1.5],具体的由时钟配置寄存器 CFGR 的位 22:USBPRE 配置。USB 的时钟最高是 48M,根据分频因子反推过来算,PLLCLK 只能是 48M 或者是 72M。一般我们设置 PLLCLK=72M,USBCLK=48M。USB 对时钟要求比较高,所以 PLLCLK 只能是由 HSE 倍频得到,不能使用 HSI 倍频。

B**、Cortex** 系统时钟

Cortex 系统时钟由 HCLK 8 分频得到,等于 9M,Cortex 系统时钟用来驱动内核的系统定时器 SysTick,SysTick 一般用于操作系统的时钟节拍,也可以用做普通的定时。

C**、ADC** 时钟

ADC 时钟由 PCLK2 经过 ADC 预分频器得到,分频因子可以是 [2,4,6,8],具体的由时钟配置寄存器 CFGR 的位 15-14:ADCPRE[1:0] 决定。很奇怪的是怎么没有 1 分频。ADC 时钟最高只能是 14M,如果采样周期设置成最短的 1.5 个周期的话,ADC 的转换时间可以达到最短的 1us。如果真要达到最短的转换时间 1us 的话,那 ADC 的时钟就得是 14M,反推 PCLK2 的时钟只能是:28M、56M、84M、112M,鉴于 PCLK2 最高是 72M,所以只能取 28M 和 56M。

D**、RTC** 时钟、独立看门狗时钟

RTC 时钟可由 HSE/128 分频得到,也可由低速外部时钟信号 LSE 提供,频率为32.768KHZ,也可由低速内部时钟信号 LSI 提供,具体选用哪个时钟由备份域控制寄存器 BDCR 的位 9-8:RTCSEL[1:0] 配置。独立看门狗的时钟由 LSI 提供,且只能是由 LSI 提供,LSI 是低速的内部时钟信号,频率为 30~60KHZ 直接不等,一般取40KHZ。

E**、MCO** 时钟输出

MCO 是 microcontroller clock output 的缩写,是微控制器时钟输出引脚,在 STM32 F1系列中由 PA8 复用所得,主要作用是可以对外提供时钟,相当于一个有源晶振。MCO的时钟来源可以是:PLLCLK/2、HSI、HSE、SYSCLK,具体选哪个由时钟配置寄存器CFGR 的位 26-24:MCO[2:0] 决定。除了对外提供时钟这个作用之外,我们还可以通过示波器监控 MCO 引脚的时钟输出来验证我们的系统时钟配置是否正确

配置系统时钟实验

#include "bsp_clkconfig.h"

#include "stm32f10x_rcc.h"

/*

* 使用HSE时,设置系统时钟的步骤

* 1、开启HSE ,并等待 HSE 稳定

* 2、设置 AHB、APB2、APB1的预分频因子

* 3、设置PLL的时钟来源,和PLL的倍频因子,设置各种频率主要就是在这里设置

* 4、开启PLL,并等待PLL稳定

* 5、把PLLCK切换为系统时钟SYSCLK

* 6、读取时钟切换状态位,确保PLLCLK被选为系统时钟

*/

/* 设置 系统时钟:SYSCLK, AHB总线时钟:HCLK, APB2总线时钟:PCLK2, APB1总线时钟:PCLK1

* PCLK2 = HCLK = SYSCLK

* PCLK1 = HCLK/2,最高只能是36M

* 参数说明:pllmul是PLL的倍频因子,在调用的时候可以是:RCC_PLLMul_x , x:[2,3,...16]

* 举例:User_SetSysClock(RCC_PLLMul_9); 则设置系统时钟为:8MHZ * 9 = 72MHZ

* User_SetSysClock(RCC_PLLMul_16); 则设置系统时钟为:8MHZ * 16 = 128MHZ,超频慎用

*

* HSE作为时钟来源,经过PLL倍频作为系统时钟,这是通常的做法

*/

void HSE_SetSysClock(uint32_t pllmul)

{

__IO uint32_t StartUpCounter = 0, HSEStartUpStatus = 0;

// 把RCC外设初始化成复位状态,这句是必须的

RCC_DeInit();

//使能HSE,开启外部晶振,野火开发板用的是8M

RCC_HSEConfig(RCC_HSE_ON);

// 等待 HSE 启动稳定

HSEStartUpStatus = RCC_WaitForHSEStartUp();

// 只有 HSE 稳定之后则继续往下执行

if (HSEStartUpStatus == SUCCESS)

{

//----------------------------------------------------------------------//

// 使能FLASH 预存取缓冲区

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

// SYSCLK周期与闪存访问时间的比例设置,这里统一设置成2

// 设置成2的时候,SYSCLK低于48M也可以工作,如果设置成0或者1的时候,

// 如果配置的SYSCLK超出了范围的话,则会进入硬件错误,程序就死了

// 0:0 < SYSCLK <= 24M

// 1:24< SYSCLK <= 48M

// 2:48< SYSCLK <= 72M

FLASH_SetLatency(FLASH_Latency_2);

//----------------------------------------------------------------------//

// AHB预分频因子设置为1分频,HCLK = SYSCLK

RCC_HCLKConfig(RCC_SYSCLK_Div1);

// APB2预分频因子设置为1分频,PCLK2 = HCLK

RCC_PCLK2Config(RCC_HCLK_Div1);

// APB1预分频因子设置为1分频,PCLK1 = HCLK/2

RCC_PCLK1Config(RCC_HCLK_Div2);

//-----------------设置各种频率主要就是在这里设置-------------------//

// 设置PLL时钟来源为HSE,设置PLL倍频因子

// PLLCLK = 8MHz * pllmul

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, pllmul);

//------------------------------------------------------------------//

// 开启PLL

RCC_PLLCmd(ENABLE);

// 等待 PLL稳定

while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET)

{

}

// 当PLL稳定之后,把PLL时钟切换为系统时钟SYSCLK

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

// 读取时钟切换状态位,确保PLLCLK被选为系统时钟

while (RCC_GetSYSCLKSource() != 0x08)

{

}

}

else

{ // 如果HSE开启失败,那么程序就会来到这里,用户可在这里添加出错的代码处理

// 当HSE开启失败或者故障的时候,单片机会自动把HSI设置为系统时钟,

// HSI是内部的高速时钟,8MHZ

while (1)

{

}

}

}

/*

* 使用HSI时,设置系统时钟的步骤

* 1、开启HSI ,并等待 HSI 稳定

* 2、设置 AHB、APB2、APB1的预分频因子

* 3、设置PLL的时钟来源,和PLL的倍频因子,设置各种频率主要就是在这里设置

* 4、开启PLL,并等待PLL稳定

* 5、把PLLCK切换为系统时钟SYSCLK

* 6、读取时钟切换状态位,确保PLLCLK被选为系统时钟

*/

/* 设置 系统时钟:SYSCLK, AHB总线时钟:HCLK, APB2总线时钟:PCLK2, APB1总线时钟:PCLK1

* PCLK2 = HCLK = SYSCLK

* PCLK1 = HCLK/2,最高只能是36M

* 参数说明:pllmul是PLL的倍频因子,在调用的时候可以是:RCC_PLLMul_x , x:[2,3,...16]

* 举例:HSI_SetSysClock(RCC_PLLMul_9); 则设置系统时钟为:4MHZ * 9 = 36MHZ

* HSI_SetSysClock(RCC_PLLMul_16); 则设置系统时钟为:4MHZ * 16 = 64MHZ

*

* HSI作为时钟来源,经过PLL倍频作为系统时钟,这是在HSE故障的时候才使用的方法

* HSI会因为温度等原因会有漂移,不稳定,一般不会用HSI作为时钟来源,除非是迫不得已的情况

* 如果HSI要作为PLL时钟的来源的话,必须二分频之后才可以,即HSI/2,而PLL倍频因子最大只能是16

* 所以当使用HSI的时候,SYSCLK最大只能是4M*16=64M

*/

void HSI_SetSysClock(uint32_t pllmul)

{

__IO uint32_t HSIStartUpStatus = 0;

// 把RCC外设初始化成复位状态,这句是必须的

RCC_DeInit();

//使能HSI

RCC_HSICmd(ENABLE);

// 等待 HSI稳定

while (RCC_GetFlagStatus(RCC_FLAG_HSIRDY) == RESET)

{

}

// 读取 HSI 就绪状态

HSIStartUpStatus = RCC->CR & RCC_CR_HSIRDY;

// 只有 HSI就绪之后则继续往下执行

if (HSIStartUpStatus == RCC_CR_HSIRDY)

{

//----------------------------------------------------------------------//

// 使能FLASH 预存取缓冲区

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

// SYSCLK周期与闪存访问时间的比例设置,这里统一设置成2

// 设置成2的时候,SYSCLK低于48M也可以工作,如果设置成0或者1的时候,

// 如果配置的SYSCLK超出了范围的话,则会进入硬件错误,程序就死了

// 0:0 < SYSCLK <= 24M

// 1:24< SYSCLK <= 48M

// 2:48< SYSCLK <= 72M

FLASH_SetLatency(FLASH_Latency_2);

//----------------------------------------------------------------------//

// AHB预分频因子设置为1分频,HCLK = SYSCLK

RCC_HCLKConfig(RCC_SYSCLK_Div1);

// APB2预分频因子设置为1分频,PCLK2 = HCLK

RCC_PCLK2Config(RCC_HCLK_Div1);

// APB1预分频因子设置为2分频,PCLK1 = HCLK/2

RCC_PCLK1Config(RCC_HCLK_Div2);

//-----------------设置各种频率主要就是在这里设置-------------------//

// 设置PLL时钟来源为HSI,设置PLL倍频因子

// PLLCLK = 4MHz * pllmul

RCC_PLLConfig(RCC_PLLSource_HSI_Div2, pllmul);

//------------------------------------------------------------------//

// 开启PLL

RCC_PLLCmd(ENABLE);

// 等待 PLL稳定

while (RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET)

{

}

// 当PLL稳定之后,把PLL时钟切换为系统时钟SYSCLK

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

// 读取时钟切换状态位,确保PLLCLK被选为系统时钟

while (RCC_GetSYSCLKSource() != 0x08)

{

}

}

else

{ // 如果HSI开启失败,那么程序就会来到这里,用户可在这里添加出错的代码处理

// 当HSE开启失败或者故障的时候,单片机会自动把HSI设置为系统时钟,

// HSI是内部的高速时钟,8MHZ

while (1)

{

}

}

}

用LED灯验证是否时钟配置成功或者用逻辑分析仪

main函数的验证

/******************************************************************************

* 实验平台:野火 F103-指南者 STM32 开发板

******************************************************************************

*/

/*

* 配置MCO引脚:PA8 对外提供时钟,最高频率不能超过IO口的翻转频率50MHZ

* MCO 时钟来源可以是:PLLCLK/2 ,HSI,HSE,SYSCLK

*/

#include "stm32f10x.h"

#include "bsp_led.h"

#include "bsp_clkconfig.h"

#include "bsp_mcooutput.h"

// 软件延时函数,使用不同的系统时钟,延时不一样

void Delay(__IO u32 nCount);

/**

* @brief 主函数

* @param 无

* @retval 无

*/

int main(void)

{

// 程序来到main函数之前,启动文件:statup_stm32f10x_hd.s已经调用

// SystemInit()函数把系统时钟初始化成72MHZ

// SystemInit()在system_stm32f10x.c中定义

// 如果用户想修改系统时钟,可自行编写程序修改

// 重新设置系统时钟,这时候可以选择使用HSE还是HSI

// 使用HSE时,SYSCLK = 8M * RCC_PLLMul_x, x:[2,3,...16],最高是128M

//HSE_SetSysClock(RCC_PLLMul_9);

// 使用HSI时,SYSCLK = 4M * RCC_PLLMul_x, x:[2,3,...16],最高是64MH

HSI_SetSysClock(RCC_PLLMul_2);//现在系统时钟频率为8MHZ

// MCO 引脚初始化

MCO_GPIO_Config();

// 设置MCO引脚输出时钟,用示波器即可在PA8测量到输出的时钟信号,

// 我们可以把PLLCLK/2作为MCO引脚的时钟来检测系统时钟是否配置准确

// MCO引脚输出可以是HSE,HSI,PLLCLK/2,SYSCLK

//RCC_MCOConfig(RCC_MCO_HSE);

//RCC_MCOConfig(RCC_MCO_HSI);

//RCC_MCOConfig(RCC_MCO_PLLCLK_Div2);

RCC_MCOConfig(RCC_MCO_SYSCLK);

// LED 端口初始化

LED_GPIO_Config();

while (1)

{

LED1( ON ); // 亮

Delay(0x0FFFFF);

LED1( OFF ); // 灭

Delay(0x0FFFFF);

}

}

// 软件延时函数,使用不同的系统时钟,延时不一样

void Delay(__IO uint32_t nCount)

{

for(; nCount != 0; nCount--);

}

/*********************************************END OF FILE**********************/