如何从零开始设计一颗芯片?

戳蓝字“CSDN云计算”关注我们哦!

来源:陌上风骑驴看IC 作者:陌上风骑驴

来源:陌上风骑驴看IC 作者:陌上风骑驴

在各方助力下,集成电路成了时代热点,有大量文章在写芯片设计之复杂之困难,老驴打算从EDA 使用角度捋一遍芯片设计流程。在老驴画出第一副图之后,发现熟知的只有数字电路部分的一小段,对系统、软件及上层应用完全无知,只能归类为Others。

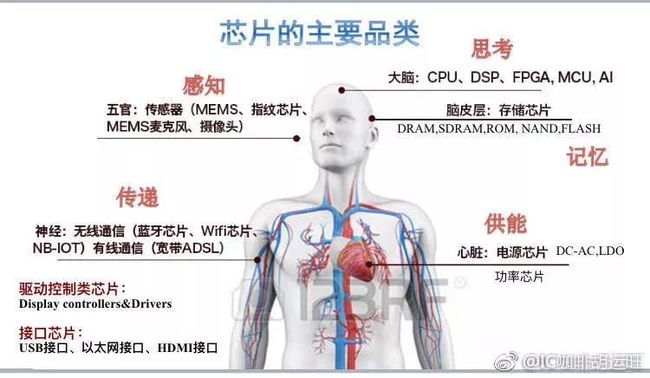

于消费者而言,一个可以使用的系统,有数字集成电路部分、模拟集成电路部分、系统软件及上层应用部分。关于各个部分的功能,借用IC 咖啡胡总的精品图可以一目了然。

外部世界是一个模拟世界,故所有需要与外部世界接口的部分都需要模拟集成电路,模拟集成电路将采集到的外部信息转化成0/1 交给数字集成电路运算处理,再将数字集成电路运算处理完的信号转化成模拟信号输出;而这一切的运算过程都是在系统软件的号令跟监控下完成的,故曰:芯片是骨架,系统软件是灵魂。

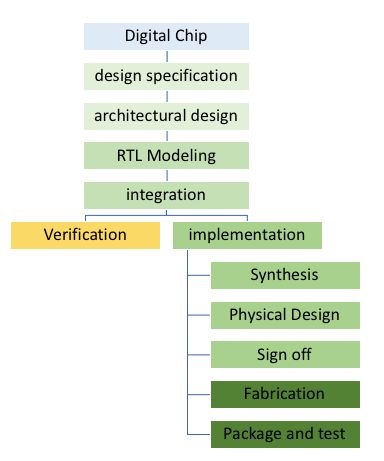

数字集成电路设计实现流程是个相当漫长的过程,拿手机基带芯片为例,对于3G, 4G, 5G, 工程师最初见到的是无数页的协议文档。

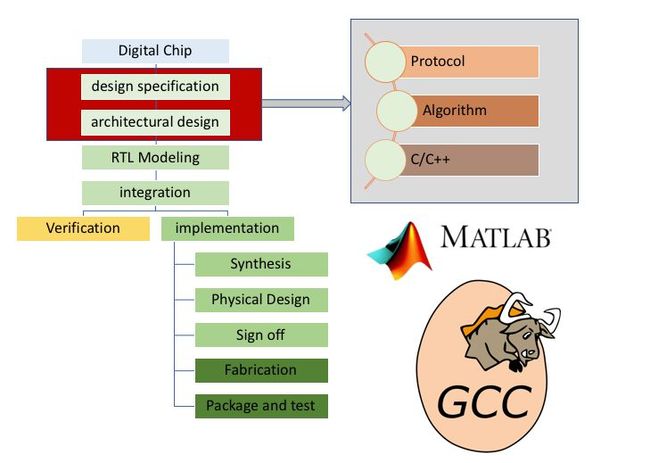

- 架构师要根据协议来确定:协议的哪些部分可以用软件实现,哪些部分需要用硬件实现;

- 算法工程师要深入研读协议的每一部分,并选定实现所用算法;

- 芯片设计工程师,需要将算法工程师选定的算法,描述成RTL;

- 芯片验证工程师,需要根据算法工程师选定的算法设计测试向量,对RTL 做功能、效能验证;

- 数字实现工程师,需要根据算法工程师和设计工程师设定的目标PPA 将RTL 揉搓成GDS;

- 芯片生产由于太过复杂,完全交由代工厂完成,封装亦是;

- 对于测试,大部分公司都是租借第三方测试基台由自己的测试工程师完成,只有少部分土豪公司才会有自己的测试基台。

一颗芯片,性能的60% 取决于架构师,在国内好的架构师不超过三位数,极好的架构师不超过两位数,架构师是芯片灵魂的缔造者,是食物链的最顶端,是牛逼闪闪的存在,就驴浅显认知,除了office 似乎没有EDA 工具用于架构设计;

架构敲定了之后,大量的算法工程师跟上,对于协议规定的每个点,都要选择适当的算法,用C/C++ 做精确模拟仿真,要确保功能、精度、效率、吞吐量等指标,Matlab 跟GCC 应该是他们使用最多的工具。

设计工程师根据算法工程师经过反复模拟仿真选择的算法,将抽象描述或定点C 转换成RTL, 在设计过程中需要反复仿真、综合,以确定设计功能的正确性,跟设计能达到的PPA. 除了RTL, 设计工程师还需要根据设计目标编写SDC 和power intent, 并做对应的质量检查。设计工程师需要使用大量EDA 工具:

- 编辑器:VIM, emac;

- Lint : RTL 质量检查,Spyglass, Jasper;

- CDC: SDC 质量检查,Spyglass, Conformal, GCA;

- CPF/1801: power intent 质量检查,CLP;

- Power: RTL 级功耗分析,Joules, PA;

- 仿真器:C, S, M 三家都有各自的仿真工具;

- 综合:Genus, DC;

老驴以为,从集成开始,由脑力劳作进入体力劳作,对比盖房子,就是从设计师到泥瓦工。集成工程师,要把芯片所用的所有模块相互连接起来,指导思想是架构工程师确定的,各个IP 如何连接是各IP 的owner 确定的,集成工程师只要保证不多连、不少连、不乱连即可,据说当前也没有什么有效的集成工具,常用到的是emac。

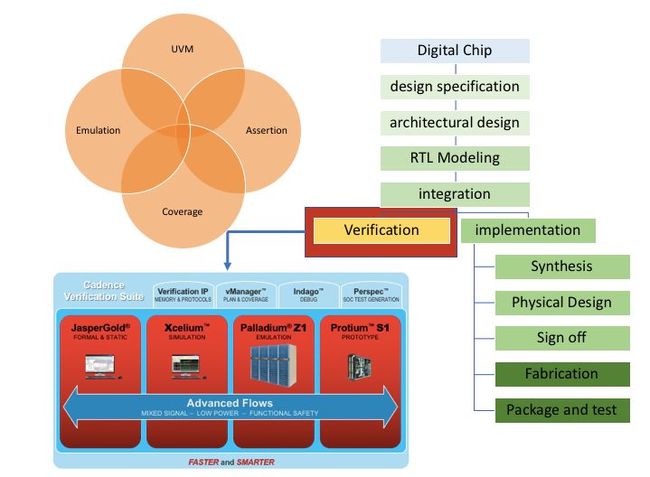

验证

接着捋,实际项目中验证跟综合从RTL coding 开始就会交叉进行,反复迭代。

验证在数字芯片设计中占很大比例,近些年在设计复杂度的推动下验证方法学跟验证手段在不断更新,从OVM 到UVM, 从Dynamic verification 到Static verification, 从FPGA 到Emulator,所有革新目的可概括为:快速、完备、易调试。验证涉及到许多方面,验证工程师一方面要对相关协议算法有足够了解,根据架构、算法工程师设定的目标设计仿真向量;

另一方面要对设计本身足够了解,以提高验证效率,缩短验证时间。验证工程师需要掌握许多技术,需要使用许多工具。

- 语言:各种脚本语言之外,C/C++, SystemVerilog, Verilog;

- 协议:各种接口协议,各种通信协议,各种总线协议;

- 工具:动态仿真工具,静态仿真工具,FPGA, Emulator;

数字验证领域,依旧是C, S, M 三家几乎全霸,老驴已不做验证多年,对S, M 两家验证相关工具除了VCS, Verdi, Modelsim 其他几乎无知,此处拿C 家验证全套为例。

- Static Verification: Jasper Gold 是C 家新近推出的静态验证工具,驴所理解的静态验证是基于断言的验证方法学,所谓静态即不需要输入测试激励,验证过程是纯数学行为。

- Dynamic Verification: Xcelium 是C 家的动态验证工具,驴所理解的动态验证是基于UVM 的验证方法学,通过输入测试激励,监控仿真结果,分析覆盖率完成功能验证。

- Emulator: 硬件仿真加速器,粗暴理解:有debug 功能的集成了丰富接口的巨型可编程阵列;特点:超高速验证、支持系统软件调试。帕拉丁是C 家在验证领域的明星产品,是行业翘楚,据说常有钦差莅临硅厂在帕拉丁前驻足良久,赏其外形之美,赞其功能之强。

- Verification IP: 验证需要各种验证模型,各种IP, 各种总线,各种高速接口。

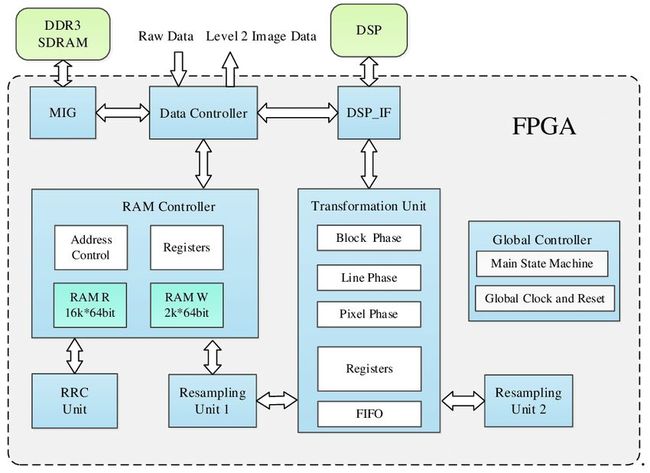

FPGA 的一大应用是验证,故提一嘴。在世上曾经有两家牛逼闪闪的FPGA 公司,一家是Altera 另一家是Xilinx, 后来Altera 像Mentor 一样找了个大爷把自己卖了。FPGA 内除了可编程逻辑之外,通常还会集成各种IP, 如CPU, DSP, DDR controller 等。

每家FPGA 都有各种配置,根据集成的IP, 可编程逻辑的规模,可达到的速度,价格相差极大。相对于ASIC, FPGA 也有一套对应的EDA 工具,用于综合、布局布线、烧录、调试。如:Synplify, Quartus。

国内现状:Static Verification, Dynamic Verification, Emulator 几乎空白;国内有一些FPGA 公司,在中低端领域已经做得非常不错,但是高端领域几乎空白。任重而道远,不矫饰,脚踏实地干!

实现

接着上面说的我们继续捋数字芯片设计实现流程,今天进入实现阶段,对于这一段驴只熟悉其中的综合、形式验证、低功耗验证、RTL 功耗分析、STA, 其他部分都是一知半解,故无深究,只捋流程。

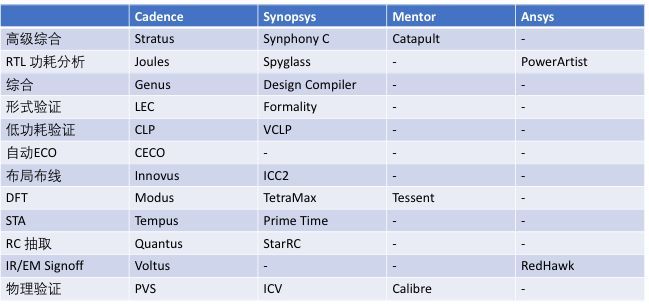

整个实现阶段,可以概括成玩EDA 工具及基于EDA 工具的方法学,EDA 工具无疑是实现阶段的主导,一颗芯片做得好不好,在实现阶段之前基本取决于工程师的能力强不强,而在实现阶段之后基本取决于EDA 工具玩得好不好。整个设计实现流程,涉及到许多工具,此处列出四家主要参与者,空白部分不代表没有,只代表驴不知。

数字电路实现流程,从大方向上可以分成两部分:优化跟验证。优化,会更改逻辑描述方式,会更改逻辑结构,会插入新逻辑,这所有的动作都存在引入错误的风险,故需要验证工具予以监控;

验证,要确保逻辑优化过程不改变逻辑功能,要确保时序满足既定目标需求,要确保无物理规则违规,要确保信号完整性,这所有的验证都有一套对应的通过规则,但凡有某一项不达标,就不能拿去生产制造。

高级综合:所谓的高级综合就是将C/ C++/ System C描述的设计意图,“翻译”成用Verilog/ System Verilog 描述的RTL, 多应用于运算逻辑主导的设计,除了三巨头,市面上有许多小公司在这一个点上也做得不错。

综合:在实现流程中,就背后算法而言,综合一定是最难最复杂的。综合首先将Verilog/ System Verilog/ VHDL 描述的逻辑转化成由Gtech 描述的逻辑,再对Gtech 逻辑做优化,优化后再将Gtech 描述映射到对应工艺库。

其中优化过程涉及到多个方面,近年来EDA 工具的发展方向基本可以概括为:容量,速度,相关性。容量:指可处理的设计规模;速度:指EDA 工具的优化速度;相关性:指跟布局布线之间的相关性。主流工具:Genus, Design Compiler. 在这一点上,几乎再难有后起之秀,除非有朝一日,整个数字电路的设计方法学发生颠覆性的革新。

DFT: 插入压缩解压缩逻辑,插入scan chain, 插入Mbist, 插入Lbist, 插入Boundary Scan, 插入OCC, 插入Test Point, 生成ATPG pattern, 故障诊断,DFT 工程师像老中医插入、观察、诊断。当今市面上DFT 工程师紧缺,贵!主流工具:Tessenst, Modus, TetraMax.

ECO: 但凡有新的东西引入,就可能引入bug, 早期发现bug 可以重新走一遍实现流程,如果在后期发现bug 重走一遍流程的代价太大,通常的做法就是ECO. 对于简单的bug 修复手工ECO 就可以,但是对于复杂的bug 修复,手工ECO 有心无力,故需要有EDA 工具来完成相应的工作。当前世面上最好用的自动ECO 工具非Conformal ECO 莫属。最近也有一些startup 做对应的点工具,整个思路跟CECO 类似,但是没有自己的综合工具优化ECO 后的补丁,就很难得到一个好的结果。

布局布线:在进入纳米时代之前,布局布线并没那么复杂,从90nm 开始到如今的3nm,布局布线的复杂度呈指数增长,从floorplan 到placement 到CTS 到Routing 每一步涉及到的算法在近年都做了颠覆性的革新,以Innovus 的问世为起点,布局布线进入到了一个新纪元。

在AI 的浪潮下C 跟S 都一头扎了进去,要做世上最智能的布局布线工具,也许有朝一日可以像跟小度对话一样:

- 硅农:Innovus 请解析A 文件,按设定目标做个功耗最优的结果;

- Innovus: 已读取目标文件,根据设计数据分析,本设计大概需要250G 内存,在5小时内完成,请选择任务完成后是否自动进入后续程序......

RTL 功耗分析:这一步可以放在实现端做也可以放在实现之前做。分析过程相对简单:读入RTL, SDC, 仿真激励,通过计算分析平均功耗跟瞬时功耗,找出设计中的“功耗缺陷”,指导Designer 进行功耗优化。主流工具有:Joules, Spyglass, PowerArtist.

形式验证:在整个实现流程中,形式验证充当逻辑功能等效性的监察官,任何一步优化结束后都需要过形式验证这一关,以确保在优化过程中,逻辑功能未被改变。主流工具:LEC, Formality. 随着设计规模的暴增跟优化技术的飞速发展,形式验证的难度逐渐增加,占用的时间逐渐增多,SmartLEC 是针对复杂设计的先行者。

低功耗验证:针对低功耗设计,低功耗验证要验证CPF/ UPF/ 1801 的语法语义跟描述意图,要验证低功耗单元未多插,未漏插,未乱插,要验证电源跟地的链接符合设计意图,要验证电特性的完整性。主流工具:CLP。

STA: Timing signoff, STA 看似庞杂,其实并不复杂,相比于优化过程要简单得多,抛开Timing ECO, STA 所有的动作都只是计算而不是求解,不恰当的比方:STA 就好比幼儿园的算术题,加数跟被加数都在那里,只要求个和即可;而优化过程是求最优解或近似最优解的过程,要难得多。

近年来STA EDA 工具主要在几个方向着力:如何模拟制造过程的随机工艺偏差,如何处理超大规模设计,如何模拟新工艺结点电特性对时序的影响。

Power Signoff: 验证设计的电源网络是否足够强悍,分析,发现,修正:IR-drop 跟EM。主流工具:Voltus, RedHawk。

物理验证: 验证所有的管子、过孔、走线是否满足Foundry 制定的规则,是个体力活,有点像盖好房子之后的垃圾清理,主流工具:Calibre, PVS, ICV。

整个数字实现流程中涉及到诸多工具,三巨头在领跑,后面基本没有跟随者,偶尔有某个点工具做得好的后起之秀,大多都会被三巨头吃了,这也算是行业套路。就市值看,三巨头加起来来也不及互联网公司一条腿粗,然而在整个芯片设计实现过程中却不可或缺,吾国要强大芯片产业,必须要在EDA 这一块加大投入,方能离脱离被掐着脖子走更进一步。

![]()

福利

扫描添加小编微信,备注“姓名+公司职位”,加入【云计算学习交流群】,和志同道合的朋友们共同打卡学习!

![]()

推荐阅读:

如何高效地准备技术面试?

漫画:有趣的“帽子问题”

我为什么放弃了 Chrome?

5天破10亿的哪吒,为啥这么火,Python来分析

通俗易懂:图解10大CNN网络架构

互联网公司上演反腐风暴;GitHub CEO 对断供表示无能为力;程序员面试锦集| 开发者周刊

在其他国家被揭穿骗子又盯上非洲? 这几个骗子公司可把非洲人民坑苦了……