芯片功耗从28mW降到0.28mW

景芯SoC训练营培训项目,低功耗设计前,功耗为27.9mW。

低功耗设计后,功耗为0.285mW,功耗降低98.9%!

(一)低功耗lowper debug

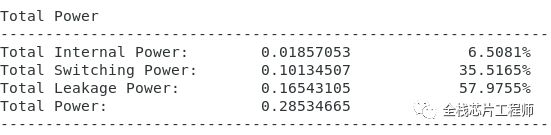

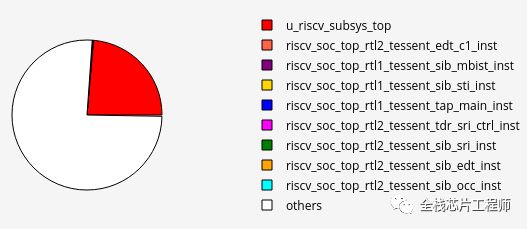

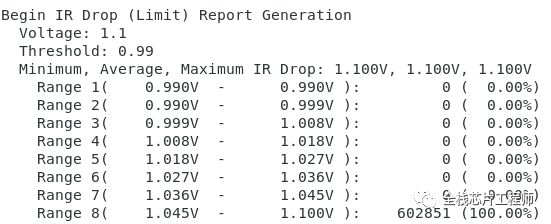

今天给大家介绍下景芯SoC训练营低功耗debug,景芯SoC在低功耗P&R完成后,低功耗静态功耗为2.107mW,下图可以看到Internal Power为1.8mW占据了87%的比例,那么这1.8mW的功耗来自哪里?

小编首先联想到的就是时钟IO,进一步查看报告,可以看到就是IO的Internal功耗。

Summary也可以看到这个时钟IO PAD功耗占据了1.838mW。

按照低功耗的架构设计,U_CRYSTAL_OSC0的时钟应该关闭,且该IO PAD应该关电,那么Voltus功耗分析怎么做呢?欢迎加入景芯SoC全流程设计训练营实战吧。

修改后的功耗为:

如果不采用低功耗设计,芯片待机状态下功耗将是27.9mW,嵌入式设备时不可接受的,景芯SoC的全流程学员会深有体会,低功耗设计的重要性可见一斑!

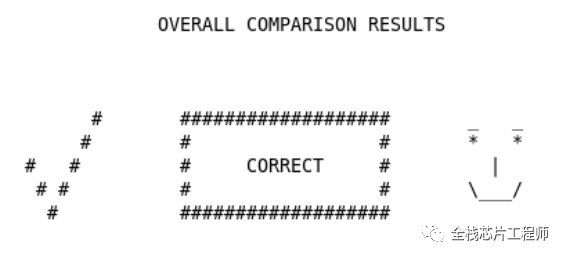

(二)低功耗low power确认

选中一个power gating domain(shut down domain)的STD CELL作为report对象,domain关电后,report_instance_power,发现其功耗确实为0。是不是很好玩?

景芯微SoC团队业务

景芯SoC芯片全流程设计训练营,让每个人都能设计一款SoC/MCU芯片!

-

提供全网最全流程的实际芯片项目培训

-

提供SoC、MCU、ISP、CIS等芯片设计服务

-

提供芯片设计、验证、DFT设计服务

-

提供后端设计服务,工艺包括7nm、12nm、28nm、40nm、55nm、65nm、90nm、110nm、180nm等,提供投片渠道

-

提供高校、企业定制化芯片设计培训及就业推荐与就业指导

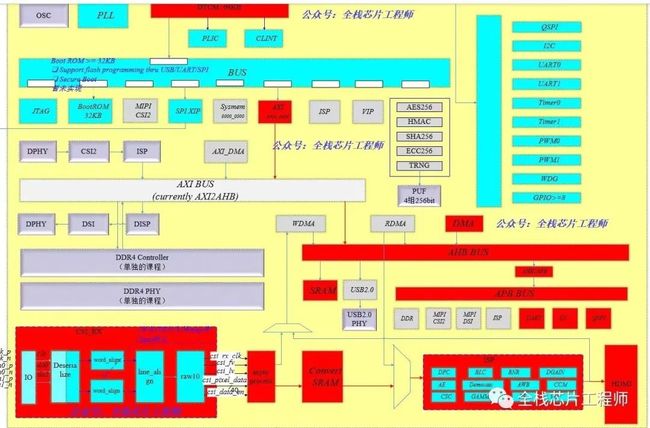

【全网唯一】景芯SoC是一款用于【芯片全流程设计培训】的低功耗ISP图像处理SoC,采用低功耗RISC-V处理器,内置ITCM SRAM、DTCM SRAM,集成包括MIPI、ISP、USB、QSPI、UART、I2C、GPIO、以太网MAC控制器等IP,采用SMIC40工艺设计流片。

(一)SoC前端课程,您将学会

-

高速接口的Verilog设计实现

-

图像算法及Verilog设计实现

-

MIPI通信协议的Verilog实现

-

Lint、CDC检查及UVM验证

-

后仿真

仅前端一门课程内容就抵得上其他培训机构的5-6门课程。

(二)SoC中端课程,您将学会

-

DFT设计(芯片级)

-

Synthesis逻辑综合(芯片级)

-

低功耗UPF设计、CLP技术

-

formal验证等技术

仅中端一门课程内容就抵得上其他培训机构的4-5门课程。

(三)SoC后端课程,您将学会

-

布局布线(低功耗FF flow)

-

StarRC/QRC

-

STA/Tempus

-

功耗分析

-

DRC/LVS设计

仅后端一门课程内容就抵得上其他培训机构的3-4门课程。

课程提供服务器供大家实践!带你从算法、前端、DFT到后端全流程参与SoC项目设计。更多内容,请联系号主报名!

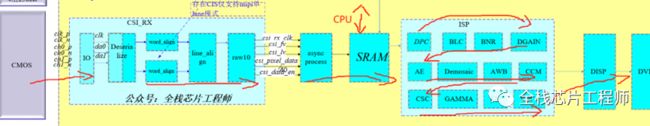

图像处理的数据通路:

景芯SoC的CRG设计:

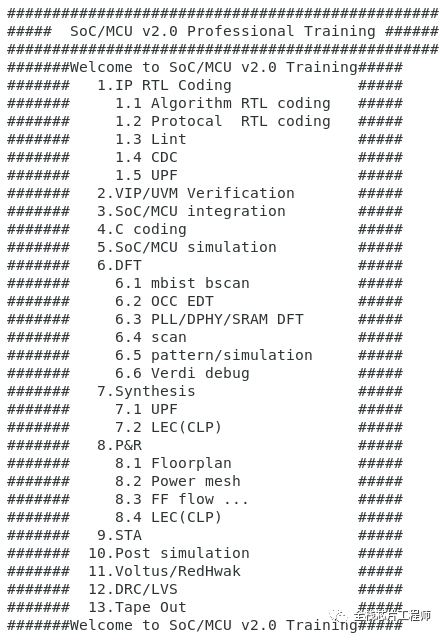

一键式完成C代码编译、仿真、综合、DFT插入、形式验证、布局布线、寄生参数抽取、STA分析、DRC/LVS、后仿真、形式验证、功耗分析等全流程。升级后的芯片设计工程V2.0 flow如下:

SoC一键式执行flow

MIPI DPHY+CSI2解码

数字电路中经典设计:多条通信数据Lane Merging设计实现

数字电路中经典设计:多条通信数据Lane Distribution实现

UPF低功耗设计

全芯片UPF低功耗设计(含DFT设计)

景芯SoC训练营培训项目,低功耗设计前,功耗为27.9mW。

低功耗设计后,功耗为0.285mW,功耗降低98.9%!

芯片的版图设计V1.0

芯片的版图设计V2.0

低功耗设计的DRC/LVS,芯片顶层的LVS实践价值极高,具有挑战性!业界独一无二的经验分享。

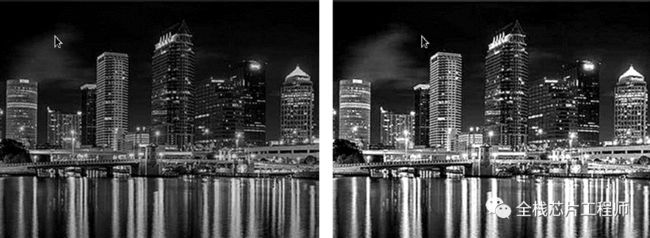

ISP图像处理

-

dpc - 坏点校正

-

blc - 黑电平校正

-

bnr - 拜耳降噪

-

dgain - 数字增益

-

demosaic - 去马赛克

-

wb - 白平衡增益

-

ccm - 色彩校正矩阵

-

csc - 色彩空间转换 (基于整数优化的RGB2YUV转换公式)

-

gamma - Gamma校正 (对亮度基于查表的Gamma校正)

-

ee - 边缘增强

-

stat_ae - 自动曝光统计

-

stat_awb - 自动白平衡统计

CNN图像识别

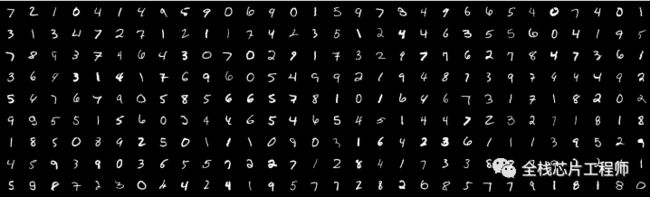

支持手写数字的AI识别:

仿真结果:仿真识别上图7、2、1、0、4、1、4、9

前端设计目录

中端设计目录

后端设计目录

欢迎加入【全栈芯片工程师】知识星球交流技术,从算法、前端、DFT到后端的全流程设计交流。点击下方图片,加入知识星球!

欢迎加入CIS+ISP技术交流群,先加我微信,我拉你进群!

欢迎加入MCU芯片设计交流群,先加我微信,我拉你进群!